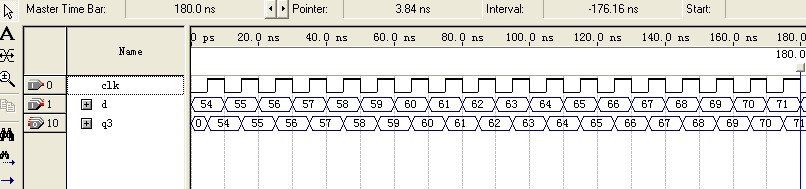

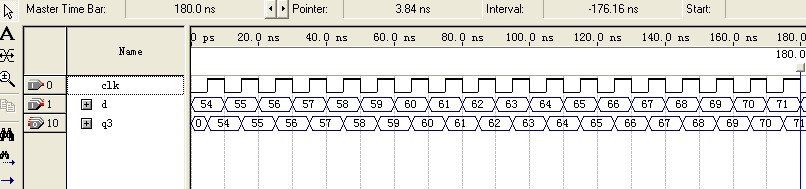

阻塞與非阻塞賦值 首先從名字上理解,阻塞賦值即賦值沒完成,后邊的語句將無法執行,非阻塞剛好與其相反,即賦值完不完成并不阻礙后續程序的執行,所以我們常說非阻塞賦值的對象并未立馬得到新值,如果從時序來看

2017-09-19 18:32:43 11967

11967 來源:《Verilog數字系統設計(夏宇聞)》 阻塞和非阻塞賦值的語言結構是Verilog 語言中最難理解概念之一。甚至有些很有經驗的Verilog 設計工程師也不能完全正確地理解:何時使用非阻塞

2021-08-17 16:18:17 6000

6000 當元素的數據類型和數組界限(最低和最高的可能的數組索引)相匹配時,能夠將一個完整數組賦值給另一個數組。如果是這樣,在賦值符后指定數組的標識符

2022-07-12 10:55:25 2759

2759 Verilog 2005 版本支持使用省略位寬的方式賦值,’b,’d,’h,采用省略位寬的方式可以向左主動補齊,如果省略了進制符合b/d/h/o,則默認是十進制。

2022-11-23 14:14:51 4427

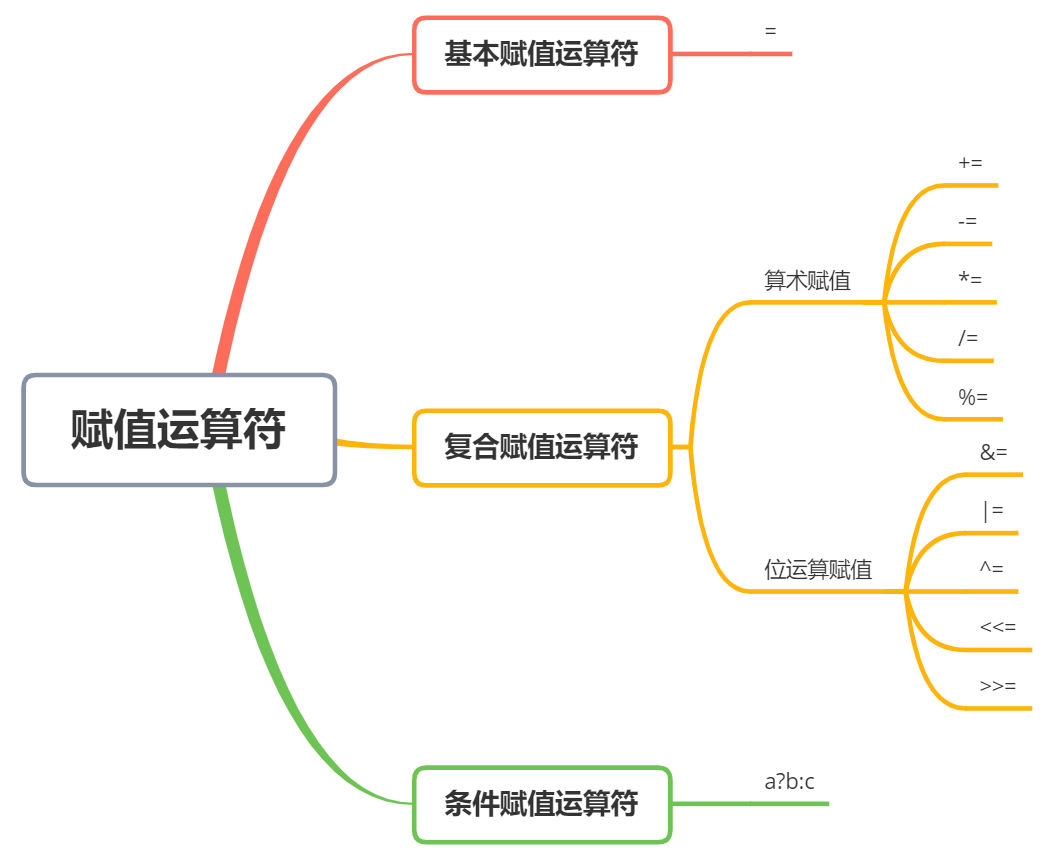

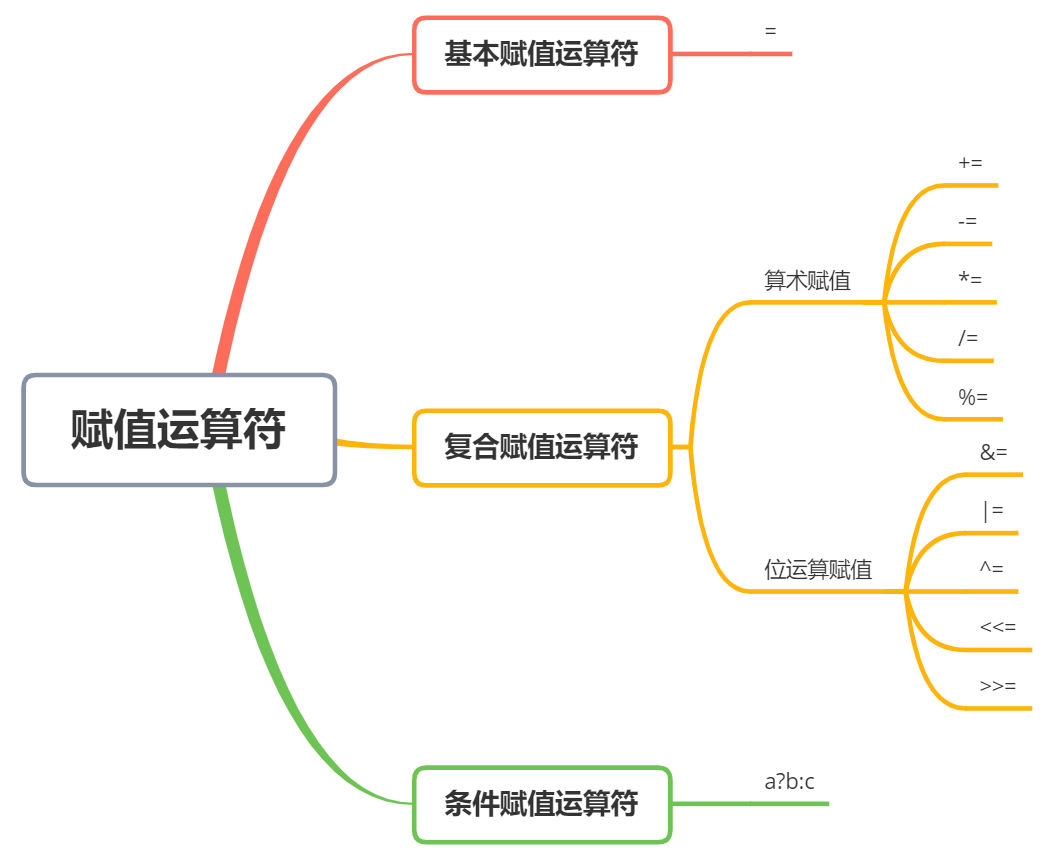

4427 今天我們來學習C語言中的運算符和表達符。C語言中賦值運算有”=“、”+=“、”-=“、”/=“和”%=“等。用賦值運算符將運算對象連接而成的表達式稱為賦值表達式。

2023-02-02 09:35:03 225

225 在C語言中,賦值運算符用于將一個值賦給變量。

2023-08-18 16:38:13 837

837

S7-200中的字符串賦值指令,包括其語法、使用方法、注意事項等,以幫助讀者更好地理解和應用該指令。 首先,我們來了解一下S7-200中字符串的表示方式。字符串是由多個字符組成的序列,用于存儲和處理文本信息。在S7-200的程序中,字符串通常使用字元(CH

2023-12-08 14:44:06 778

778 在使用電氣CAD軟件進行強電平面設計的過程中,有些時候會需要給圖紙中的設備添加型號規格,那么具體該如何操作呢?對此浩辰電氣CAD軟件中提供了設備賦值功能,可以快速對設備進行賦值。接下來的CAD學習

2021-02-07 15:57:36

參數,文字顏色將被修改為黑色,可以修改參數值,結果圖中該類圖塊被賦予同一種型號規格。可以應用“符號派生”對同一圖塊區分表示,這樣采用“設備批量賦值”時就可以分別賦值了。以上就是小編給大家分享的浩辰

2021-06-29 16:47:45

1,在阻塞賦值中,說是前邊賦值阻塞后邊賦值,但是看波形明明是同時變化,這是為什么?2,在if ,else if, else語句中說是順序執行,是時鐘跳一個周期判斷一次嗎,還是同時判斷,如果是同時判斷為什么說是順序執行?3,是組合邏輯中用=,非組合邏輯中用

2019-05-29 01:09:27

如題所示,如何給端口整體賦值;例如51中端口賦值方式,P2 = 0x55,謝謝!

2023-08-24 06:05:18

如題所示,如何給端口整體賦值;例如51中端口賦值方式,P2 = 0x55,謝謝!

2024-01-16 07:10:14

要發送出去數據就是給SBUF賦值,可是賦值之后接收到的和賦給SBUF的值不一樣呢?接收到的數據為什么不是5呢?? 用LabVIEW讀取的也是這樣 85 85 85。不知道是哪里出錯了,期待前輩賜教

2016-08-14 22:46:06

我編寫了個FIFO,我想把它輸出的數賦給9個信號量,如何按順序賦值,求幫忙

2015-03-17 13:52:07

`在書上看到的,講解阻塞型賦值語句時,舉了一個例子說的是,本想采用觸發器的方式,設計一個延時來使得dreg的輸出比areg慢3個時鐘節拍,但是結果是dreg的輸出只比areg慢一個時鐘節拍輸出程序

2017-09-20 15:10:01

Verilog中阻塞賦值與非阻塞賦值的區別

2020-12-30 06:22:29

[table][tr][td] Verilog中有兩種為變量賦值的方法。一種叫做連續賦值,另一種叫做過程賦值。過程賦值又分為阻塞賦值和非阻塞賦值。阻塞性賦值使用“=”為變量賦值,在賦值結束前不可以進行其他操作,在賦值結束之后繼續后面的操作。這個過程就好像阻斷了程序的運行。非阻塞賦值使用“

2018-07-03 03:06:04

剛才看c語言手冊有這么一個函數strcpy()字符串復制我有這么一個想法定義一個數組:unsigned char dd[]={"123456\r\n"};定義一個指針

2019-04-03 00:31:53

`阻塞與非阻塞賦值首先從名字上理解,阻塞賦值即賦值沒完成,后邊的語句將無法執行,非阻塞剛好與其相反,即賦值完不完成并不阻礙后續程序的執行,所以我們常說非阻塞賦值的對象并未立馬得到新值,如果從時序來看

2017-04-05 09:53:11

i沒賦值,怎么有詳細數字賦值到“i0;b--)for(a=130;a>0;a--);}

2014-08-27 19:01:23

(14): error C129: missing ';' before '.'但是我將‘.’去掉或者改成‘_’就沒有問題了,我就是不明白c語言里面結構變量賦值不是.嗎,那為什么會這樣typedef

2012-10-13 23:26:11

labview怎么實現調用SQL server存儲過程 并完成賦值 求幫助~求思路~

2018-01-09 17:17:08

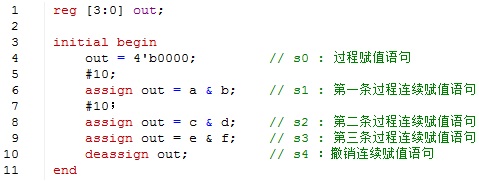

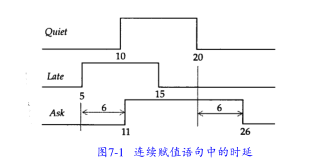

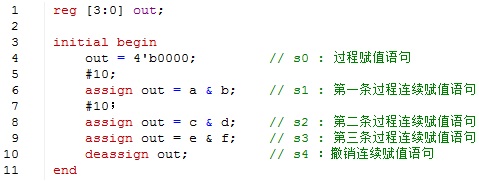

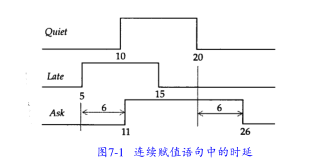

Verilog HDL 中的數據流建模形式一般用連續賦值語句來實現。Verilog HDL 中有兩種形式的賦值方式:連續賦值和過程賦值。其中過程賦值用于順序行為建模,而組合邏輯電路的行為最好

2018-09-21 09:24:45

過程性賦值是在 initial 語句或 always 語句內的賦值,它只能對寄存器數據類型的變量賦值。過程性賦值如下兩類:? 阻塞性過程賦值:賦值在其后所有語句執行前執行,即在下一語句執行前該賦值

2018-09-26 09:16:55

阻塞賦值與非阻塞賦值原理分析實驗目的:掌握阻塞賦值與非阻塞賦值的區別實驗平臺:無實驗原理:阻塞賦值,操作符為“=”,“阻塞”是指在進程語句(initial和always)中,當前的賦值語句阻斷了其后

2016-12-25 01:51:24

本文和設計代碼由FPGA愛好者小梅哥編寫,未經作者許可,本文僅允許網絡論壇復制轉載,且轉載時請標明原作者。阻塞賦值,操作符為“=”,“阻塞”是指在進程語句(initial和always)中,當前

2020-02-24 20:09:13

阻塞與非阻塞作者:小黑同學一、 概述1、阻塞賦值對應的電路往往與觸發沿沒有關系,只與電平的變化有關系。阻塞賦值符號“=”。2、非阻塞賦值對應的電路結構往往與邊沿觸發有關系,只有在觸發沿時才有可能發生賦值的情況。非阻塞賦值符號“

2020-04-24 14:49:45

立即學習>>夢翼師兄FPGA培訓(純視頻),手把手帶你入門FPGA寫在前面的話開發過程中,我們用的最多的恐怕就是賦值語句了,我們常用的賦值方式有兩種:阻塞賦值和非阻塞賦值。夢翼師兄剛開始

2019-12-22 14:21:37

查找范例,很多例程里面的for循環不賦值的,感覺好奇怪,自己寫的不賦值會出錯,求大神解答

2016-05-23 00:54:31

正常的數組賦值,可是jtag仿真出來,賦值都亂了,圖順序截的,本來打算menu0[0]給menu1[0]的,以此類推,,,求解釋

2019-09-05 03:37:58

本文舉例說明了信號賦值與變量賦值的區別。

2021-04-30 06:44:35

@ (posedge GlobalClk)RegC = RegB;由于過程性賦值立即發生,即沒有任何時延,所以根據首先執行哪一條always語句,RegC取不同的值,這就產生了競爭。書上說使用非阻塞性賦值可以避免產生競爭狀態,為什么??求助...

2013-11-07 10:16:34

編譯時會根據語句出現的位置自動識別是邏輯運算還是賦值運算。

在“表達式”(expression)中,\"<=\"作為邏輯比較運算符;在“語句”(statement

2023-08-08 09:32:07

在單片機C語言中如何對變量的某一位進行操作或賦值?

2011-04-07 14:47:47

順序賦值的方式實現流水燈&nb

2022-03-02 07:14:54

如上圖所示,我在While循環外面對兩個一維數組的第一個元素分別賦值“溫度”和“電壓”,但是當程序走到While循環里面的時候,用探針探測出兩個數組是空數組,求高手解答:怎樣給數組賦初值呢?

2015-06-30 08:59:05

用的verilog hdl。always塊里的每個賦值語句間,有延遲的嗎?如果有延遲是多大?還有非阻塞語句是并行執行的還是說在always塊結束的時候再一句一句執行?之前一直搞C語言,到這里好多東西不習慣

2018-05-15 15:07:37

Verilog HDL語言中存在兩種賦值語言:● 非阻塞型賦值語句● 阻塞型賦值語句1. 非阻塞型語句以賦值操作符“

2015-03-22 10:23:44

)的設計第二篇cVerilogcHDL語言綜合原理篇第6章綜合的基本知識6.1綜合的概念6.2數值集合與數據類型6.3儲值單元的綜合原則第7章VerilogHDL語句的綜合7.1連續賦值

2012-02-07 10:25:05

;abcde";如上面代碼,text1.a[5]處報錯 error C141: syntax error near '{',如果說數組不能整體賦值,那該怎么賦值,一個個的來嗎?為什么下面text1.b[5]可以整體賦值不會報錯?

2014-12-05 16:37:28

給C語言指針賦值有何作用?給普通變量的賦值與給指針變量的賦值有何不同?

2022-02-25 06:10:48

附件為表格控件某一行值得獲取和某一單元格賦值的案例,請查閱

2018-08-02 08:41:26

如何給特征(notify) 賦值,用的例子是 gatts_server_service_table,運行后 特征和描述都沒有值,請問下怎么賦值,看別人做的,特征值還一直在變化

2023-03-03 07:27:50

介紹了PCM采編器的工作原理,并且詳細解釋了采用VerilogHDL語言用EDA的方法設計及實現PCM采編器的仿真及下栽過程,說明了PCM采編器在通信及廣播領域的廣泛用途。

2012-04-01 15:07:42 74

74 VerilogHDL 中,有兩種過程賦值方式,即阻塞賦值(blocking)和非阻塞賦值(nonblocking)。阻塞賦值執行時,RHS(righthandstatement)估值與更新LHS(lefthandstatement)值一次執行完成,計算完畢,立即更新。

2012-05-23 09:55:51 1192

1192

基于PCM采編器的VerilogHDL語言設計

2017-10-31 09:30:46 39

39 設計背景: 阻塞 (=)和非阻塞(=)一直是在我們FPGA中討論的問題,資深的學者都是討論的是賦值應該發生在上升下降沿還是在哪里,我們在仿真中看的可能是上升下降是準確的,但是在時間電路中這就

2018-05-31 11:40:14 6357

6357

本文檔的主要內容詳細介紹的是PHP中傳值賦值和引用賦值的詳細資料詳解。

2019-03-06 17:04:32 5

5 本文檔的主要內容詳細介紹的是FPGA視頻教程之Verilog中兩種不同的賦值語句的資料說明免費下載。

2019-03-27 10:55:59 6

6 本文檔的主要內容詳細介紹的是單片機交通燈的程序不能重新賦值。

2019-06-05 17:52:00 2

2 對于VerilogHDL語言中,經常在always模塊中,面臨兩種賦值方式:阻塞賦值和非阻塞賦值。對于初學者,往往非常迷惑這兩種賦值方式的用法,本章節主要介紹這兩種文章的用法。其實,有時候概念稍微不清楚,Bug就會找到我們,下面一文掃清阻塞賦值和非阻塞賦值所有的障礙。

2020-01-30 17:41:00 20976

20976 1、阻塞賦值操作符用等號(即 = )表示。“阻塞”是指在進程語句(initial和always)中,當前的賦值語句阻斷了其后的語句,也就是說后面的語句必須等到當前的賦值語句執行完畢才能執行。而且阻塞賦值可以看成是一步完成的,即:計算等號右邊的值并同時賦給左邊變量。

2020-04-25 08:00:00 0

0 阻塞賦值對應的電路往往與觸發沿沒有關系,只與輸入電平的變化有關系。非阻塞賦值對應的電路結構往往與觸發沿有關系,只有在觸發沿時才有可能發生賦值的情況。

2020-06-17 11:57:41 10885

10885

對于VerilogHDL語言中,經常在always模塊中,面臨兩種賦值方式:阻塞賦值和非阻塞賦值。對于初學者,往往非常迷惑這兩種賦值方式的用法,本章節主要介紹這兩種文章的用法。其實,有時候概念稍微

2020-11-19 15:48:56 927

927 連續賦值語句總是處于激活狀態。只要任意一個操作數發生變化,表達式就會被立即重新計算,并且將結果賦給等號左邊的線網。

2020-11-26 10:04:44 3101

3101

本文檔的主要內容詳細介紹的是如何使用Verilog語言實現持續賦值方式定義的2選1多路選擇器程序免費下載。

2020-10-28 16:54:27 14

14 本文檔的主要內容詳細介紹的是如何使用Verilog語言實現持續賦值方式定義的2選1多路選擇器程序免費下載。

2020-10-28 16:54:27 6

6 數據流模型化 本章講述Verilog HDL語言中連續賦值的特征。連續賦值用于數據流行為建模;相反,過程賦值用于(下章的主題)順序行為建模。組合邏輯電路的行為最好使用連續賦值語句建模。 7.1 連續

2021-03-05 15:38:21 3646

3646

@(posedge clk) begin q1 = d; q2 = q1; q3 = q2; end endmodule 上述代碼綜合后能得到所期望的邏輯電路嗎? 答案是否定的, 根據阻塞賦值語句的執行過程可以得到執行后的結果是

2021-05-08 14:47:05 1799

1799

阻塞賦值和非阻塞賦值的可綜合性 Blocking Assignment阻塞賦值和NonBlocking Assignment非阻塞賦值,原本是軟件進程管理的術語。由于Verilog團隊是從C語言發展

2021-05-12 09:45:09 2398

2398

賦值 當一個值被指定,變量的當前值被通過表達式指定的新的值代替。此表達式也能夠包含函數標識符,其被語句激活,然后返回相應的值(返回值)。 如下圖所示,在賦值符右邊的表達式被求值,且得到的值作為結果

2021-05-24 14:56:15 4647

4647

關于51單片機的IO接口的地址與賦值大小理解前提了解關于51單片機的IO接口的地址與賦值大小理解其他單片機定義前提了解提示:我們需要回顧C語言的類型定義,如int aa=1;代碼編譯運行的時候計算機

2021-11-17 10:51:02 14

14 / C51中的復合賦值運算符 /變量 復合運算符 表達式先把變量與后邊的表達式進行某種運算,然后將運算的結果賦給前面的變量。+= 加法賦值 ?+ 減法賦值*= 乘法賦值 /= 除法賦值%= 取模賦值

2021-11-24 10:36:02 0

0 從仿真結果可以看出:在順序塊中,15ns的時候,l1被賦值為8’h2,在25ns的時候,l2被賦值為8’h8;而在并行塊中,10ns的時候,k2被賦值為8’h8,在15ns的時候,k1被賦值為8’h2。可以很容易明白順序塊和并行塊的特性。

2022-03-15 11:51:15 1510

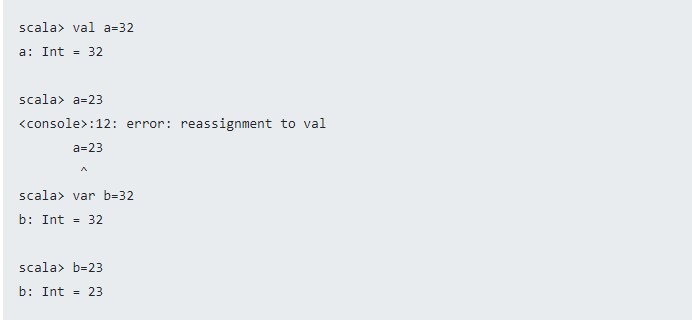

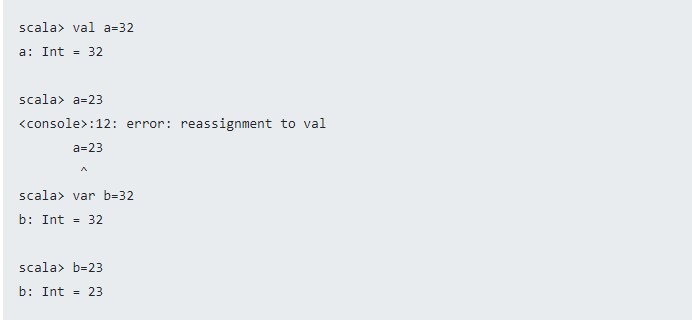

1510 我們是為電路對象所代表的值進行賦值,而不是改變電路對象本身(把電路對象指向另一個對象,想一想是否和上面Array的賦值有點兒類似),因而這里我們是不能用=(=在Scala中本身也是一個方法,是改變

2022-07-28 18:16:47 1213

1213

如例6.1所述,在多個“Always” 進程中使用阻塞賦值。程序塊“Always”在時鐘的正邊緣觸發,綜合器推斷時序邏輯。如前所述,所有阻塞賦值都在活動隊列中進行計算和更新。讀者請參閱之前分享的分層事件隊列一文。

2022-09-06 09:44:02 3306

3306 方法:實際應用里,通常需要在上電復位過程中對變量進行初始化,如果數組個數少時,直接賦初始值即可,但是數組個數多時,可以用循環實現賦值,通常的循環語句有FOR和WHILE。(注意變量的賦值方式)

2022-09-23 14:20:08 7953

7953 當我們聲明一個類時還沒有分配內存,只有在實例化(new())時才會分配內存。這個時候對象句柄指向被分配的內存,下面是對象句柄賦值的示例。

2022-11-21 10:35:50 645

645 SystemVerilog有三種在可綜合RTL級別表示組合邏輯的方法:連續賦值語句、always程序塊和函數。接下來幾篇文章將探討每種編碼風格,并推薦最佳實踐編碼風格。

2022-12-07 15:31:47 940

940 今天我們把數組復習一下,數組是怎么用的,怎么對它進行定義,怎么對它進行賦值,然后把字符型數組大概說一下。

2022-12-08 08:55:19 592

592 阻塞賦值操作符用等號(即 = )表示。“阻塞”是指在進程語句(initial和always)中,當前的賦值語句阻斷了其后的語句,也就是說后面的語句必須等到當前的賦值語句執行完畢才能執行。

2022-12-19 16:49:28 4607

4607 使用邏輯門和連續賦值對電路建模,是相對詳細的描述硬件的方法。使用過程塊可以從更高層次的角度描述一個系統,稱作行為級建模(behavirol modeling)。

2023-02-08 09:41:33 362

362 python類主體沒有任何內容,只有pass語句,稱為空類。

## 1.2 obj.attr屬性賦值

通過obj.attr=value進行類和實例屬性賦值。

2023-02-21 10:30:52 655

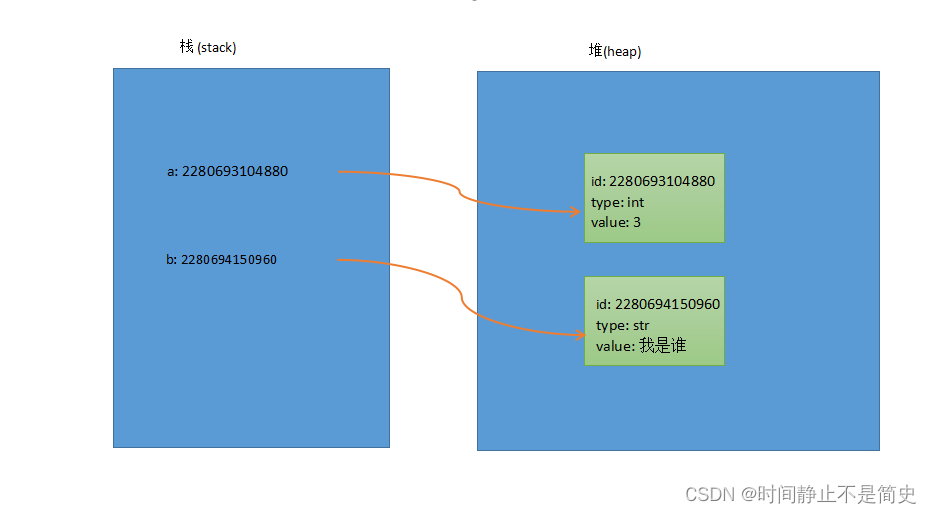

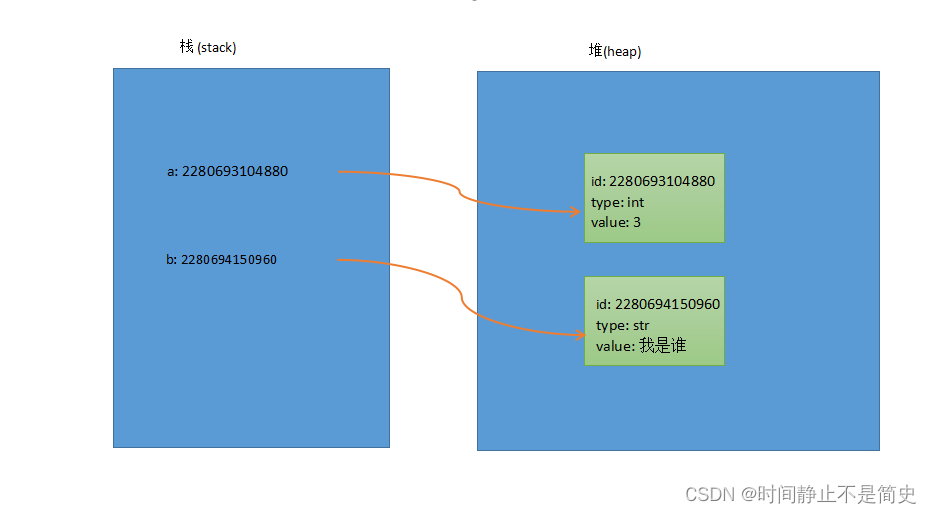

655 量。 比如: a = 3 變量賦值內存變化情況: 運行過程中,解釋器先運行右邊的表達式,生成一個代表表達式運算結果的對象; 然后,將這個對象地址賦值給左邊的變量, 如下圖所示: 如果直接調用未賦值的變量, 例如 print(a) 則會報如下錯誤: Traceback (mo

2023-03-05 17:11:26 985

985

使用邏輯門和連續賦值對電路建模,是相對詳細的描述硬件的方法。使用過程塊可以從更高層次的角度描述一個系統,稱作行為級建模(behavirol modeling)。 1. 過程賦值 阻塞賦值和非阻塞賦值

2023-03-17 21:50:05 368

368 當元素的數據類型和數組界限(最低和最高的可能的數組索引)相匹配時,能夠將一個完整數組賦值給另一個數組。如果是這樣,在賦值符后指定數組的標識符。下面的賦值是有效的:

2023-04-10 11:46:59 555

555 用此指令可以對一個整數計數器或一個二進制輸出端賦值,并將賦以的信號和一種條件 (布爾算子)相連接。

2023-04-15 09:54:20 1336

1336 對于VerilogHDL語言中,經常在always模塊中,面臨兩種賦值方式:阻塞賦值和非阻塞賦值。對于初學者,往往非常迷惑這兩種賦值方式的用法,本章節主要介紹這兩種文章的用法。其實,有時候概念稍微不清楚,Bug就會找到我們,下面一文掃清阻塞賦值和非阻塞賦值所有的障礙。

2023-06-01 09:21:57 514

514 通過給模擬輸出端賦值,可通過機器人控制器輸出模擬電壓。

2023-06-05 10:50:04 406

406

可通過賦值運算,可以將一個表達式的值分配給一個變量。賦值表達式的左側為變量,右側為表達式的值。

2023-06-19 10:57:16 3654

3654 今天給大家普及一下阻塞賦值和非阻塞賦值的相關知識

2023-07-07 14:15:12 1239

1239

在轉換中執行賦值時,所使用的值有明顯的區別。

2023-08-03 16:05:20 492

492

”=“阻塞賦值與”<=“非阻塞賦值是verilog語言中的兩種不同的賦值方式,下面將對兩種賦值方式進行比較。方便進行理解和使用。

2023-09-12 09:06:15 587

587

循環是Python編程中非常重要的一個概念,它可以讓我們輕松地重復執行某些代碼塊,從而簡化編程過程并提高代碼的效率。在循環中,我們經常需要創建變量并賦值,這是非常常見的操作。接下來,我將詳盡地解釋

2023-11-23 14:51:59 545

545 在Python中,可以使用 input 函數從用戶那里獲取輸入,并將輸入賦值給變量。當用戶輸入多個值時,可以使用空格、逗號或其他分隔符將它們分開。下面將詳細介紹如何使用 input 函數賦值多個變量

2023-11-23 15:37:40 953

953 通過賦值,一個變量接受另一個變量或者表達式的值。在賦值運算符“;=”左邊的是變量,該變量接受右邊的地址或者表達式的值。

2023-11-29 09:24:32 848

848 并賦值可以通過使用PL/SQL語句塊或使用SQL*Plus工具來實現。下面將詳細介紹這兩種方法以及它們的具體用法。 使用PL/SQL語句塊定義和賦值變量: 在Oracle SQL中,PL/SQL是一種過程化語言,允許在代碼中定義和使用變量。下面是一個示例的PL/SQL語句塊,展示了如何定義和賦值一

2023-12-06 10:46:32 553

553 C語言編程時,各種類型的變量該如何初始化? 在C語言中,每個變量都需要在使用之前進行初始化。初始化是為變量分配內存空間并賦予初始值的過程。C語言提供了不同的初始化方式,根據變量的類型和需求選擇

2023-12-07 13:53:50 434

434 Verilog是一種硬件描述語言,用于設計和模擬數字電路。在Verilog中,同步和異步是用來描述數據傳輸和信號處理的兩種不同方式,而阻塞賦值和非阻塞賦值是兩種不同的賦值方式。本文將詳細解釋

2024-02-22 15:33:04 202

202 Proteus是一種電路設計和仿真軟件,在進行電路設計和仿真時,屬性賦值是非常重要的步驟。屬性賦值工具可以幫助用戶快速有效地配置電路元件的屬性,從而實現電路的準確仿真。下面是關于Proteus屬性

2024-02-23 17:19:55 487

487 MapGIS是一款功能強大的地理信息系統軟件,它提供了豐富的功能和工具,使用戶能夠對地理數據進行快速、高效的管理和分析。其中一個重要的功能就是給區屬性賦值,即對地圖中的區域進行分類和標記,以便更好

2024-02-23 17:49:41 283

283

電子發燒友App

電子發燒友App

評論