本文采用EDA技術,應用目前廣泛應用的Verilog HDL硬件電路描述語言,實現交通燈系統控制器的設計,利用MAX+PLUS 集成開發環境進行綜合、仿真,并下載到CPLD可編程邏輯器件中,完成系統的控制作用。

1 引言

EDA技術是依靠功能強大的電子計算機,在EDA工具軟件平臺上,對以硬件描述語言HDL(Hardware Description Language)為系統邏輯描述手段完成的設計文件,自動地完成邏輯編輯、化簡、分割、綜合、優化和仿真,直至下載到可編程邏輯器件CPLD/FPGA或專用集成電路ASIC(Application Specific Integrated Circuit)芯片中,實現既定的電子電路設計功能。EDA技術使得電子電路設計者的工作僅限于利用硬件描述語言和EDA軟件平臺來完成對系統硬件功能的實現,極大地提高了設計效率,縮短了設計周期,節省了設計成本。

實現路口交通燈系統的控制方法很多,可以用標準邏輯器件,可編程控制器PLC,單片機等方案來實現。但是這些控制方法的功能修改及調試都需要硬件電路的支持,在一定程度上增加了功能修改及系統調試的困難。因此,在設計中采用EDA技術,應用目前廣泛應用的Verilog HDL硬件電路描述語言,實現交通燈系統控制器的設計,利用MAX+PLUS 集成開發環境進行綜合、仿真,并下載到CPLD可編程邏輯器件中,完成系統的控制作用。

2 Verilog HDL硬件描述語言的介紹

Verilog HDL是目前應用最廣泛的一種硬件描述語言。Verilog HDL是在1983年由GDA(GateWay Design Automation)公司的Phil Moorby首創的。1986年,他對Verilog HDL的發展又作出了另一個巨大貢獻:提出了用于快速門級仿真的XL算法。Verilog-XL算法的成功,使Verilog HDL語言得到迅速發展。基于Verilog HDL的優越性,IEEE于1995年制定了Verilog HDL 的IEEE標準,即Verilog HDL1364-1995。Verilog HDL語言具有以下特點:

基本邏輯門,例如and,or和nand等都內置在語言中。

用戶定義原語(UDP)創建的靈活性。用戶定義的原語既可以是組合邏輯原語,也可以是時序邏輯原語。

開關級基本結構模型,例如pmos和nmos等也被內置在語言中。

提供顯示語言結構制定設計中的端口到端口的時延及路徑和設計的時序檢查。

可以用三種不同方式或混和方式對設計建模這些方式包括:行為描述方式—— 使用過程化結構建模;數據流方式—— 使用連續賦值語句方式建模;結構化方式—— 使用門和模塊實例語句描述建模。

能夠描述層次設計,可使用模塊實例結構描述任何層次。

Verilog HDL的描述能力能夠通過使用編程語言接口(PLI)機制進一步擴展。PLI是允許外部函數訪問Verilog模塊內信息,允許設計者與模擬器交互的例程集合。

設計能夠在多個層次相加以描述,從開關級,門級,寄級器傳送級(RTL)到算法級,包括進程和隊列級。

能夠監控擬驗證的執行,即模擬驗證執行過程這設計的值能夠被監控和顯示。

在行為級描述中,Verilog HDL不僅能夠在RTL級上進行設計描述,而且能夠在體系結構描述及其算法級行為上進行設計描述。

3 交通燈系統控制器的設計

3.1 控制器的設計要求

按照路口交通運行的實際情況,在本系統中,設定系統的工作情況如下:

A 方向和B方向各設紅(R)、黃(Y)、綠(G)和左拐(L)四盞燈按合理的順序亮滅,并能將燈亮的時間以倒計時的形式顯示出來。兩個方向各種燈亮的時間應該能夠非常方便地進行設置和修改,此外假設A方向是主干道,車流量大,因此A方向通行的時間應比B方向長一些。其示意圖如圖1所示。

圖1 十字路口交通燈示意圖

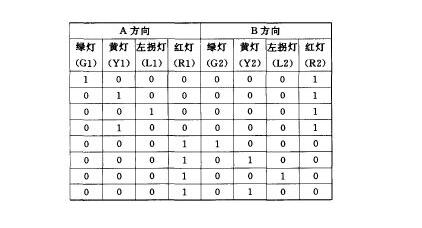

交通燈控制器的狀態轉換如表1所示。表中1表示燈亮,0表示燈滅。A方向和B方向的紅、黃、綠和左拐燈分別用R1、Y1、G1、L1和R2、Y2、G2、L2來表示。

表1 交通燈控制器狀態轉換

從狀態轉換表中可以看出,每個方向四種燈依次按如下順序點亮,并不斷循環:

綠燈→黃燈→左拐燈→黃燈→紅燈。

并且每個方向紅燈亮的時間應該與另一方向綠、黃、左拐、黃燈亮的時間相等。黃燈所起的作用是用來在綠燈和左拐燈后進行緩沖,以提醒行人該方向馬上要禁行了。

3.2 控制器的Verilog HDL程序設計

根據交通燈控制器要實現的功能,考慮用兩個并行執行的always模塊來分別控制A和B兩個方向的四盞燈,這兩個always模塊使用同1個時鐘信號,以進行同步,也就是說,兩個always模塊的敏感信號是同1個。例如A方向的控制程序描述如下:

……

always@(posedge CLK)//該always模塊控制A方向的4種燈

begin

if(EN)

begin

if(!tempa)

begin

tempa《= 1;

……

每個always模塊控制1個方向的4種燈按如下順序點亮,并往復循環:

綠燈→黃燈→左拐燈→黃燈→紅燈。程序描述如下:

……

case(counta)//控制亮燈的順序

0:begin numa《=agreen;LAMPA《=2;counta《=1;end

1:begin numa《=ayellow;LAMPA《=4;counta《=2;end

2:begin numa《=alert;LAMPA《=1;counta《=3;end

3:begin numa《=ayellow;LAMPA《=4;counta《=4;end

4:begin numa《=ared;LAMPA《=8;counta《=0;end

default:LAMPA《= 8;

endcase

……

每盞燈亮的時間采用一個減法計數器進行計數,該計數器采用同步預置法設計,這樣只需改變預置數據,就可以改變計數器的模,因此每個方向只需要1個計數器進行計時即可。為便于顯示燈亮的時間,計數器的輸出均采用BCD碼,顯示由4個數碼管來完成,A方向和B方向各用兩個數碼管。可用如下程序描述:

……

else begin//倒計時

if(numa》1)

if(numa[3:0]==0)begin

numa[-3:0]《=4b1001;

numa[7:4]《=numa[7:4]-1;

end

else numa[3:0]《=numa[3:0]-1;

if(numa==2) tempa《=0;

end

此外,本設計中還設定A方向紅、綠、黃、左拐燈亮的時間分別為65秒、40秒、5秒和15秒,B方向紅、綠、黃、左拐燈亮的時間分別為:55秒、30秒、5秒和15秒。假如要改變這些時間只須改變計數器的預置數即可。程序描述如下:

……

begin//設置各種燈的計數器的預置數

ared《=8b01010101;//65s

ayellow 《=8b00000101;//5s

agreen 《=8b01000000; //40s

aleft 《=8b00010101; //15s

bred 《=8b01100101; //55s

byellow 《=8b00000101; //5s

bleft 《=8b00010101; //15s

bgreen 《=8b00110000; //30s

end

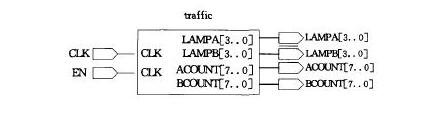

為了更直觀地加以描述,將上面的文本模塊編譯生成一個符號,并加上輸入輸出引腳,構成完整的交通燈控制器頂層電路。如圖2所示。

圖2 交通燈控制器電路

4 仿真結果

仿真運行是HDL的強大功能之一,雖然與現場環境不可能完全一致,但可以幫助設計者解決邏輯錯誤,如果在設計時能夠將器件時序和時延時間考慮完整,并作好準確的描述,就可以最大程度的模擬真實環境,對最后生成的電路改動較少,節約了成本。本設計對整個交通燈控制器用MAX+PLUS軟件編譯并進行時序仿真。

5 總結

erilog HDL有著類似C語言的風格,易于學習和掌握。與傳統的原理圖輸入設計方法相比較,Verilog HDL更適用于規模日益增大的數字系統,用Verilog HDL等硬件描述語言進行數字系統的設計是當前EDA發展的趨勢,也是一種具有廣闊前景的集成電路開發工具。

電子發燒友App

電子發燒友App

評論