高速數字電路的仿真

介紹了專用于高速數字電路的仿真工具Hyperlynx,并使用它對高速數字電路中的阻抗匹配、傳輸線長度

2009-03-20 14:11:39 1275

1275

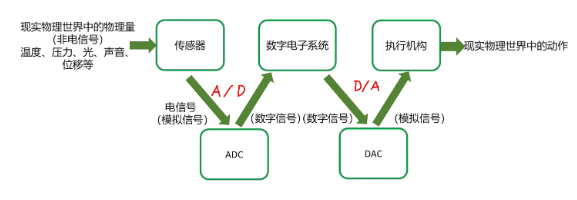

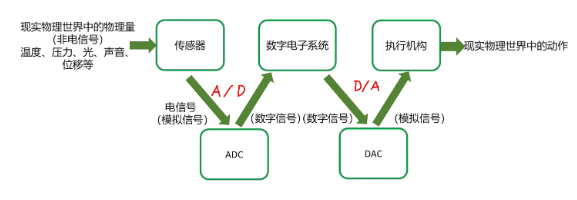

D/A和A/D轉換概述及例題練習

2023-02-07 11:45:51 712

712

Verilog是一種硬件描述語言,用于描述數字電路的結構和行為。與傳統的編程語言不同,Verilog更加注重電路的行為和時序特性。

2023-08-01 09:00:07 1724

1724

VHDL硬件描述語言與和數字邏輯電路設計.侯伯亭&顧新

2020-05-11 09:22:18

VHDL語言的程序結構與數據類型第2節 VHDL語言的程序結構與數據類型[學習要求] 掌握VHDL硬件描述語言的基本語法和源文件的結構,學會用VHDL硬件描述語言設計典型數字邏輯電路。[重點與難點

2009-03-19 14:52:00

超高速集成電路硬件描述語言,主要是應用在數字電路的設計中。它在中國的應用多數是用在FPGA/CPLD/EPLD的設計中。當然在一些實力較為雄厚的單位,它也被用來設計ASIC。VHDL主要用于描述數字系統的結構

2015-09-30 13:48:29

、韓國、美國等區域應用很普遍。本文簡要地介紹國內數字電路設計普遍使用的Verilog語言。verilog是什么。Verilog HDL是一種硬件描述語言,以文本形式來描述數字系統硬件的結構和行為的語言

2021-07-26 06:39:56

P|CB樣板打板 在介紹基本知識時,我們將以集成數字電路為主,該電路又分TTL和CMOS兩種類型,這里又以CMOS集成數字電路為主,因它功耗低、工作電壓范圍寬、扇出能力強和售價低等,很適合電子

2013-09-05 11:12:39

當今時代,數字電路已廣泛地應用于各個領域。本報將在“電路與制作”欄里,刊登系列文章介紹數字電路的基本知識和應用實例。 在介紹基本知識時,我們將以集成數字電路為主,該電路又分TTL和CMOS兩種

2012-12-03 21:37:43

的基本知識和應用實例。 在介紹基本知識時,我們將以集成數字電路為主,該電路又分TTL和CMOS兩種類型,這里又以CMOS集成數字電路為主,因它功耗低、工作電壓范圍寬、扇出能力強和售價低等,很適合電子

2009-04-07 09:39:18

什么是數字電路和模擬電路?數字電路和模擬電路有什么區別?

2021-03-11 07:21:36

話說,數字電路和模擬電路在同一個電路板上最好要隔離,防止相互干擾,為什么會有干擾呢?小弟不才,就此做一個簡單的說明,希望有高手大牛來賜教!簡單來說:數字電路是離散量,說白了就只有1和0,也就是高低

2013-04-19 19:28:25

本文主要詳細介紹了數字電路比模擬電路的優點,分別是數字電路結構簡單、數字電路容易標準化、數字電路能夠...發表于 2019-05-16 17:50?7次閱讀...

2021-09-15 06:02:55

數字電路測試基礎難得的好教材! [hide]數字電路測試基礎.pdf[/hide]

2009-11-20 17:13:50

當今時代,數字電路已廣泛地應用于各個領域。本報將在“電路與制作”欄里,刊登系列文章介紹數字電路的基本知識和應用實例。 在介紹基本知識時,我們將以集成數字電路為主,該電路又分TTL和CMOS

2018-08-28 15:36:27

`求解答。我不想做伸手party。只想弄清楚這個怎么弄?剛學數字電路。望解答`

2017-02-21 22:07:54

描述DIY Protoboard 數字電路用于電子電路的 0.100" 原型板。這對數字和模擬設計都有好處

2022-07-27 06:31:35

I2C總線概述及時序,看完你就懂了

2021-05-24 06:42:06

的輸出與輸入之間的邏輯關系,因而在數字電路中不能采用模擬電路的分析方法,例如,小信號模型分析法。由于數字電路中的器件主要工作在開關狀態,因而采用的分析工具主要是邏輯代數,用功能表、真值表、邏輯表達式

2009-04-06 23:45:00

什么是數字電路?AND電路的工作方式反向輸出的NOT電路

2021-03-17 06:51:27

數字邏輯電路分類數字電路的特點數字電路的應用

2021-04-06 09:08:57

記錄一下,方便以后翻閱~主要內容:1) 內存管理概述及原理;2)相關實驗代碼解讀。官方資料:《STM32中文參考手冊_V10》-第19章 靈活的靜態存儲器控制器(FSMC)。實驗要求:系統啟動后

2022-02-23 06:15:20

華為《高速數字電路設計教材》這本書是專門為電路設計工程師寫的。主要描述模擬電路原理在高速數字電路設計中的分析應用

2014-09-01 23:09:11

華為《高速數字電路設計教材》這本書是專門為電路設計工程師寫的。主要描述模擬電路原理在高速數字電路設計中的分析應用

2014-09-01 23:20:19

高速數字信號的阻抗匹配有什么作用?傳輸線長度對高速數字電路的設計有什么影響?如何對高速數字電路進行仿真測試?

2021-04-21 06:00:00

數字電路是實現一定邏輯功能的電路,稱為邏輯電路,又稱為開關電路。這種電路中的晶體管一般都工作在開關狀態。數字電路可以由分立元件構成(如反相器、自激多諧振蕩器等),但現在絕大多數是由集成電路構成(如與門電路

2021-02-25 07:58:41

已經在開發軟件方面提供了基于本公司芯片的強大開發工具。但由于VHDL設計是行為級設計,所帶來的問題是設計者的設計思想與電路結構相脫節,而且其在設計思路和編程風格等方面也存在差異,這些差異會對系統綜合后的電路整體性能產生重要的影響。如何優化設計?非常值得思考。

2019-08-08 07:08:00

大家好,我是電子愛好者新手,現在想學點數字電路設計。剛把數字電路這么課程學完。我想學電路設計,不知道如何下手。比如FPGA什么的,這些都怎么開始學習啊。請知情者指點下。謝謝

2013-08-02 08:17:31

第一講 數據結構概述及線性表 1 數據結構概述1.1 概述 60年代初期,還沒有獨立的“數據結構”課程,有關內容散見于操作系統、編譯

2010-12-05 21:20:35

與數字邏輯》語言簡潔,知識全面,深入淺出,通俗易懂。在保證理論知識夠用的同時,注重理論聯系實際,培養學生各方面的能力。《新編數字電路與數字邏輯》在編寫過程中注意到電子技術領域的最新變化,將VHDL語言

2018-10-28 21:36:01

模擬電路與數字電路的定義及特點模擬電路與數字電路之間的區別模擬電路和數字電路之間的聯系如何實現模擬和數字電路的功能

2021-03-11 06:58:41

跪求《VHDL數字電路設計》(巴西)的課后習題答案,有的請發郵箱501305928@qq.com萬分感謝。。。。。。。。。。。。。。。

2014-07-19 15:34:33

波音客機概述及特征波音和空客客機的區別在于:· 空中客車的客機駕駛艙最后一扇窗的底邊是平的。· 波音的客機駕駛艙最后一扇窗的底邊是斜的[hide][/hide]

2010-02-24 14:32:17

)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。HDL硬件描述語言(HDL)是一種用來設計數字邏輯系統和描述數字電路的語言,常用的主要有VHDL、Verilog HDL、System Verilog 和 System C。VHDL是一種用于電路設計的高級

2021-12-22 07:39:43

目錄1 概述及應用基本介紹電子羅盤,也叫數字指南針,是利用地磁場來定北極的一種方法,作為導航儀器或姿態傳感器已被廣泛應用。古代稱為羅經,現代利用先進加工工藝生產的磁阻傳感器為羅盤的數字化提供了有力

2021-12-09 06:55:17

硬件描述語言VHDL課件 硬件描述語言VHDL 數字系統設計分為硬件設計和軟件設計, 但是隨著計算機技術、超大規模集成電路(CPLD

2008-09-11 15:47:23

高速數字電路設計的幾個基本概念高速數字電路設計的基本要求是什么

2021-04-27 06:19:05

全面地介紹了VHDL硬件描述語言的基本知識和利用VHDL進行數字電路系統設計的方法。全書共分13章:第1-6

2008-09-11 15:45:27 1333

1333 [學習要求] 掌握VHDL硬件描述語言的基本語法和源文件的結構,學會用VHDL硬件描述語言設計典型數字邏輯電路。[重點與難點]重點:VHDL語言的程序結構;VHDL語言的數據類型及數

2009-03-18 20:02:35 47

47 剖析硬件描述語言VHDL-AMS 的新特性。通過對A/D 轉換器和D/A 轉換器進行建模和仿真分析可以看出,VHDL-AMS 突破了VHDL 只能設計數字電路的限制,使得VHDL 可以應用于模擬以及混合信

2009-07-08 09:49:23 22

22 數字電路EDA入門——VHDL程序實例集的主要內容:第一章 VHSL設計基礎第二章 用VHDL設計組合電路第三章 用VHDL設計時序電路第四章 用電路圖輸入法方法設計

2009-07-20 11:55:08 0

0 VHDL語言概述:本章主要內容:硬件描述語言(HDL)VHDL語言的特點VHDL語言的開發流程

1.1 1.1 硬件描述語言( 硬件描述語言(HDL HDL)H

2009-08-09 23:13:20 47

47 本文介紹了在ALTERA 公司的EDA 軟件MAX+plusII 平臺下用VHDL 語言進行數字電路設計的主要流程,并用一個設計實例闡述演示了設計過程。關鍵詞:電子設計自動化 MAX+plusII 硬件描述

2009-08-25 14:50:32 38

38 VHDL語言描述數字系統:本章介紹用 VHDL 描述硬件電路的一些基本手段和基本方法。 VHDL 語言是美國國防部在 20 世紀 80 年代初為實現其高速集成電路計劃(VHSIC)而提出的

2009-09-01 09:02:40 37

37 vhdl數字系統設計是數字電路自動化設計(EDA)入門的工具書。其內容主要包括:用VHDL語言設計的基本組合電路、時序電路、數字綜合電路、電路圖輸入法要領概述、實用VHDL語句

2009-10-08 21:54:01 0

0 VHDL與數字電路系統設計實驗指導書:《VHDL與數字電路系統設計實驗》是電氣信息類自動化專業、電氣工程及其自動化專業的一門實驗課程,也可供其他相關專業選用。本實驗課

2010-02-06 14:14:21 128

128 VHDL硬件描述語言與數字邏輯電路設計:本書系統地介紹了一種硬件描述語言,即VHDL語言設計數字邏輯電路和數字系統的新方法。這是電子電路設計方法上一次革命性的變化,也是邁

2010-02-06 16:55:22 359

359 摘要:在數字電路課程設計中引入先進的EDA技術是數字電路實驗教學改革的方向,本文通過一個數字電路課程設計的實例,說明了基于EDA技術中的VHDL語言和CPLD/FPGA器件進行數字系

2010-04-26 10:08:50 23

23 摘要:利用數字電路完成對SRD測速電路的沒汁,并用VHDL語言進行描述.經過功能仿真。下載到一片FPGA成單片數字化測速電路,并全數字化的SRD系統使用了該專用測速芯片,其測速精

2010-05-04 10:02:55 33

33 摘要:介紹應用高速集成電路硬件描述語言(VHDL)在Altera公司的MAX+plusII環境下,設計專用分配器和計數器。關鍵詞:VHDL;分配器;計數器

2010-05-13 09:44:11 38

38 本書是專門為電路設計師工程師寫的

它主要描述模擬電路原理在高速數字電路設計中的分析應用

1-3章分別介紹了模擬電路術語、邏輯門高速特性和標準高速電路測量

2010-06-23 18:02:57 63

63 怎樣看數字電路圖緊扣“怎樣看數字電路圖”的主題,系統地介紹了看懂數字電路圖所必須掌握的基礎知識、基本方法和技巧,并通過電路實例進行了

2008-12-26 10:55:08 4524

4524 實驗六、VHDL的基本描述語句設計一? 實驗目的1掌握VHDL語言的基本結構及設計的輸入方法。2掌握VHDL語言的基本描述語句的使用方法。二? 實驗設備

2009-03-13 19:23:57 1998

1998 數字電路是什么意思?

現代的數字電路由半導體工藝制成的若干數字集成器件構造而成。邏輯門是數字邏輯電路的基本單元。存儲器是用來

2009-04-06 23:45:50 7301

7301

數字電路及其應用

編者的話 當今時代,數字電路已廣泛地應用于各個領域。本報將在“電路與制作”欄里,刊登系列文章介紹數字電路的基本知識和應用實例。

2009-04-07 09:38:37 3341

3341 數字電路圖

圖 數字電路圖

監控單元本機監控的實現比較簡單

2009-07-17 10:41:57 1453

1453

數字電路設計

關于高速數字電路的電氣特性,設計重點大略可分為三項:

正時(Timing) :由于數字電路大

2009-08-26 19:08:06 2665

2665 BASIC語言概述及

2010-08-11 18:09:52 4371

4371 《VHDL與數字電路設計》是有盧毅、賴杰主編的,主要介紹涉及數字系統設計的多方面原理、技術及應用,主要內容有數字系統的基本設計思想、設計方法和設計步驟, VHDL 硬件描述語言

2011-07-11 15:54:27 0

0 本書是數字電路電子設計自動化(EDA)入門的工具書,其內容主要包括:用 VHDL 設計的基本組合電路、時序電路、數字綜合電路、電路圖輸入法要領概述、實用VHDL語句等;附錄部分介紹了

2011-08-04 10:17:43 0

0 主要內容有:第1 章實驗基本知識、第2 章 PROTEUS 仿真軟件快速入門、第3 章數字電路基礎實驗、第4 章數字電路綜合設計實驗、 第5章VHDL 語言基礎、第6 章 數字電路的CPLD/FPGA 實現。在教

2011-09-07 16:29:53 0

0 電子發燒友網站提供《[VHDL硬件描述語言與和數字邏輯電路設計].侯伯亭&顧新.掃描版.txt》資料免費下載

2012-07-10 18:32:33 0

0 電子發燒友網核心提示 :硬件描述語言HDL是一種用形式化方法描述數字電路和系統的語言。 利用這種語言,數字電路系統的設計可以從上層到下層(從抽象到具體)逐層描述自己的設

2012-10-15 10:36:08 3385

3385 電子發燒友網站提供《經典教材-VHDL硬件描述語言與數字邏輯電路設計(第三版).txt》資料免費下載

2014-08-27 11:41:09 0

0 本書共分為三個基本組成部分,首先詳細介紹VHDL語言的背景知識、基本語法結構和VHDL代碼的編寫方法;然后介紹VHDL電路單元庫的結構和使用方法,以及如何將新的設計加入到現有的或自己新建立的單元

2016-04-25 17:07:53 0

0 本書共分為三個基本組成部分,首先詳細介紹VHDL語言的背景知識、基本語法結構和VHDL代碼的編寫方法;然后介紹VHDL電路單元庫的結構和使用方法,以及如何將新的設計加入到現有的或自己新建立的單元

2016-04-25 17:07:53 0

0 關于電路的數字報告,能夠解決數字電路的實驗問題。

2016-05-16 11:56:08 1

1 數字電路篇,VHDL資料,又需要的下來看看

2016-08-08 17:03:24 66

66 VHDL語言編程學習之VHDL硬件描述語言

2016-09-01 15:27:27 0

0 VHDL程序實體--EDA資料,設計實體是VHDL語言設計的基本單元,簡單的可以是一個與門,復雜的可以是一個微處理器或一個數字系統,其結構基本是一致的,都是由實體說明和結構體兩部分組成。實體說明

2016-11-21 15:40:34 0

0 脈沖與數字電路

2016-11-05 11:42:40 0

0 VHDL硬件描述語言與數字邏輯電路設計,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 14:20:34 0

0 數字電路7大基礎實驗

2016-12-20 17:20:06 0

0 icepeak教程概述及工程應用

2017-09-16 10:18:41 13

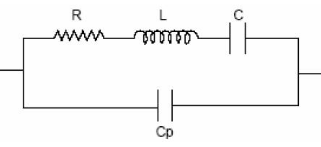

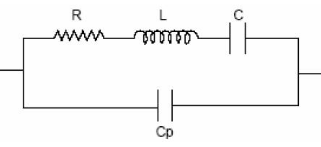

13 我們常說的晶振,實際上是通過切割設備將人工培養的水晶進行薄片切割而得到的,水晶的人工培養主要跟生長環境有關系,目前市面上品質較好的是俄羅斯生長的水晶。之所以說晶振是數字電路的心臟,就是因為所有

2018-01-22 11:19:47 3009

3009

1987年, VHDL被正式確定為IEEE 1076標準。 VHDL是一種強類型語言, 具有豐富的表達能力, 可使各種復雜度(系統級、 電路板級、 芯片級、 門級)的電路網絡在同一抽象程度上被描述

2018-03-30 11:20:15 9

9 VHDL語言是一種在EDA設計中廣泛流行的硬件描述語言,主要用于描述數字系統的結構、行為、功能和接口。除了含有許多具有硬件特征的語句外,VHDL語言的句法、語言形式和描述風格十分類似于一般的計算機高級語言,是目前硬件描述語言中應用最為廣泛的一種。

2018-03-30 16:04:27 21

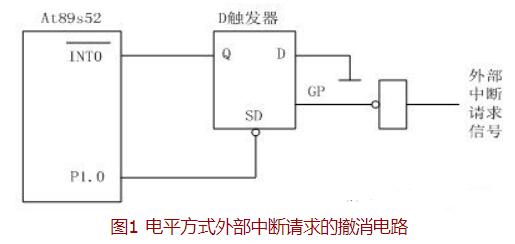

21 在各種復雜的數字電路中不但需要對二值信號進行數值運算和邏輯運算,還經常需要將運算結果保存下來。為此,需要使用具有記憶功能的基本邏輯單元。能夠存儲1位二值信號的基本單元電路統稱為觸發器。

2018-07-20 08:00:00 0

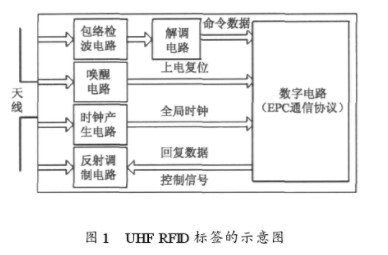

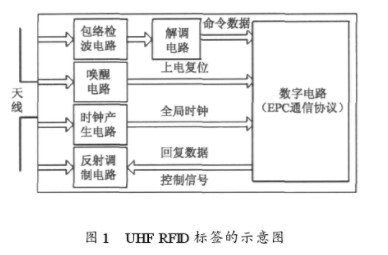

0 在研究讀寫器和射頻標簽通信過程的基礎上,結合EPC C1G2協議以及ISO/IEC18000.6協議, 采用VHDL語言設計出一種應用于超高頻段的射頻標簽數字電路。對電路的系統結構和模塊具體實現方法

2019-08-28 08:03:00 1750

1750

模擬信號和數字信號的特點不同,處理這兩種信號的方法和電路也不同。一般地, 電子電路可分為模擬電路和數字電路兩大類。 1. 模擬電路 處理模擬信號的電子電路稱為模擬電路。模擬電路研究

2018-10-16 10:25:09 97754

97754 本文主要詳細介紹了數字電路比模擬電路的優點,分別是數字電路結構簡單、數字電路容易標準化、數字電路能夠滿足對信號保真度的要求。

2019-05-16 17:50:36 17510

17510 從數字電路中學到的邏輯電路功能,使用硬件描述語言(Verilog/VHDL)描述出來,這需要設計人員能夠用硬件編程思維來編寫代碼,以及擁有扎實的數字電路功底。

2019-12-05 07:10:00 2977

2977

模擬電路與數字電路的關系,有說所有電路都是模擬電路,數字電路只是模擬電路的一部分的;有說模擬電路和數字電路各成系統,井水不犯河水的;有說線性的就是模擬電路,非線性的就是數字電路,不一而足。

2019-07-03 17:35:50 9233

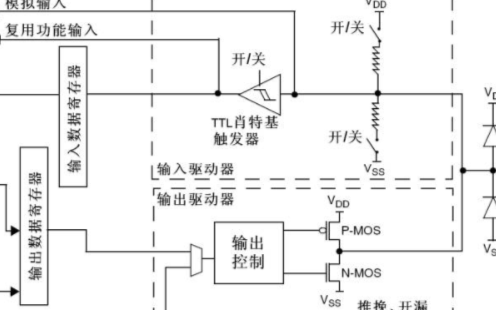

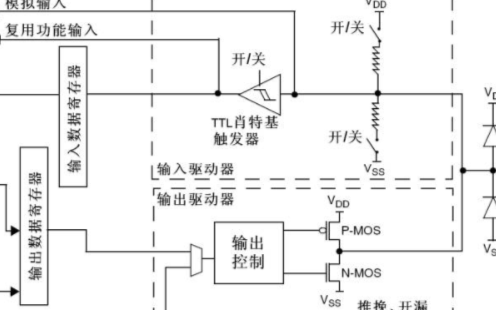

9233 關于IO模式(浮空、推挽、開漏...)描述及應用

2020-03-24 11:06:49 9186

9186

雖然在FPGA中,利用綜合工具來可以將VHDL或者Verilog代碼轉化成電路。但是作為FPGA工程師而言,在沒有綜合工具的情況下,如何設計出數字電路呢?如果已經知道需要實現的功能的狀態機,如何將它轉化成數字電路呢?和設計出數字電路呢?

2020-06-17 16:33:38 2899

2899 。邏輯門是數字邏輯電路的基本單元。存儲器是用來存儲二進值數據的數字電路。 數字電路的特點 電路結構簡單,穩定可靠。數字電路只要能區分高電平和低電平即可, 對元件的精度要求不高,因此有利于實現數字電路集成化。 數字信號

2022-12-05 17:36:59 7096

7096 本文檔的主要內容詳細介紹的是使用VHDL實現數字電路設計的詳細資料說明包括了:ASIC技術的發展,電路系統設計方法,自定向下的設計流程,設計描述風格。

2021-01-21 17:03:18 14

14 本文檔的主要內容詳細介紹的是VHDL硬件描述語言的學習課件免費下載包括了:VHDL概述,VHDL數據類型與數據對象,VHDL命令語句

2021-01-22 08:00:00 5

5 的生成(ATPG)以及測試的時序等諸多問題。并結合最常用的綜合工具 SYNOPSYS 中的 DFT COMPILER 部分,深入描述了為一數字電路芯片加入掃描部分和產生測試矢量集的具體流程。掃描結構對數字電路的結構有一些限制,為了避免違反這些限制,文中羅列了所謂的設計規范,并詳細介紹了如

2021-03-26 14:48:18 22

22 VHDL與Verilog硬件描述語言在數字電路的設計中使用的非常普遍,無論是哪種語言,仿真都是必不可少的。而且隨著設計復雜度的提高,仿真工具的重要性就越來越凸顯出來。在一些

2021-08-04 14:16:44 3307

3307 的,呵呵。我們這里只討論數字電路設計。實際上就是如何把我們從課堂上學到的邏輯電路使用原理圖(很少有人用這個拉),或者硬件描述語言(Verilog/VHDL)來實現,或許...

2021-11-06 11:36:01 18

18 數字電路基礎

2022-03-21 15:12:36 108

108 本書是數字電路電子設計自動化(EDA)入門的工具書。其內容主要包括:用VHDL設計的基本組合電路、時序電路、數字綜合電路、電路圖輸入法要領概述、實用VHDL語句等;附錄部分介紹了VHDL基本知識和基本術語,中小規模集成電路等。

2022-04-07 14:48:12 3

3 數字電路設計是數字電路最為關鍵及重要的一步,今天我們將從各個流程為大家介紹完整的數字電路設計!

2022-07-10 17:14:16 6046

6046 vhdl描述半加器

2023-02-24 11:08:31 0

0 用數字信號完成對數字量進行邏輯運算和算術運算的電路稱為數字電路。由于它具有邏輯運算和邏輯處理功能,所以又稱為數字邏輯電路。

2023-06-06 16:50:29 3984

3984

VHDL與Verilog硬件描述語言在數字電路的設計中使用的非常普遍,無論是哪種語言,仿真都是必不可少的。而且隨著設計復雜度的提高,仿真工具的重要性就越來越凸顯出來。在一些

2023-09-09 10:16:56 721

721

VHDL (VHSIC Hardware Description Language),是一種硬件描述語言,可以用于描述電路的結構、功能和行為等,并進行仿真和驗證。VHDL具有規范性、綜合性和模擬性等特點,已被廣泛應用于數字電路的設計和仿真中。

2023-09-29 10:40:00 554

554

正在加载...

電子發燒友App

電子發燒友App

評論