EDA是芯片設(shè)計(jì)最上游、壁壘最高的部分,也是國(guó)內(nèi)芯片產(chǎn)業(yè)幾乎最薄弱的環(huán)節(jié)。

2020,滄海橫流,疫病橫生,偏偏此時(shí)國(guó)際關(guān)系劍拔弩張。以中美摩擦為劇,一時(shí)間火花四濺,駭浪驚濤。

從中興通信事件為始到“516”華為全面進(jìn)入實(shí)體清單,此間已二年有余。

尤其以半導(dǎo)體為首的科技產(chǎn)業(yè)被推入風(fēng)口浪尖,甚至一個(gè)企業(yè),便要承受一個(gè)國(guó)家的命運(yùn)和擔(dān)當(dāng)。

作為產(chǎn)程密集度、工業(yè)自動(dòng)化程度、技術(shù)密集度最高,代表人類最頂級(jí)智慧結(jié)晶的行業(yè),半導(dǎo)體產(chǎn)業(yè)的低國(guó)產(chǎn)化、低自給化和產(chǎn)業(yè)中低端化,成為此次掣肘中國(guó)的利劍。

電子設(shè)計(jì)自動(dòng)化—— Electronic Design Automation,簡(jiǎn)稱EDA,是芯片設(shè)計(jì)最上游、壁壘最高的部分,卻是國(guó)內(nèi)芯片產(chǎn)業(yè)幾乎最薄弱的環(huán)節(jié),被強(qiáng)行推向舞臺(tái)中央。

作為產(chǎn)業(yè)中樞和設(shè)計(jì)之母,EDA承載起中國(guó)半導(dǎo)體產(chǎn)業(yè)生態(tài)的塑造之路,其產(chǎn)業(yè)位置之重要,見微知著:

以設(shè)計(jì)自動(dòng)化為題,EDA以計(jì)算機(jī)輔助設(shè)計(jì)(CAD)為橋梁,嫁接超大規(guī)模集成電路(VLSI)設(shè)計(jì)中所涉及的功能設(shè)計(jì)、綜合、驗(yàn)證、物理結(jié)構(gòu)(布線、布局和版圖)等流程的全制;

以芯片設(shè)計(jì)生態(tài)為題,EDA發(fā)展的產(chǎn)業(yè)生態(tài)基礎(chǔ),嫁接了代工廠對(duì)于產(chǎn)業(yè)上下游的理解,培植高端芯片設(shè)計(jì)公司,是形成整套半導(dǎo)體系統(tǒng)生態(tài)的中樞神經(jīng);

以半導(dǎo)體生態(tài)為題,EDA作為半導(dǎo)體產(chǎn)業(yè)的發(fā)展杠桿,將會(huì)孕育整個(gè)半導(dǎo)體后摩爾時(shí)代的產(chǎn)業(yè)發(fā)展路徑。以摩爾定律為代表的物理極限被打破,使得配套的設(shè)計(jì)工具和軟件服務(wù),決定了產(chǎn)業(yè)未來(lái)的發(fā)展路徑和天花板。

01?歷史觀瀾:EDA的前世今生

集成電路作為整個(gè)半導(dǎo)體產(chǎn)業(yè)的核心,其技術(shù)設(shè)計(jì)的復(fù)雜性,產(chǎn)業(yè)結(jié)構(gòu)的專業(yè)化,使得一套完整的EDA軟件成為剛需,較之前有限的晶體管布局和布線難度,現(xiàn)有集成電路設(shè)計(jì)之繁雜,規(guī)模之巨大,均不是單純?nèi)肆Ψ秶芨采w。

EDA出現(xiàn)之前,傳統(tǒng)設(shè)計(jì)人員必須通過(guò)手工完成設(shè)計(jì)和布線等基礎(chǔ)工作,彼時(shí)前沿的工程師,不過(guò)是使用集合方法制造用于電路光繪的專用膠帶(Photo plotter)便可滿足需求。

EDA作為高階的電子設(shè)計(jì)自動(dòng)化,并未在彼時(shí)呼之欲出,取決于傳統(tǒng)集成電路的復(fù)雜程度仍較原始,半導(dǎo)體工業(yè)仍延續(xù)粗放生產(chǎn)。

隨著數(shù)據(jù)的快速擴(kuò)張導(dǎo)致計(jì)算量的極限增長(zhǎng),手工設(shè)計(jì)愈發(fā)吃力。為了配合工程師的需求,自動(dòng)完成掩膜草圖開始出現(xiàn),提供電路布局和布線的研發(fā)工具雨后春筍般出現(xiàn)在設(shè)計(jì)人員的視野中。

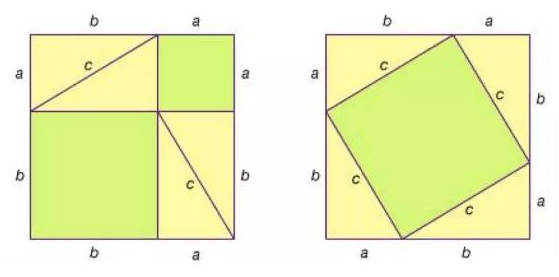

真正的突破出現(xiàn)在1980年,加州理工學(xué)院教授Carver Mead和全錄帕洛阿爾托研究中心的程式設(shè)計(jì)師Lynn Conway共同發(fā)表了一篇具有劃時(shí)代意義的論文《超大規(guī)模集成電路系統(tǒng)導(dǎo)論》 (Introduction to VLSI Systems)。

這篇論文將編程語(yǔ)言構(gòu)建芯片設(shè)計(jì)的新思想推向世界。以此成果編寫的《VLSI系統(tǒng)簡(jiǎn)介》成為當(dāng)時(shí)標(biāo)準(zhǔn)的課堂教材,在超過(guò)一百所高校里使用。

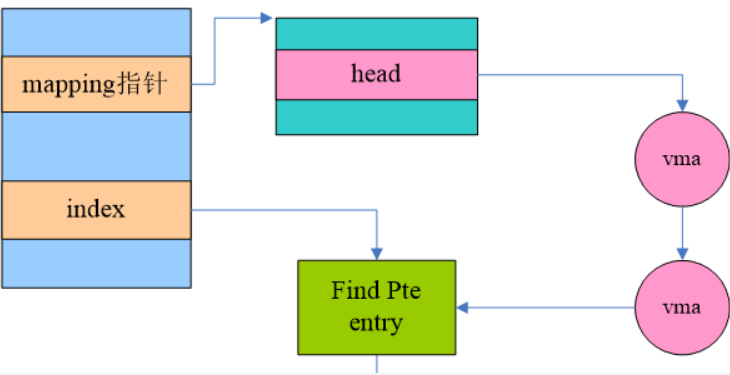

具體展開,EDA到底在芯片設(shè)計(jì)中扮演著怎樣的重要角色?

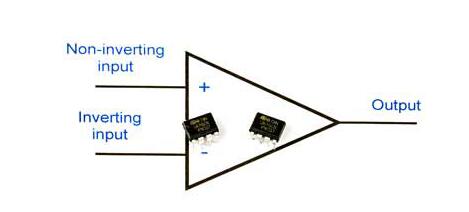

芯片設(shè)計(jì)分為前端和后端,前端調(diào)節(jié)芯片邏輯,后端完成物理實(shí)現(xiàn)。

二者清晰劃分但并不嚴(yán)格切分界限,涉及一切工藝相關(guān)則統(tǒng)一劃分為后端,前端則對(duì)芯片門級(jí)網(wǎng)表電路進(jìn)行邏輯梳理,一則實(shí)現(xiàn)對(duì)芯片的功能定義,二則為功能實(shí)現(xiàn)行為尋找物理路徑,最終形成布局規(guī)劃和邏輯輸出。

芯片設(shè)計(jì)的過(guò)程,就是工程師利用程式碼規(guī)劃芯片功能的過(guò)程。而通過(guò)EDA工具,工程師得以將程式碼轉(zhuǎn)化成為實(shí)際電路設(shè)計(jì)。

再具體一點(diǎn):

工程師向EDA提供完整的HDL code(Hardware Description Language,硬件描述語(yǔ)言代碼);

EDA會(huì)根據(jù)邏輯閘設(shè)計(jì)圖的規(guī)格對(duì)該代碼進(jìn)行修改和調(diào)整,生成功能正確的電路圖;

最后供給后端進(jìn)行布局模擬和電路制作,形成光罩,然后流片成產(chǎn)品

作為邏輯綜合工具的EDA,不僅為設(shè)計(jì)的邏輯閘提供意見的修改,其更重要的價(jià)值是在SoC(System on Chip,系統(tǒng)級(jí)芯片)數(shù)以億計(jì)的今天,大幅度地降低了設(shè)計(jì)試錯(cuò)成本。

大規(guī)模集成電路的復(fù)雜度,已經(jīng)遠(yuǎn)超人類設(shè)計(jì)仿真的控制極限。因此,在動(dòng)輒流片費(fèi)用百萬(wàn)千萬(wàn)計(jì)的今天,任何一家芯片公司都無(wú)法承受數(shù)次流片失敗的成本。設(shè)計(jì)環(huán)節(jié)的絲毫差錯(cuò),都可能導(dǎo)致巨大的財(cái)務(wù)損失。

EDA的出現(xiàn),至少將此成本縮減超百倍。

隨后,集成電路的布道者們開始大肆宣傳集成電路與承載的人類命運(yùn),幾乎和集成電路所能承載的復(fù)雜程度直接關(guān)聯(lián)。這在當(dāng)時(shí)看起來(lái)幾乎荒誕的理論,在40年后的今天一語(yǔ)中的 ——

通過(guò)編程語(yǔ)言設(shè)計(jì)和驗(yàn)證電路預(yù)期行為,并通過(guò)邏輯綜合工具軟件得到低抽象級(jí)物理設(shè)計(jì)的研發(fā)途徑,迄今為止仍然是數(shù)字集成電路設(shè)計(jì)的思想基礎(chǔ)和工程基礎(chǔ)。

在這個(gè)基礎(chǔ)之上,EDA的商業(yè)化在上世紀(jì)80年代高速發(fā)展:

1981年,日后主宰全球EDA市場(chǎng)的三大巨頭之一Mentor Graphics悄然誕生,日后名聲飛揚(yáng)的Xpedition、PADS、Mentor EE均誕生于此;

1986年,Gateway提出Verilog,這是迄今為止最流行的高級(jí)抽象語(yǔ)言;

同年,三巨頭之二Synopsys誕生于美國(guó)加州Mountain View;

1987年,美國(guó)國(guó)防部資助的VHDL(Very-High-Speed Integrated Circuit Hardware Description Language,超高速集成電路硬件描述語(yǔ)言)問(wèn)世,將設(shè)計(jì)實(shí)體分為內(nèi)外部分,日后被廣泛應(yīng)用于機(jī)械工程、儀器科學(xué)和計(jì)算機(jī)科學(xué)中;

1988年,第三家巨頭Cadence誕生在美國(guó)加州San Jose。

產(chǎn)業(yè)規(guī)模的急速擴(kuò)張和競(jìng)爭(zhēng)逐步加劇,導(dǎo)致分工模式進(jìn)一步細(xì)化。

EDA猶如達(dá)摩克斯的利劍,精確切分原來(lái)由IDM (Integrated Device Manufacturer,集約化制造商)主導(dǎo)的半導(dǎo)體產(chǎn)業(yè)生態(tài),逐步演化成了Fabless(無(wú)工廠僅設(shè)計(jì)) + Foundry(代工廠) + OSAT(Out Sourced Assembly and Testing,封測(cè)代工廠)的產(chǎn)業(yè)格局。

后來(lái)耳熟能詳?shù)?a target="_blank">IC設(shè)計(jì)、IC制造和IC封裝,三大核心板塊逐漸形成。

因?yàn)镋DA,產(chǎn)業(yè)生態(tài)的上中下游,第一次被清晰的展現(xiàn)出來(lái)。

“當(dāng)價(jià)格不變時(shí),集成電路上可容納的元器件的數(shù)目,約每隔18-24個(gè)月便會(huì)增加一倍,性能也將提升一倍。”

——戈登·摩爾(英特爾創(chuàng)始人之一)

摩爾定律作為半導(dǎo)體行業(yè)的金科玉律已運(yùn)轉(zhuǎn)多年,應(yīng)驗(yàn)了無(wú)數(shù)半導(dǎo)體發(fā)展的重大時(shí)刻,并像圣經(jīng)一般,收斂了整個(gè)芯片產(chǎn)業(yè)上下游的發(fā)展和演化規(guī)律,使其達(dá)到了實(shí)質(zhì)意義上的統(tǒng)一。

而EDA的迭代,數(shù)年來(lái)也追隨摩爾定律有序發(fā)展,承載了人類迄今為止超大規(guī)模集成電路的設(shè)計(jì),發(fā)展和產(chǎn)業(yè)化演進(jìn)。

但凡事終有極限,物理性征的限制,使得摩爾定律大有被替代更新的趨勢(shì)。

在2019年人類撬開7nm大門后,傳統(tǒng)EDA支撐下的IC設(shè)計(jì)遭遇瓶頸,對(duì)復(fù)雜設(shè)計(jì)的不斷追求和提升集成電路性能,并縮小尺寸的要求進(jìn)一步提升。

如何在EDA上追趕并超越摩爾定律,成為人類觸碰下一代超大規(guī)模集成電路的核心要素 —— AI,物聯(lián)網(wǎng)和虛擬現(xiàn)實(shí)等技術(shù)的不斷更迭,人類對(duì)集成電路的要求也越發(fā)提升,對(duì)EDA的智能型要求也愈發(fā)提升。

以IT產(chǎn)業(yè)為例,手機(jī)和服務(wù)器為代表的設(shè)備更替周期從2010年全面到來(lái)至今年為止,人類社會(huì)對(duì)智能手機(jī)、大規(guī)模數(shù)據(jù)中心的替代基本結(jié)束。下一代智能終端包括和5G相關(guān)的各類硬件及軟件工具將再一次帶來(lái)設(shè)備更迭的產(chǎn)業(yè)浪潮。

因此,對(duì)集成電路的要求、設(shè)計(jì)復(fù)雜度的要求和可靠性的要求將更勝彼時(shí),定制化、高個(gè)性化、私有化的要求也會(huì)隨著產(chǎn)業(yè)周期的變革愈發(fā)高漲。

EDA工具除了設(shè)計(jì),服務(wù)能力和智能化程度,必然會(huì)進(jìn)一步劃分EDA市場(chǎng)的終極格局和生態(tài)構(gòu)成。

02?生態(tài)為王:EDA催生的IP生態(tài)

芯片設(shè)計(jì)所形成的重復(fù)使用設(shè)計(jì)模塊,被稱為我們常聽到的IP(Intellectual Property,知識(shí)產(chǎn)權(quán)核)。

一個(gè)成功的IP設(shè)計(jì)往往擁有獨(dú)家版權(quán),并且將成為未來(lái)功能化芯片設(shè)計(jì)改良的母版,被各大公司采購(gòu)和重復(fù)利用,造就了高通、英特爾等巨頭。

并不是每個(gè)新的芯片都需要重復(fù)設(shè)計(jì)每個(gè)細(xì)節(jié),各家公司可以通過(guò)購(gòu)買成熟可靠的IP方案,在原有的IP基礎(chǔ)上搭建特定的客戶需求和技術(shù)方案,從而縮短設(shè)計(jì)開發(fā)流程,提高可靠性,將芯片的產(chǎn)業(yè)價(jià)值和規(guī)模最大化。

作為已經(jīng)存在世間超過(guò)50年的傳統(tǒng)型工業(yè),集成電路工業(yè)已積累了數(shù)以萬(wàn)計(jì)的成熟IP供市場(chǎng)使用,現(xiàn)有的不少SoC廠商通過(guò)發(fā)掘市場(chǎng)中成熟的IP進(jìn)行自我演進(jìn),并在功能上精確嫁接客戶需求,縮短整個(gè)交付流程:

研發(fā)周期、交付周期和迭代周期同比例得到精簡(jiǎn)和優(yōu)化,這個(gè)產(chǎn)業(yè)思路逐步擴(kuò)大到各個(gè)SoC廠商成為固定套路,整合和發(fā)掘IP滿足客戶需求并大規(guī)模出貨,成為廠商迅速實(shí)現(xiàn)規(guī)模化,集成化優(yōu)勢(shì)壁壘的通途。

在串聯(lián)IP商業(yè)價(jià)值上,EDA為IP內(nèi)核提供了三種表現(xiàn)形式:

HDL語(yǔ)言形式的加密軟核。設(shè)計(jì)周期短,投入少且布線靈活,但后續(xù)工序與前序被切斷,性能難以持續(xù)優(yōu)化;

網(wǎng)表形式的固核。通過(guò)頭文件或GUI(Graphical User Interface,圖形用戶接口)進(jìn)行參數(shù)操作,收斂其他電路設(shè)計(jì)與該內(nèi)核之間的接口;

版圖形式的硬核。從掩膜出發(fā),針對(duì)特定工藝進(jìn)行功耗和尺寸的優(yōu)化,不提供RTL(Register Transfer Level,寄存器轉(zhuǎn)換級(jí)電路),因而更易于實(shí)現(xiàn)IP保護(hù)。

可以看出,三種特定的表現(xiàn)形式使得IP模塊和芯片設(shè)計(jì)企業(yè)的研發(fā)體系高度耦合。

作為具備先發(fā)優(yōu)勢(shì)的歐美廠家,IP的豐富程度,與SoC企業(yè)的深度耦合經(jīng)驗(yàn)和歷史,讓雙方的競(jìng)爭(zhēng)力成為一個(gè)密不可分的有效整體。

分立的EDA公司一枝獨(dú)秀絕不能支撐整個(gè)體系,需要與系統(tǒng)級(jí)開發(fā)商深度耦合,系統(tǒng)級(jí)開放商對(duì)產(chǎn)業(yè)深度理解并挖掘客戶需求,最終反饋到IP設(shè)計(jì),再反向傳導(dǎo)至EDA完成閉環(huán)。

不斷的演進(jìn)和替代,才能形成真正的生態(tài)和競(jìng)爭(zhēng)模式。

EDA企業(yè),SoC廠商,IP授權(quán)方深度和長(zhǎng)期捆綁,最終決定了EDA產(chǎn)業(yè)贏家通吃的基本局面。新進(jìn)者無(wú)論具備怎樣密集和有效的設(shè)計(jì)基礎(chǔ)和能力,都很難打破現(xiàn)有的產(chǎn)業(yè)格局。

不過(guò)如前面所述,隨著科技發(fā)展和產(chǎn)業(yè)周期迭代,傳統(tǒng)數(shù)字電路IP生產(chǎn)的方式方法,也在悄然發(fā)生改變。頂層架構(gòu)設(shè)計(jì)和模塊指標(biāo)的模擬IP,如今已可自動(dòng)生成和生產(chǎn)。自動(dòng)IP的生成逐步成熟,使最優(yōu)設(shè)計(jì)完全可以通過(guò)本身有效的數(shù)據(jù)收斂,得到理論上的最優(yōu)解。

2018年,半導(dǎo)體IP市場(chǎng)規(guī)模約為46億美元,而模擬IP自動(dòng)生成領(lǐng)域,下穿到垂類行業(yè)(如射頻、數(shù)模混合、處理器等)的話,當(dāng)前基數(shù)均可忽略不計(jì)。

作為新興行業(yè),自動(dòng)模擬IP生成工具的優(yōu)化和產(chǎn)業(yè)化,未來(lái)將很可能成為EDA新的戰(zhàn)場(chǎng),跳過(guò)SoC形成的原有格局,在新格局上重新競(jìng)爭(zhēng),重新劃分江湖。

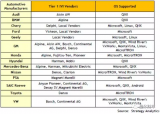

03?S、C、MG:EDA三座大山

EDA從無(wú)到有,并最終成為撬動(dòng)整個(gè)半導(dǎo)體行業(yè)的杠桿和基石,前面提到的三大EDA廠商以江湖盟主的姿態(tài),霸占產(chǎn)業(yè)山頭。

提EDA,Synopsys就是不可逾越的大山,是EDA世界當(dāng)之無(wú)愧的王者,行業(yè)制定者和領(lǐng)軍人。在EDA的發(fā)展軌跡上,提供整體解決方案即Total solution,并從整體方案往下延展行業(yè)渠道的公司,往往更有競(jìng)爭(zhēng)力 ——猶如在半導(dǎo)體行業(yè)里掌握分立器件技術(shù)的公司比比皆是,但是捏合起來(lái)成為整體卻艱難異常。

縱觀美國(guó)半導(dǎo)體巨頭發(fā)展簡(jiǎn)史,掌握Total solution能力的巨頭,往往是從單一器件和單一能力入手切入市場(chǎng),通過(guò)大規(guī)模的整合并購(gòu),完成自我能力的塑造和建設(shè)。

以Synopsys為例,34年的發(fā)展歷史上,從幼年期收購(gòu)Zycad公司的VHDL仿真業(yè)務(wù)入手,使得Synopsys一夜間掌握了前后端一體化的EDA能力,如此甜頭在往后的歲月里被不斷復(fù)制,加強(qiáng),逐步衍生出全套的技術(shù)解決和工程驗(yàn)證能力,最終成為一代領(lǐng)軍。

有意思的是,整合并購(gòu)作為一種典型擴(kuò)張手段,三大巨頭具有明顯的不同,這和企業(yè)本身的基因高度相關(guān)。

Synopsys從誕生初期便立足于為客戶在整體上優(yōu)化設(shè)計(jì)環(huán)境,核心Knowhow隱藏在產(chǎn)品后不讓客戶直接感知,產(chǎn)品迭代速度和發(fā)展,通過(guò)內(nèi)部研發(fā)和交易并購(gòu)解決。

從Astro、DFT到TetraMAX和Vera等產(chǎn)品來(lái)看,Synopsys力圖從產(chǎn)品整體的角度,致力優(yōu)化設(shè)計(jì)、布局到布線的整體環(huán)境,便于客戶在設(shè)計(jì)流程的前期更加容易熟悉和感知環(huán)境,確保在時(shí)序和測(cè)試覆蓋要求同時(shí)滿足的情況下,盡可能提升操作體驗(yàn),為客戶的設(shè)計(jì)服務(wù)提供更自由的工具和交付空間。

Cadence從誕生的第一天便是高度混合的個(gè)體,前身SDA System和ECAD作為EDA江湖最早出現(xiàn)在公眾視野的頂尖公司,擅長(zhǎng)領(lǐng)域和對(duì)前后端理解有諸多不同,而二者最終于1988年合二為一,將Cadence瞬然保送至全球第一EDA企業(yè)的高度。

從程序方案服務(wù)和設(shè)計(jì)服務(wù),覆蓋從半導(dǎo)體、計(jì)算機(jī)系統(tǒng)、網(wǎng)絡(luò)工程、消費(fèi)電子及其他各類電子產(chǎn)品的設(shè)計(jì),使其覆蓋的產(chǎn)業(yè)和技術(shù)遠(yuǎn)超同類競(jìng)爭(zhēng)對(duì)手,加上常年近40%的研發(fā)投入和美國(guó)國(guó)防部的長(zhǎng)期支持,使得Cadence在2002年之前,一直處于全球EDA之巔。

Mentor Graphics的核心是EDA軟硬件耦合,對(duì)PCB解決方案的設(shè)計(jì)上,提供EDA和模擬硬件系統(tǒng)。產(chǎn)業(yè)較前兩家有一定差距,沒(méi)有提供Total solution的能力,但PCB設(shè)計(jì)工具方案的完整度,使得該公司仍然穩(wěn)居世界第三。

產(chǎn)業(yè)并購(gòu)方面,MG自成立至今雖然也有66起并購(gòu)發(fā)生,但產(chǎn)生行業(yè)影響力的事件并不多,最終在2016年11月以45億美元賣身西門子,成為西門子數(shù)字工廠的一部分。

04?國(guó)產(chǎn)替代:圍剿中艱難啟航

伴隨中美對(duì)抗走入全新時(shí)局,半導(dǎo)體自給率將由主動(dòng)替換走向被動(dòng)替換,中國(guó)已是全球最大的半導(dǎo)體消費(fèi)市場(chǎng),據(jù)預(yù)測(cè)2020年將達(dá)到全球半導(dǎo)體消費(fèi)總額的60%。

然而作為擁有超過(guò)86座光晶圓廠的超極半導(dǎo)體大國(guó),卻不得不面臨國(guó)內(nèi)EDA孱弱的現(xiàn)實(shí):

EDA的自給化率卻低于15%;

純EDA國(guó)產(chǎn)化率低于5%,今年可能因?yàn)镾oC工藝迭代而降至3%;

擁有全棧式技術(shù)路線,并大規(guī)模投入生產(chǎn)制造環(huán)節(jié)的公司小于5家。

嚴(yán)重的產(chǎn)業(yè)結(jié)構(gòu)倒掛,既揭開了中國(guó)EDA發(fā)展的現(xiàn)實(shí),也孕育了巨大的國(guó)內(nèi)需求和替代機(jī)會(huì)。風(fēng)險(xiǎn)和機(jī)會(huì)并存,并將在未來(lái)的中國(guó)半導(dǎo)體生態(tài)中長(zhǎng)期存在 ——

如果說(shuō)半導(dǎo)體是中美貿(mào)易戰(zhàn)中最被卡脖子的一個(gè)問(wèn)題,那EDA的孱弱則是這個(gè)卡脖子問(wèn)題中最核心之一。

歷史上,EDA從誕生的第一天就進(jìn)入歐美半導(dǎo)體產(chǎn)業(yè)體系被集中保護(hù),從建國(guó)初期的“巴統(tǒng)”禁運(yùn)(巴黎統(tǒng)籌委員會(huì)對(duì)中國(guó)實(shí)行禁運(yùn),國(guó)外EDA無(wú)法進(jìn)入中國(guó)),到1988年打破封鎖的熊貓系統(tǒng)橫空出世,再到1994年巴統(tǒng)禁運(yùn)取消,全球EDA產(chǎn)品全面進(jìn)入中國(guó)。

國(guó)內(nèi)EDA企業(yè)經(jīng)歷了早期探索,還未脫開襁褓卻又迎來(lái)國(guó)外EDA的豺狼虎豹。隨后市場(chǎng)的凋敝又帶來(lái)研發(fā)費(fèi)用不足和資本投入周轉(zhuǎn)緩慢等連鎖效應(yīng),造成了當(dāng)前中國(guó)EDA發(fā)展緩慢,難以與三大巨頭抗衡的局面。

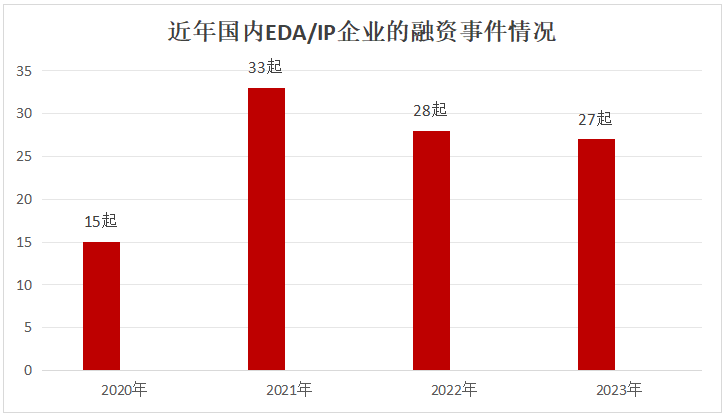

一直到2008年國(guó)家核高基的鼓勵(lì)扶持,以華大九天為首的中國(guó)EDA企業(yè)開始進(jìn)入市場(chǎng)的主流視野。持續(xù)的技術(shù)投入、人才積累、與IP的有效粘連,也讓一批企業(yè)從長(zhǎng)尾客戶切入,逐漸站穩(wěn)腳跟。

同時(shí),中國(guó)EDA市場(chǎng)的發(fā)展必然與本土半導(dǎo)體產(chǎn)業(yè)的發(fā)展息息相關(guān)。中國(guó)Fabless廠家已經(jīng)占據(jù)全球四分之一的份額,原創(chuàng)IP逐步出現(xiàn),急需一批提供與IP相關(guān)服務(wù)工具強(qiáng)粘連的服務(wù)商和渠道商。

因此作為承載熊貓系統(tǒng)等核心技術(shù)的華大九天,在國(guó)內(nèi)被稱為EDA的先行者,也是領(lǐng)先者。

盡管2009年公司才正式宣告成立,但從承載熊貓系統(tǒng)的技術(shù)、EDA和IP方面的積累,多次增資和更換股東,尤其大股東從華大集成電路到中國(guó)電子的轉(zhuǎn)移,華大九天都擁有了在國(guó)內(nèi)問(wèn)鼎華山的實(shí)力和潛力。

從核心產(chǎn)品和已取得的成就上也可以看出:

模擬IC設(shè)計(jì)的全流程EDA系統(tǒng)國(guó)內(nèi)唯一,也是全球四大模擬設(shè)計(jì)全流程平臺(tái),仿真技術(shù)可支持7 nm工藝,出貨量過(guò)百億,SKU達(dá)到數(shù)百款;

數(shù)字SoC設(shè)計(jì)優(yōu)化EDA,覆蓋國(guó)內(nèi)90%以上企業(yè),已基本完成國(guó)產(chǎn)化替代;

晶圓制造專用工具,掩膜板處理軟件全球第一;

平板設(shè)計(jì)EDA全球唯一,國(guó)內(nèi)新建產(chǎn)線超過(guò)半數(shù)都采用該系統(tǒng)。

華大九天的發(fā)展基調(diào)也定位在垂類行業(yè)的Total solution上,例如在數(shù)字SoC設(shè)計(jì)優(yōu)化的EDA領(lǐng)域,已經(jīng)形成從標(biāo)準(zhǔn)單元庫(kù)特征化、工藝資料分析檢驗(yàn)、規(guī)則檢車時(shí)鐘分析、到一站式版圖分析集成逐一擊破的整體能力。

就像前面所述,EDA的發(fā)展并非孤島,華大九天最大的優(yōu)勢(shì)便是中國(guó)半導(dǎo)體的海量市場(chǎng)支撐。

盡管產(chǎn)業(yè)上下游從當(dāng)下來(lái)看,大多并不具備高端器件的生產(chǎn)及整合能力,但巨大的市場(chǎng)潛力和需求、日趨動(dòng)蕩的中美關(guān)系,加上EDA本身特殊的產(chǎn)業(yè)位置,都催生華大九天繼續(xù)深入產(chǎn)業(yè)上下游,做好整個(gè)IC設(shè)計(jì)的母版和粘合劑。

其次,中國(guó)的人工智能產(chǎn)業(yè)發(fā)展,通信射頻、汽車電子、MEMS(微機(jī)電系統(tǒng))等各領(lǐng)域資本的瘋狂布局,一定會(huì)催生以國(guó)產(chǎn)化替代為主的EDA浪潮,這個(gè)浪潮的核心是通過(guò)產(chǎn)業(yè)下游催生產(chǎn)業(yè)上游的國(guó)產(chǎn)化改良和產(chǎn)業(yè)流程的再造。

對(duì)中低端開發(fā)廠商而言,具備定制化能力提供IP和EDA軟件授權(quán)的企業(yè)大有人在,急需專業(yè)EDA技術(shù)支持進(jìn)行設(shè)計(jì)整合。

同樣,提供集成器件設(shè)計(jì)和集成能力的制造商雖為數(shù)眾多,但下游場(chǎng)景從之前的工業(yè)自動(dòng)化、電子、航空航天等領(lǐng)域,早已滲透到消費(fèi)級(jí)電子產(chǎn)品、通信領(lǐng)域的基站和設(shè)備、高性能服務(wù)器及計(jì)算存儲(chǔ)單元。

一切都在倒逼國(guó)內(nèi)EDA設(shè)計(jì)企業(yè)提供具有中國(guó)特色的電路分析服務(wù)和設(shè)計(jì)服務(wù)。

除了華大九天,廣立微電子,今年5月申報(bào)科創(chuàng)板的芯愿景,還有創(chuàng)業(yè)公司中的藍(lán)海微科技、博達(dá)微科技、奧卡思微電子等等,也通過(guò)器件建模、PDK(Process Design Kit,工藝設(shè)計(jì)包)驗(yàn)證、形式驗(yàn)證等產(chǎn)品,為半導(dǎo)體企業(yè)提供除去主體設(shè)計(jì)外的集成電路工藝設(shè)計(jì)包、半導(dǎo)體參數(shù)測(cè)試和器件驗(yàn)證等全流程的服務(wù)工具。

05?結(jié)尾:戰(zhàn)事才開始

無(wú)論是暫時(shí)領(lǐng)先的華大九天,還是即將登陸資本市場(chǎng)的芯愿景或早期公司,想要在本輪市場(chǎng)浪潮中獲得有效機(jī)會(huì)并趕超巨頭,可能需要具備以下三個(gè)條件:

打信息差:產(chǎn)品矩陣模仿國(guó)外三大巨頭意義不大,基于中國(guó)IC設(shè)計(jì)市場(chǎng)提供定制化方案,勢(shì)必要打三大巨頭在中國(guó)半導(dǎo)體生態(tài)中的信息差;

人才為王:充分利用此時(shí)半導(dǎo)體市場(chǎng)的集中火爆,用最大的可能性吸收EDA核心人才,重塑人才梯隊(duì),半導(dǎo)體的核心競(jìng)爭(zhēng)永遠(yuǎn)是人才稀缺性;

共建生態(tài):EDA的發(fā)展絕不是孤立存在,客戶替代意愿只能歸為強(qiáng)制替代而不是市場(chǎng)化行為,EDA本身的工作遠(yuǎn)沒(méi)有建立一個(gè)共榮的生態(tài)重要。

2020年,作為半導(dǎo)體設(shè)計(jì)之母的EDA,從最初的高深莫測(cè),裹挾著焦慮和民族情緒,終于走到時(shí)代的中央。

在全球疫病當(dāng)前的今天,中國(guó)半導(dǎo)體市場(chǎng)伴隨著資本和政策的簇?fù)恚缁鹑巛薄_@份火熱既有市場(chǎng)對(duì)于沉寂多年的高科技的確定性補(bǔ)償,更多則體現(xiàn)出民族對(duì)于攻破半導(dǎo)體枷鎖的信心,甚至信仰:

一個(gè)強(qiáng)大的中國(guó),一定要擁有一顆強(qiáng)大的中國(guó)芯。

EDA的中場(chǎng)戰(zhàn)事,才剛剛開始。

? ? ? ? 責(zé)任編輯:tzh

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論