全球電子設計創新企業Cadence設計系統公司日前宣布其與TSMC在3D IC設計基礎架構開發方面的合作。

2012-06-11 09:47:43 1071

1071 Cadence設計系統公司,在TSMC最近舉辦的Open Innovation Platform Ecosystem Forum上因DRAM接口IP和技術方面的相關論文而獲得“客戶首選獎”

2013-01-30 09:08:27 842

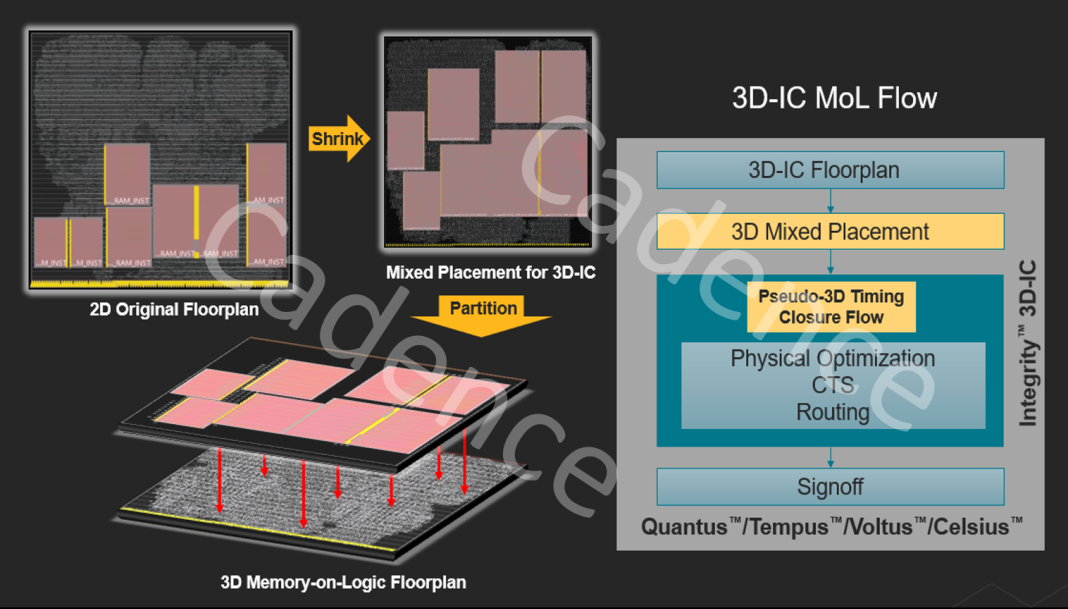

842 Cadence Integrity 3D-IC 平臺是業界首個全面的整體 3D-IC 設計規劃、實現和分析平臺,以全系統的視角,對芯片的性能、功耗和面積 (PPA) 進行系統驅動的優化,并對 3D-IC 應用的中介層、封裝和印刷電路板進行協同設計。

2022-05-23 17:13:53 4218

4218 Integrity 3D-IC 平臺具有強大的數據管理功能,能夠實現跨團隊的一鍵數據同步與更新。同時,Integrity 3D-IC 支持靈活的 3D-IC 實現流程,配合其高效的數據管理機制,可以讓用戶在流程中的多個關鍵階段接入內嵌的分析平臺,進而實現整個系統的快速迭代和 ECO。

2022-07-19 09:34:44 1442

1442

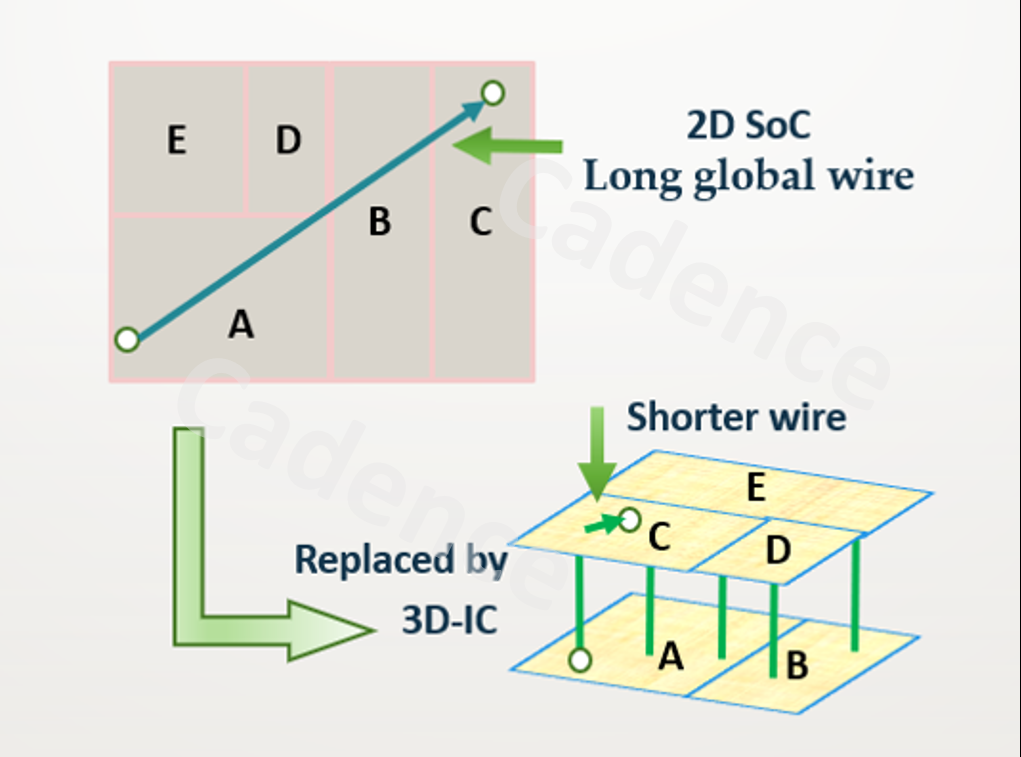

隨著芯片工藝尺寸的縮小趨于飽和或停滯,設計師們現在專注于通過 3D-IC 異構封裝,在芯片所在平面之外的三維空間中構建系統。3D-IC 異構封裝結構可能包括多個芯片,它們被放置在一個通用的中介層上,或者通過芯片內部的高級互連來集成內存單元、處理器和其他功能模塊。

2022-12-09 11:02:18 3231

3231 這是一個業界用于打造差異化定制芯片的領先平臺,可借助生成式 AI 技術顯著提升設計生產力; Virtuoso Studio 與 Cadence 最前沿的技術和最新的底層架構集成,助力設計工

2023-04-20 15:52:13 508

508

3nm 時代來臨了!Cadence 在 2023 年 TSMC 北美技術研討會期間發布了面向臺積電 3nm 工藝(N3E)的 112G 超長距離(112G-ELR)SerDes IP 展示,這是

2023-05-19 16:25:12 784

784

、無廢棄副產品等特性在汽車某些關鍵精巧零部件的制造方面更加方便、快速和高效。而這一技術在汽車行業的應用,機遇遠大于挑戰。為順應市場需求,在各主管部門的支持下,2020中國(北京)國際3D打印與汽車智造

2019-12-20 16:11:32

3D Experience — 產品協同研發平臺

2021-01-08 07:30:52

`2D工程圖紙,難以高效轉化成3D模型數據?多CAD格式混合設計,難以進行標準化?大量舊版本圖紙堆積,難以實現數據重用?浩辰3D制圖軟件不僅具備支持主流3D原生和通用文件的導入,對數據進行直接編輯

2021-02-24 17:22:41

3D顯示技術的原理是什么?3D顯示技術有哪些應用?3D拍好了到底怎么樣傳輸?

2021-05-31 06:53:03

各類顯示和消費電子產品提供具有業界領先水平的視頻技術及方案。易維視擁有長期的3D技術算法積累,在動態背光、超解析、頻率轉換和超多試點方面有技術領先。其中多視點轉換是裸眼3D平板的關鍵技術。多視點

2020-11-27 16:17:14

Cadence設計系統公司發布了Cadence Allegro系統互連設計平臺針對印刷電路板(PCB)設計進行的全新產品和技術增強。改進后的平臺為約束驅動設計提供了重要的新功能,向IC、封裝和板

2018-11-23 17:02:55

設計,并與封裝設計團隊和使用Cadence Allegro? 封裝技術的外包半導體組裝和測試 (OSAT) 公司進行無縫協同設計。 使用 Integrity 3D-IC 平臺的客戶可以獲得以下功能和優勢

2021-10-14 11:19:57

具包與CadenceRFSiPMethodologyKit整合,Jazz在優化RFSiP設計周期方面為Cadence提供支持,從而為我們共同的客戶提供更好的性能和技術,以及更快的產品上市周期。 CadenceSiP解決方案也

2008-06-27 10:24:12

Cadence設計系統公司發布Cadence?Allegro?系統互連設計平臺針對印刷電路板(PCB)設計進行的全新產品和技術增強.改進后的平臺為約束驅動設計提供了重要的新功能,向IC、封裝和板

2018-08-28 15:28:45

Cadence設計系統公司發布Cadence?Allegro?系統互連設計平臺針對印刷電路板(PCB)設計進行的全新產品和技術增強.改進后的平臺為約束驅動設計提供了重要的新功能,向IC、封裝和板

2008-06-19 09:36:24

IC設計Cadence 2018設計筆試題Choice Questions1. What is theminimum number of flip flops to implement a

2018-12-28 10:20:26

多視角裸眼3D顯示器技術發展和市場動態

2012-08-17 13:48:00

`FTDI發布支持Android平臺的 USB Host/slave IC--UART GPIO SPI I2C先進的單片USB主控橋接器并支持各種標準接口英商飛特蒂亞公司(FTDI)繼續推進安卓

2013-01-10 17:32:34

`FTDI發布支持Android平臺的 USB Host/slave IC--UART GPIO SPI I2C先進的單片USB主控橋接器并支持各種標準接口英商飛特蒂亞公司(FTDI)繼續推進安卓

2013-01-10 17:43:45

赫、RF與SiP/3D-IC流程。Allegro產品提供了一個可升級的PCB與IC封裝設計解決方案,利用一種約束與規則驅動型方法學,從邏輯設計授權到物理實現再到信號與功率的完整性分析。 最新系統級

2020-07-06 17:50:50

`FTDI發布支持Android平臺的 USB Host/slave IC先進的單片USB主控橋接器并支持各種標準接口英商飛特蒂亞公司(FTDI)繼續推進安卓開源配件的創新,推出FT311D。這款

2013-04-01 18:00:31

`FTDI發布支持Android平臺的 USB Host/slave IC--UART GPIO SPI I2C先進的單片USB主控橋接器并支持各種標準接口英商飛特蒂亞公司(FTDI)繼續推進安卓

2013-03-08 17:18:20

`FTDI發布支持Android平臺的 USB Host/slave IC--UART GPIO SPI I2C先進的單片USB主控橋接器并支持各種標準接口英商飛特蒂亞公司(FTDI)繼續推進安卓

2013-03-08 17:28:32

我用的是cadence 16.3的版本,用Model Integrity這個軟件模塊進行IBIS轉DML時總是報錯,提示無法打開“ibis2signoise”;還有就是查看IBIS文件的曲線時,軟件出錯,然后就自動關閉了。求哪位大神指點迷津。

2011-12-24 13:34:57

://t.elecfans.com/live/1043.html 各位小伙伴大家好,Cadence Allegro 軟件一直以來,都能夠支持3D PCB的模型制作和預覽功能,但是一直以來立體感和視角的效果都不

2019-11-22 13:45:11

本文是電子發燒友學院講師李增老師(@wareleo)經驗分享,希望能與工程師一起交流探討各位小伙伴大家好,Cadence Allegro 軟件一直以來,都能夠支持3D PCB的模型制作和預覽功能

2019-11-22 13:49:25

的錯誤日志 1. iMX8QM安卓平臺支持3D游戲嗎?2. 如果是,是否需要額外添加一些東西才能啟用 3D 游戲?

2023-04-04 07:42:57

當3D電影已成為影院觀影的首選,當3D打印已普及到雙耳無線藍牙耳機,一種叫“3D微波”的技術也悄然而生。初次聽到“3D微波”,你可能會一臉茫然,這個3D微波是應用在哪個場景?是不是用這種技術的微波爐1秒鐘就能把飯煮熟?O M G!我覺得很有必要給大家科普一下!

2019-07-02 06:30:41

(INT8)稠密算力。啟明930可獨立用于AI加速卡,亦可通過D2D擴展多種功能型Side Die進行集成,具備多種產品形態。北極雄芯由清華大學姚期智院士創建的交叉信息核心技術研究院自2018年起孵化

2023-02-21 13:58:08

從最近很多新聞上可以看到,3D打印與醫療和生物行業的結合越來越緊密。醫療行業也在不斷加緊引入全新的3D打印技術來輔助完成各種手術和一些高難度醫學工作。最近,華森科技研發了一款專業適用于醫療行業的3D打印機,誰知道這款醫療3D打印機到底有多厲害嗎?

2019-08-02 07:04:30

本帖最后由 gk320830 于 2015-3-4 19:06 編輯

在cadence ic版圖設計中tsmc.18,寬長比4/0.18的mosfet怎么畫?有多少層?每一層什么意義?

2014-10-06 08:07:57

,降低武器裝備成本,提高維修保障時效性與精度。在世界各國的廣泛關注與大力推進下,近年來3D打印技術的發展與應用不斷取得突破,顯示了良好的軍事應用前景,將對武器裝備的發展產生深遠影響。

2019-07-16 07:06:28

3D 音頻。 OpenSL ES 可在從智能手機和先進移勱設備到上代低端移勱硬件設計中應用。無關于其所部署的平臺,OpenSL ES 提供普適的通用接口 API,從而使任何設備均可達到其硬件支持的最優

2011-03-08 21:41:21

怎么實現基于SL3IC3001芯片的UHF頻段RFID多應用天線的設計?

2021-05-26 06:39:31

本文是電子發燒友學院講師李增老師(@wareleo)經驗分享,希望能與工程師一起交流探討各位小伙伴大家好,Cadence Allegro 軟件一直以來,都能夠支持3D PCB的模型制作和預覽功能

2019-11-21 17:31:52

3D視覺技術有何作用?常見的3D視覺方案主要有哪些?

2021-11-09 07:46:56

3D打印技術是綜合了三維數字技術、控制技術、信息技術眾多技術的創新研發技術,具有設計樣式多元化、試制成本低、制作材料豐富等特點。通過數字化設計工具+3D打印技術相結的模式,可以幫助企業高效實現創新

2021-05-27 19:05:15

的節點。3D封裝引發新的競爭 除了晶體管結構走向了3D以外,封裝技術也在向3D方向發展。有報道指出,用先進封裝技術提供的高密度互聯將多顆Chiplet包在同一個封裝體內,將是未來的發展趨勢。而在這其中

2020-03-19 14:04:57

請問怎樣理解3D ICs技術之變?

2021-06-18 07:20:20

眾所周知,Cadence allegro 16.x 版本已經擁有3D view,雖然比較簡單,但是總之還不錯,近年以來Cadence公司在不斷的加強 PCB Editor三維的顯示能力,可以幫助

2019-06-07 08:00:00

`FTDI發布支持Android平臺的 USB Host/slave IC-UART/I2C/GPIO/SPI先進的單片USB主控橋接器并支持各種標準接口英商飛特蒂亞公司(FTDI)繼續推進安卓開源

2013-06-18 16:52:36

商迪3D

2021-11-22 09:26:58

普密斯3D輪廓測量儀方案 3D GMS Pro,擁有高速移動測量平臺,兼容多類型傳感器,為客戶需求提供快速、強力的技術支持! 產品特點—— 高速移動測量平臺龍門架

2023-07-28 15:42:53

SpringSoft Laker定制版圖系統支持TSMC跨平臺制程設計套件

IC設計軟件全球供貨商SpringSoft, Inc.近日宣布,Laker定制版圖自動化系統(Custom Layout Automation Syste

2009-07-30 08:11:20 1005

1005 本章是Cadence IC 5.1.41 是設計 的簡明入門教程,目的是讓讀者在剛接觸該軟件的時候對它的基本功能有一個總體的了解。本章主要內容如下:[1] 啟動Cadence IC 前的準備;[2]Command Interpret

2011-12-02 16:56:58 158

158 新思科技 (Synopsys)今日宣布利用3D-IC整合技術加速多晶片堆疊系統 (stackedmultiple-die silicon system)的設計

2012-03-28 08:57:44 719

719 全球電子設計創新領先企業Cadence設計系統公司日前宣布TSMC已選擇Cadence解決方案作為其20納米的設計架構。Cadence解決方案包括Virtuoso定制/模擬以及Encounter RTL-to-Signoff平臺。

2012-10-22 16:48:03 909

909 電子發燒友網訊: TSMC授予Cadence兩項年度合作伙伴獎項,兩項大獎表彰Cadence在幫助客戶加快設計的3D-IC CoWoS技術與20納米參考流程方面的重要貢獻。 TSMC授予全球電子設計創新領先企業

2012-11-07 11:48:07 928

928 Cadence教程:基于Cadence的IC設計

2013-04-07 15:46:14 0

0 為專注于解決先進節點設計的日益復雜性,全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS) 今天宣布,臺積電已與Cadence在Virtuoso定制和模擬設計平臺擴大合作以設計和驗證其尖端IP。

2013-07-10 13:07:23 842

842 基于Wide I/O接口的3D堆疊,在邏輯搭載存儲器設計上進行了驗證 ,可實現多塊模的整合。它將臺積電的3D堆疊技術和Cadence?3D-IC解決方案相結合,包括了集成的設計工具、靈活的實現平臺,以及最終的時序物理簽收和電流/熱分析。

2013-09-26 09:49:20 1346

1346 Integrity Solution),提供卓越性能的電源分析以滿足下一代芯片設計的需要。Voltus? IC電源完整性解決方案利用獨特的新技術并結合Cadence? IC、Package、PCB和系統工具使設計團隊在整個產品開發周期更好地管理芯片設計的電源問題,以取得更快的設計收斂。

2013-11-13 16:13:50 1323

1323 7-nm FinFET Plus工藝的極紫外光刻技術,IC Compiler II 進行了專門的優化,進一步節省芯片面積。 采用TSMC的Wafer-on-Wafer(WoW)技術,平臺內全面支持

2018-05-17 06:59:00 4461

4461 關鍵詞:CoWoS , WoW , 先進封裝 新思科技(Synopsys)宣布,新思科技Design Platform全面支持TSMC WoW直接堆疊和 CoWoS先進封裝技術。Design

2018-10-27 22:14:01 346

346 對全新芯片堆疊技術的全面支持確保實現最高性能的3D-IC解決方案

2019-05-18 11:28:01 3642

3642 近日,芯原股份在接受機構調研時表示,Chiplet 帶來很多新的市場機遇,公司作為具有平臺化芯片設計能力的 IP 供應商,已經開始推進對Chiplet的布局,開始與全球領先的晶圓廠展開基于5nm

2021-01-08 12:57:56 2579

2579 業界首款應用于多個小芯片(multi-chiplet)設計和先進封裝的完整 3D-IC平臺。

2021-10-08 10:29:05 970

970 )宣布,其數字和定制/模擬流程已獲得 TSMC N3 和 N4 工藝技術認證,支持最新的設計規則手冊(DRM)。通過持續合作,Cadence 和 TSMC 發布了 TSMC N3 和 N

2021-10-26 15:10:58 1928

1928 新思科技3DIC Compiler是統一的多裸晶芯片設計實現平臺,無縫集成了基于臺積公司3DFabric技術的設計方法,提供完整的“探索到簽核”的設計平臺

2021-11-01 16:29:14 371

371 雙方合作涵蓋新思科技的Interface IP、基于TSMC 3DFabric?的設計解決方案以及針對臺積公司N4制程技術的PPA優化。

2021-11-08 11:54:45 445

445 創建邏輯內存器件的 3D 堆疊配置,優化 3D 堆疊設計的 PPA 結果。 客戶可以放心采用 Cadence Integrity 3D-IC 平臺和 Samsung Foundry 的多 Die 實現

2021-11-19 11:02:24 3347

3347 研討會”。作為 2022 年第一場線下研討會,Cadence將集聚相關軟件開發者與資深技術專家,與各位客戶朋友們分享關于 Cadence 3D-IC Integrity 平臺在統一環境中提供 3D

2022-01-04 08:56:51 1420

1420 電子設計自動化領域領先的供應商 Cadence,誠邀您參加將于2022 年 1 月 20 日于上海浦東嘉里酒店舉辦的“2022 CadenceCONNECT: 3D-IC 設計與全系統解決方案-上海研討會”。

2022-01-20 11:11:42 1533

1533 Chiplet Interconnect Express)產業聯盟。作為中國大陸首批加入該組織的企業,芯原將與UCIe產業聯盟其他成員共同致力于UCIe 1.0版本規范和新一代UCIe技術標準的研究與應用,為芯原Chiplet技術和產品的發展進一步夯實基礎。

2022-04-02 11:47:55 1251

1251 Cadence Integrity 3D-IC 平臺是業界首個全面的整體 3D-IC 設計規劃、實現和分析平臺,以全系統的視角,對芯片的性能、功耗和面積 (PPA) 進行系統驅動的優化,并對 3D-IC 應用的中介層、封裝和印刷電路板進行協同設計。

2022-05-23 16:52:50 1594

1594

基于Cadence的IC設計

2022-05-31 17:11:24 0

0 2.5D/3D-IC 目前常見的實現是基于中介層的 HBM-CPU/SOC 設計,Integrity 3D-IC 將以日和周為單位的手動繞線加速到秒級和分鐘級,輕松滿足性能、信號電源完整性與設計迭代的多重要求,為高帶寬高數據吞吐量的機器學習、超算、高性能移動設備、端計算等應用提供最佳設計支持。

2022-06-13 14:14:54 2037

2037 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence? 射頻集成電路解決方案支持 TSMC 的 N6RF 設計參考流程和制程設計套件(PDK),加速推進移動、5G 及無線應用創新。

2022-06-22 16:34:01 1774

1774 設計。得益于兩家企業的持續合作,使用 Cadence Integrity 3D-IC 平臺的參考流程現已啟用,以推進 Samsung Foundry 的 3D-IC 設計方法。使用 Cadence 平臺

2022-10-25 11:05:04 621

621 包含在臺積電3Dblox Reference Flow中的RedHawk-SC和RedHawk-SC Electrothermal,能夠使用臺積電3DFabric技術實現電源完整性和熱可靠性設計簽核

2022-11-02 14:19:48 461

461 隨著 N3E、N4P 和 3DFabric 工藝的發布,新的獨特設計要求要求進行新的認證,以確保同時滿足設計人員的系統要求和 TSMC 的工藝要求,從而縮短上市時間。

2022-11-07 14:17:59 1080

1080 此次獲獎的 Integrity 3D-IC 平臺是 Cadence 于 2021 年 10 月推出的突破性產品,它是業界首款完整的高容量 3D-IC 平臺,可將設計規劃、物理實現和系統分析統一集成于單個管理界面中。在面向日益復雜的超大規模計算、消費電子、5G 通信、移動和汽車應用設計時

2022-11-11 10:19:49 549

549 、基于云的生產力解決方案和 DSP IP 方面取得的出色成果。此外,Cadence 也被認定為 TSMC 3DFabric 聯盟的創始成員之一。

2022-12-14 11:42:34 1152

1152 不知不覺間,行業文章和會議開始言必稱chiplet —— 就像曾經的言必稱AI一樣。這種熱度對于3D-IC的從業人員,無論是3D-IC制造、EDA、還是3D-IC設計,都是好事。但在我們相信3D-IC之路是Do Right Things的同時,如何Do Things Right也愈發重要。

2022-12-16 10:31:00 808

808 半導體行業中的第一個聯盟,它與合作伙伴聯手加速3D IC生態系統的創新和準備,為半導體設計、內存模塊、襯底技術、測試、制造和封裝提供全方位的最佳解決方案和服務。這一聯盟將幫助客戶快速實現硅和系統級的創新,并利用臺積電的3DFabric技術(一個全面的3D硅堆疊

2022-12-19 17:57:02 662

662 聯華電子(NYSE:UMC;TWSE:2303)與楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日共同宣布,采用 Integrity 3D-IC 平臺的 Cadence 3D-IC 參考工作流程已通過聯電的芯片堆棧技術認證,將進一步縮短產品上市時間。

2023-02-03 11:02:23 1417

1417 Cadence 的低功耗、3D-IC 和人工智能 / 機器學習(AI / ML)技術可支持超大規模計算的數據之旅 —— 從存儲和傳輸,到傳感器和設備的數據處理要求;從近 / 遠邊緣處理,到本地云數據中心的工作負載優化計算。

2023-02-21 18:16:42 618

618 臺積電 3DFabric? CoWoS-S 硅中介層技術實現,可提供超高的帶寬密度、高效的低功耗性能和卓越的低延遲,非常適合需要極高算力的應用。Cadence UCIe IP 為Chiplet裸片到裸片通信

2023-04-27 16:35:40 453

453

該 IP 采用臺積電 3DFabric? CoWoS-S 硅中介層技術實現,可提供超高的帶寬密度、高效的低功耗性能和卓越的低延遲

2023-04-28 15:14:12 811

811 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布推出基于 Cadence Integrity 3D-IC 平臺的新設計流程,以支持 TSMC 3Dblox 標準。TSMC

2023-05-09 09:42:09 615

615 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 數字和定制/模擬設計流程已通過 TSMC N3E 和 N2 先進工藝的設計規則手冊(DRM)認證。兩家公司還發

2023-05-09 10:09:23 708

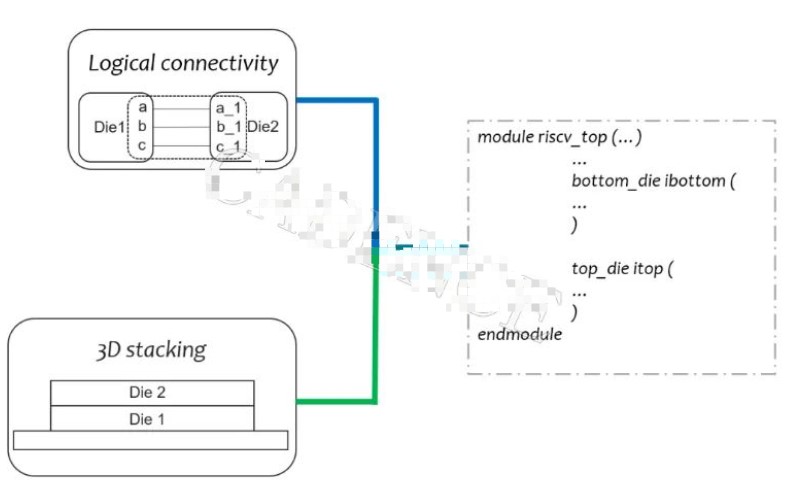

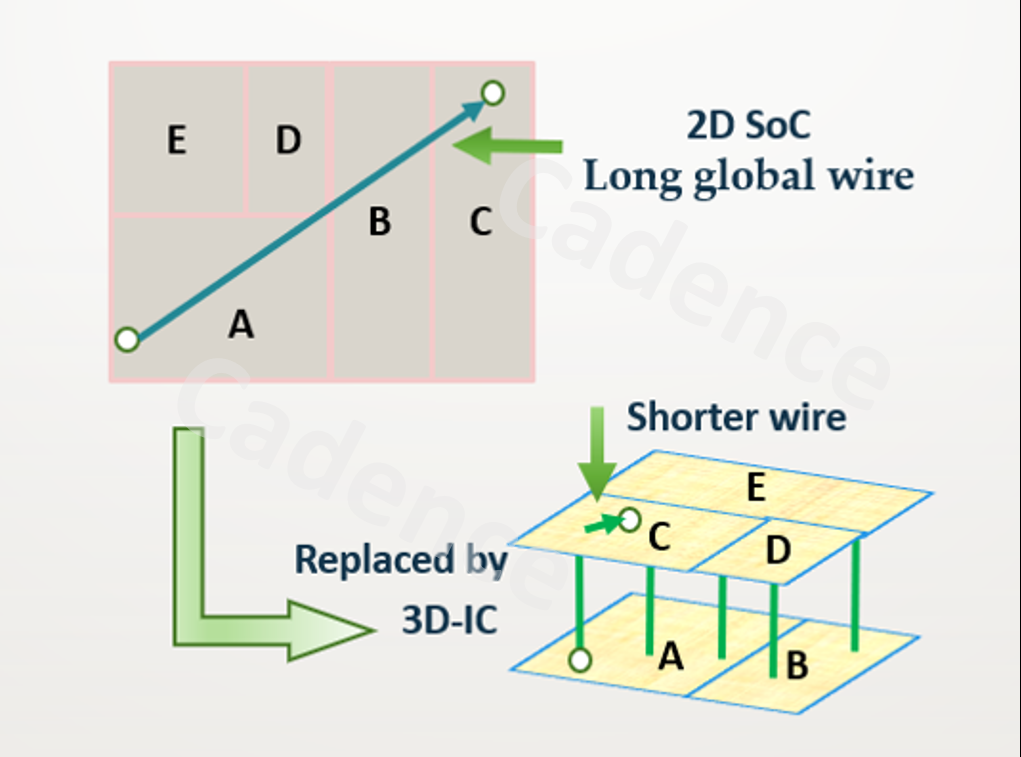

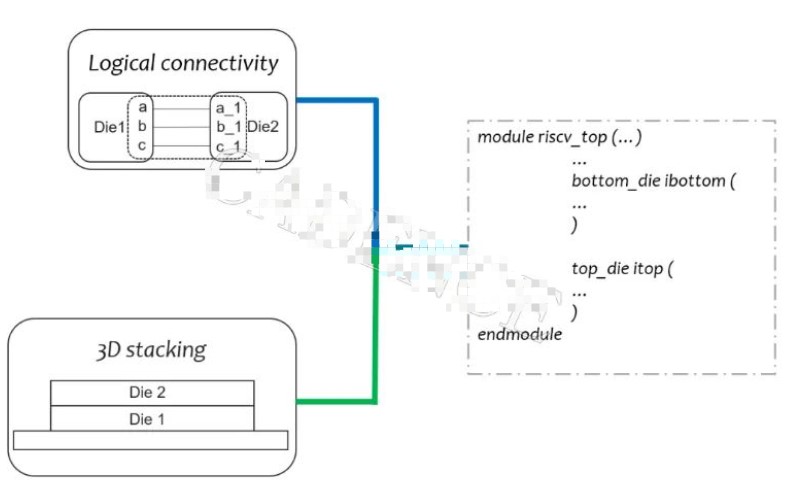

708 隨著業界對增加晶體管密度、增加帶寬和降低功耗的需求越來越迫切,許多IC設計和封裝團隊都在深入研究如何增加垂直堆疊多個芯片裸片(die)和小芯片(chiplet)的方案。這種被稱為3D-IC的技術有望

2022-01-06 14:05:18 249

249

本文作者:許立新Cadence公司DSGProductValidationGroup隨著3D-IC的制造工藝的不斷發展,3D-IC的堆疊方式愈發靈活,從需要基板作為兩個芯片互聯的橋梁,發展到如今可以

2022-07-24 16:25:41 491

491

平臺支持 Samsung 新的 3D CODE 標準,助力設計人員創建多種先進的封裝技術。 ?? Cadence 和 Samsung 的技術為客戶提供全面、定制化的解決方案。適用于能夠縮短 3D-IC

2023-07-06 10:05:04 329

329 ● AI 驅動的 Cadence Virtuoso Studio 助力 IC 設計在 TSMC 的制程技術之間實現遷移時自動優化電路 ●? 新的生成式設計技術可將設計遷移時間縮短

2023-09-27 10:10:04 301

301 內容提要 ●? Cadence Integrity 3D-IC 平臺現已全面支持最新版 3Dblox 2.0 標準,涵蓋 TSMC 的 3DFabric 產品 ●? Integrity 3D-IC

2023-10-08 15:55:01 249

249 基于Cadence的IC設計

2022-12-30 09:21:19 6

6 3D-IC 中 硅通孔TSV 的設計與制造

2023-11-30 15:27:28 212

212

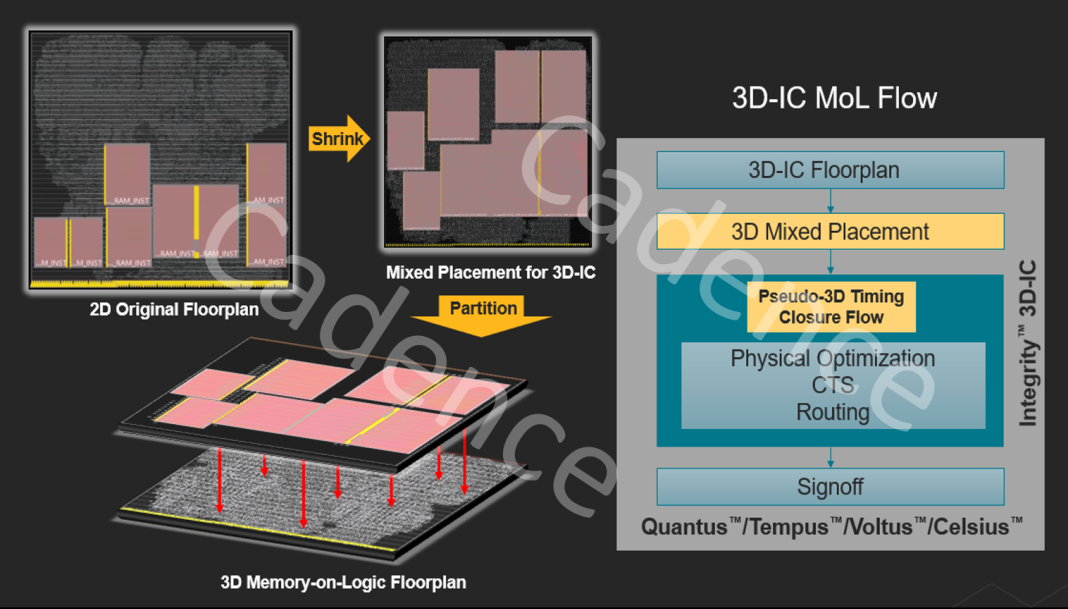

3D-IC 設計之 Memory-on-Logic 堆疊實現流程

2023-12-01 16:53:37 255

255

3D-IC 設計之早期三維布圖綜合以及層次化設計方法

2023-12-04 16:53:58 200

200

Chiplet,又稱芯片堆疊,是一種模塊化的半導體設計和制造方法。由于集成電路(IC)設計的復雜性不斷增加、摩爾定律的挑戰以及多樣化的應用需求,Chiplet技術應運而生。

2024-01-23 10:49:37 351

351

Cadence Allegro? X APD(用以實現元件布局、信號/電源/接地布線、設計同步電氣分析、DFM/DFA及最后制造輸出)、Integrity? 3D-IC Platform 及其對應的Integrity System Planner(負責系統級設計聚合、規劃和優化)

2024-03-13 10:05:40 130

130 本文要點縮小集成電路的總面積是3D-IC技術的主要目標。開發3D-IC的傳熱模型,有助于在設計和開發的早期階段應對熱管理方面的挑戰。開發3D-IC傳熱模型主要采用兩種技術:分析法和數值計算法。傳統

2024-03-16 08:11:28 52

52

電子發燒友App

電子發燒友App

評論