一千多年前,詩人李白創作了豪放灑脫、氣勢磅礴的《蜀道難》,并發出了“蜀道難,難于上青天”的感慨。從長安到巴蜀之地,要穿越秦嶺和大巴山,山高谷深,道路崎嶇,極為艱險!我雖沒有李白“筆落驚風雨,詩成泣鬼神”般的才華,但想借用李白的詩句來表達芯片設計之難,從某種角度來說,芯片設計是真的“難于上青天”!

難點之一——設計具有競爭力的高性能芯片

以個人計算機中的CPU為例,其全球市場幾乎被AMD和英特爾瓜分。在消費電子領域,高性能就是絕對的競爭力,這在AMD和英特爾幾十年的競爭歷史上得到了完美的證明。一方的性能如果能全面超越另一方,那么其市場占有率就會發生明顯的變化。

比如,AMD在2003年推出的基于K8微架構的64位速龍處理器,因其強悍的性能成為高端游戲玩家的主流配置。其市場份額也在逐年攀升,甚至在桌面CPU領域的市占率一度超過英特爾,但隨后英特爾憑借酷睿CPU重新奪回市場。

AMD和英特爾之間的競爭如“神仙打架”一般,鮮有第三家公司能擠進這個領域。這是因為AMD和英特爾擁有最優秀的架構師,架構設計思想經過多年的市場驗證及迭代,始終走在領域的最前沿。

從前端設計的角度看,頂級芯片設計公司在芯片性能(Performance)、功耗(Power)、面積(Area)方面都做到了極致,后來者恐怕難以望其項背!

難點之二——為芯片設計新功能

業內的多數芯片都有著成熟的設計方案,并且新產品都是基于上一代項目的迭代而誕生的,芯片設計過程相對容易。如果為了解決一個新的問題或者適應新的使用場景,從頭開始設計一款芯片,那么難度會直線上升。

首先要考慮如何設計架構,實現新的功能;其次要考慮如何用硬件描述語言實現架構師的想法,以及如何在有限的硬件資源條件下盡可能提高性能。這些問題都非常考驗工程師的技術實力。

難點之三——芯片驗證

事實上,驗證工程師承受著非常大的壓力,因為面對功能復雜的芯片,保證覆蓋率達標是一件非常困難的事情。在流片之后,如果芯片沒有成功點亮,驗證工程師也會挺身而出,與硅后工程師一起完成芯片的調試工作。在實際的芯片項目中,找到芯片設計中一個相對隱晦的錯誤并不容易。

難點之四——可測性設計和測試

在可測性設計中,業界通常要求固定型故障的測試覆蓋率要達到99%或者99.5%,甚至更高。在超大規模的芯片中,邏輯設計極為復雜,邏輯深度大,很多電路難以被控制和觀測,盡管有EDA工具作為輔助,但要達到目標并不容易。

在我初入職場時,公司領導曾給我講了一個故事:多年之前,一位工程師在芯片測試階段遇到了一個棘手的問題,耗費一個月的時間仍沒有任何進展,在巨大的壓力和挫敗感下,這位工程師趴在測試機上痛哭,讓人頗為唏噓。

拋開技術不談,芯片設計需要投入大量資金,流片費用高昂,是一個名副其實的“燒錢”的行業。如果沒有資金注入,就好比“巧婦難為無米之炊”,寸步難行。

2021年4月21日,在芯片界的頂級會議Hot?Chips大會上,Cerebras Systems公司發布了一款晶圓級引擎芯片——Wafer Scale Engine 2。這款芯片采用臺積電7納米工藝制程,擁有85萬個AI核心,包含2.6萬億個晶體管,面積為46225平方毫米,基于一整張12英寸的晶圓制造,這是迄今為止包含晶體管數量最多的芯片 。

除了這款“巨無霸”,市面上主流的用在智能手機或者個人電腦中的芯片,其晶體管規模都在百億級。那么數量如天文數字般的晶體管,是如何被設計出來的呢?

“上百億個晶體管,總不能用手來畫吧?”相信很多非業內人士會有類似的困惑。

其實在集成電路發展早期,內部的晶體管都是通過手畫設計的,彼時芯片的規模較小,只有幾十個或者幾百個晶體管。但隨著芯片的發展和演進,其邏輯功能變得越來越復雜且全面,晶體管的數目也呈指數級增長,此時再徒手畫電路,顯然是不現實的。隨后,計算機輔助設計開始應用于芯片領域。在直接促成百億級規模的芯片設計這一方面,有三種秘密武器必不可少。

秘密武器之一——使用編程語言來設計芯片的思想

這個思想來自卡沃·米德和林恩·康威的著作《超大規模集成電路系統導論》,它的提出是芯片設計歷史上一個非常重要的里程碑。

假設我們要設計一個數據比較器,當輸入值a和b相等時,equal的返回值為1;當a和b不相等時,返回值為0。使用Verilog語言,一行代碼即可實現。

assign?equal = (a==b)? 1 : 0;

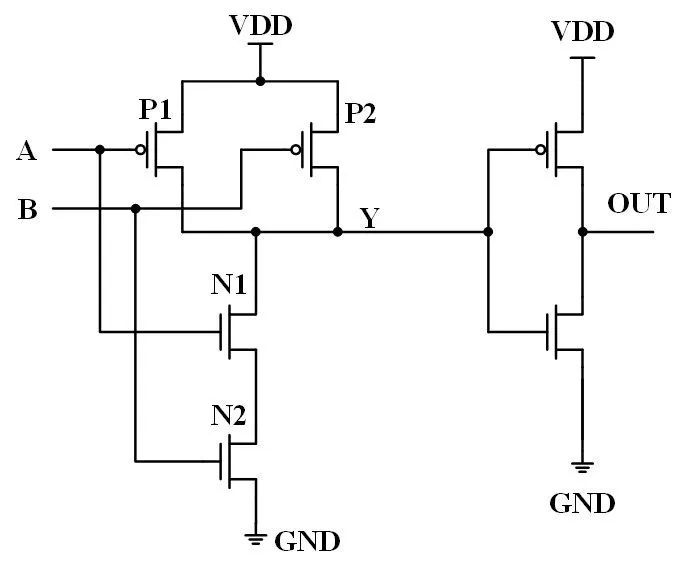

但如果徒手畫晶體管電路,通過分析以上數據比較器的功能可知,邏輯功能和同或門一致,因此可以用異或門后接一個反相器實現該數據比較器的功能。搭建一個異或門最少需要6個晶體管,一個反相器需要2個晶體管,所以我們用一行代碼就完成了8個晶體管的設計,這大幅提高了工程師設計芯片的效率!

這是數字芯片設計中最簡單的一個例子,在實際工作中,工程師可以在比較抽象的層次上描述設計電路的結構和邏輯功能,用簡潔明確的源代碼描述復雜的邏輯功能,并且支持模塊化設計和層次化設計。往往由簡單的幾十行代碼設計出來的電路,即可包含成千上萬個晶體管。因此,通過編程可以讓設計具有百億級數量晶體管的芯片成為可能。

秘密武器之二——EDA

在 RTL 設計完成后,即可采用邏輯綜合工具把RTL 轉換成門級網表,也就是與、或、非等邏輯門及其之間的連接關系。將RTL 轉換成門級網表的過程主要有三個步驟:翻譯、優化和映射。就像自動化流水線一樣,只要把原材料放進去,就可以得到成品。這些紛繁復雜的工作都交給EDA來做,可以明顯縮短設計的時間,加快將芯片推向市場的速度。

秘密武器之三——重復調用已有的成熟設計模塊

在芯片中,很多單元或模塊的數目不止用到一次,比如算術邏輯單元,我們只需設計一次,即可重復調用。這好比建筑師在設計住宅樓時,只需設計幾種標準戶型,并不要求每間房屋的戶型都是獨一無二的設計。或者從更高層次的角度看,目前的中央處理器都是8核、16核等,這些核心在設計上也幾乎是一致的。

盡管芯片設計工程師被認為是硬件工程師,但編程是芯片設計工程師必不可少的技能之一,也正是編程思想賦予了芯片設計無限的可能。

本文節選自一本“嚴(專)肅(業)的”芯片科普圖書——《了不起的芯片》。

作者王健,筆名“溫戈”,畢業于西安電子科技大學,曾就職于全球頂級芯片測試公司Teradyne,現為某芯片大廠數字芯片設計經理。成功參與多款高性能CPU、GPU、服務器等超大規模SoC芯片產品的流片。在芯片設計、可測性設計、芯片測試及應用開發等領域具有豐富的實戰經驗。

知乎平臺芯片(集成電路)、中央處理器(CPU)話題優秀答主,數碼鹽究員。騰訊新聞特約撰稿人,四川衛視《了不起的分享》節目嘉賓,微信公眾號“OpenIC”主理人。累計創作內容高達百萬字,涉及科技熱點解讀、芯片科普、技術分享、職場成長等主題,深受讀者好評,全網關注人數超過30萬,閱讀量過億。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論