芯片作為現代電子產品的核心部件,一直充當著“大腦”的位置,其技術含量和資金極度密集,生產線動輒數十億上百億美金。 ? 芯片制造的完整過程包括:芯片設計、晶圓制造、封裝、測試等幾個主要環節,其中每個環節都是技術和科技的體現。 ? 對于芯片來說設計和工藝同樣復雜,八十年代EDA技術誕生——芯片自動化設計,使得芯片設計以及超大規模集成電路的難度大為降低,工程師只需將芯片的功能用芯片設計語言描述并輸入電腦,再由EDA工具軟件將語言編譯成邏輯電路,然后再進行調試即可,正如編輯文檔需要微軟的office,圖片編輯需要photoshop一樣,芯片開發者利用EDA軟件平臺來進行電路設計、性能分析到生成芯片電路版圖。現在的一塊芯片有上百億個晶體管,不依靠EDA工具,高端芯片設計根本無從下手。你細品,這么浩瀚的工程怎么能靠手動完成呢? ? 重點是盡管有了EDA也并不代表芯片設計這件事很容易,芯片設計仍然是一個集高精尖于一體的復雜系統工程。

圖片來自網絡,侵刪

不管是IDM還是fabless,共同的特點是以芯片設計為產業的核心。舉個例子,2018年AMD的處理器改由臺積電代工,制程為7nm,英特爾的處理器制程還是14nm,但性能照樣壓制了AMD,說明芯片設計也是非常關鍵的鴨。 ? 設計一款芯片,開發者先要明確需求,確定芯片“規范”,定義諸如指令集、功能、輸入輸出管腳、性能與功耗等關鍵信息,將電路劃分成多個小模塊,清晰地描述出對每個模塊的要求。 ? 然后由“前端”開發者根據每個模塊功能設計出“電路”,運用計算機語言建立模型并驗證其功能準確無誤。“后端”開發者則要根據電路設計出“版圖”,將數以億計的電路按其連接關系,有規律地翻印到一個硅片上。 ? 至此,芯片設計才算完成。如此復雜的設計,不能有任何缺陷,否則無法修補,必須從頭再來。如果重新設計加工,一般至少需要一年時間,再投入上千萬美元的經費,有時候甚至需要上億。 ? 敲黑板,戴眼鏡,既然大家普遍對芯片制造的難度有一定的了解,那這篇文章希望可以讓大家對芯片設計的難度也有共同的認知。 ? ?

1

第一關,難在架構設計

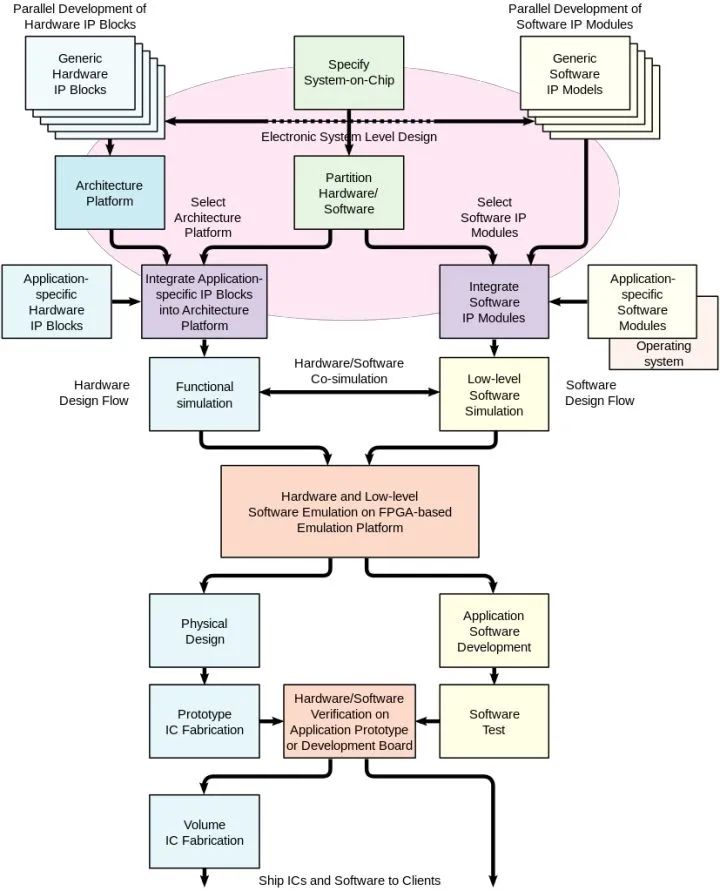

芯片設計,環節眾多,每個環節都面臨很多挑戰。以相對較為簡單的數字集成電路設計為例設計多采用自頂向下設計方式,層層分解后包括: ? 需求定義:結合外部環境分析、供應鏈資源、公司自身定位等信息,提出對新一代產品的需求,并進一步考慮產品作用、功能、所需線板數量、使用集成電路類型等,精準定義產品需求。這一環節的難度在于對市場、技術的未來趨勢準確判斷和對設計人員、制造工廠等自身和產業鏈情況、能力的充分了解。 ? 功能實現:描述芯片需要實現的目標,通常用硬件描述語言編寫。這一環節的難度在于對芯片整體可以達到的性能、功能的把握,既要充分滿足目標,又不能超過自身的能力上限。

圖片源網絡,侵刪

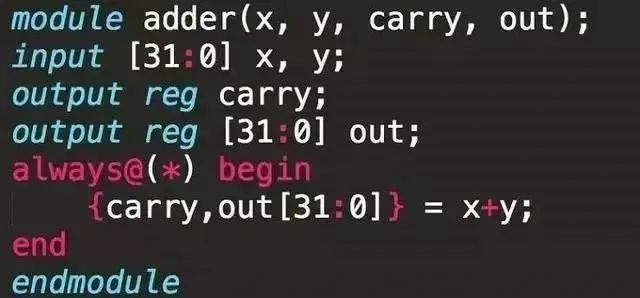

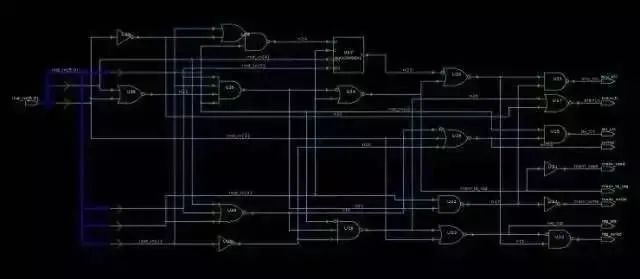

結構設計:根據芯片的特點,將其劃分成接口清晰、相互關系明確、功能相對獨立的子模塊。這一環節難度在于對芯片結構的熟悉,是否能用盡可能少的模塊和盡可能低的標準達到要求。 ? 邏輯綜合:開發者將硬件描述語言轉換成邏輯電路圖。這一環節難度在于需要保證代碼的可綜合、清晰簡潔、可讀性,有時還要考慮模塊的復用性。

圖源網絡,侵刪

物理實現:將邏輯電路轉換成為有物理連接的電路圖。這一環節難度在于如何根據制程,使用盡可能少的元件和連線完成從RTL描述到綜合庫單元之間的映射,得到一個在面積和時序上滿足需求的門級網表,并使內部互不干擾。 ? 物理版圖:以 GDSII 的文件格式交給晶圓廠,在硅片上做出實際的電路,再進行封裝和測試,得到物理芯片。 ? 必須說明的是,芯片設計時,需要考慮許多變量,例如信號干擾、發熱分布等,而芯片的物理特性,如磁場、信號干擾,在不同制程下有很大不同,沒有數學公式可以直接計算,也沒有可套用的經驗數據直接填入,只能依靠EDA工具一步一步設計,一步步模擬,不斷取舍。每一次模擬之后,如果效果不理想,就要重新設計一次,對團隊的智慧、精力、耐心都是極大考驗。

2

第二關,難在驗證

芯片驗證目標是在芯片制造之前,通過檢查、仿真、原型平臺等手段反復迭代驗證,提前發現系統軟硬件功能錯誤、優化性能和功耗,使設計精準、可靠,且符合最初規劃的芯片規格。 ? 它不是在設計完成后再進行的工序,而是貫穿在設計的每一個環節中的重復性行為,可細分為系統級驗證、硬件邏輯功能驗證、混合信號驗證、軟件功能驗證、物理層驗證、時序驗證等。

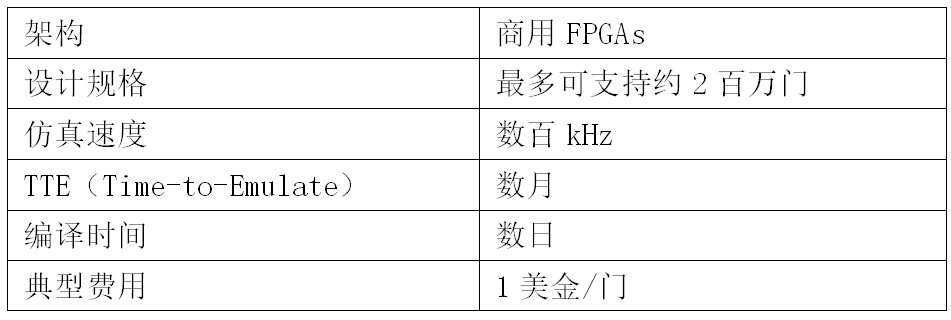

驗證很難,首先在驗證只能證偽,需要反復考慮可能遇到的問題,以及使用形式化驗證等手段來保證正確的概率,非常考驗設計人員的經驗和智慧。 ? 其次在驗證的方法必須盡可能高效。現在的芯片集成了微處理器、模擬IP核、數字IP核和存儲器(或片外存儲控制接口),驗證復雜度指數級增長。如何快速、準確、完備、易調試地完成日益復雜的驗證,進入流片階段,是每個芯片設計人員最大的挑戰。 ? 最后在驗證工具本身。以常見的FPGA硬件仿真驗證為例,90年代FPGA驗證最多可支持200萬門,每門的費用為1美元。如今單位價格雖然大幅下降,隨著芯片的復雜程度指數級增長,驗證的門數也上升到以千萬和億為計算的規模,總體費用更加驚人。

圖源網絡,侵刪

此外,FPGA本身也是芯片設計的一種。現在大型設計(大于2千萬等效ASIC門)需要用多塊FPGA互聯進行驗證,FPGA的設計面對RTL邏輯的分割、多片FPGA之間的互聯拓撲結構、I/O分配、布局布線、可觀測性等現實要求,這就又給設計環節增加了難度。 ? ?

3

第三關,難在流片

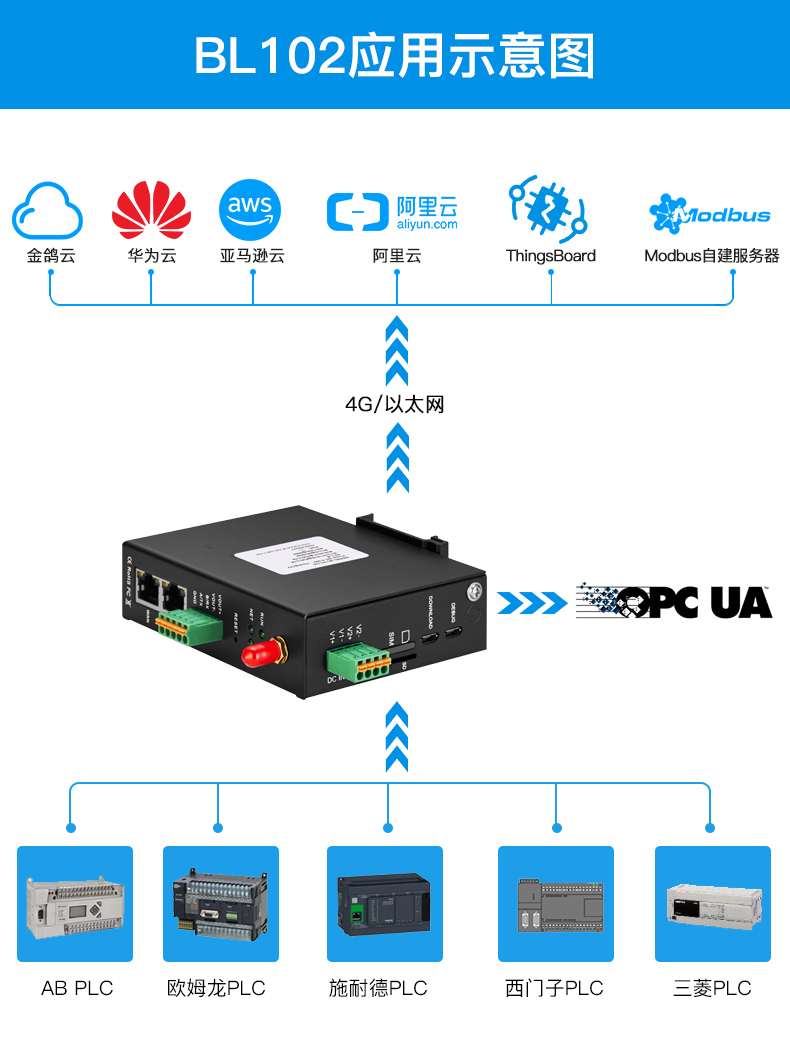

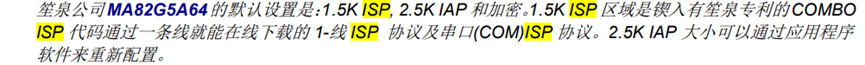

流片就是試生產,設計完后,由芯片代工廠小批量生產一些,供測試用。它看起來是芯片制造,但實際屬于芯片設計行業。 ? 流片技術上不困難,因為芯片設計基于現有工藝,除了少量需要芯片設計企業指導的生產之外,困難在于錢、錢、錢。 ? 流片一次有多貴?先引用CMP(Circuits Multi-Projets,美國一家非營利性多項目晶圓服務組織)的公開報價吧。

圖片來自CMP報價表

按照這份報價,以業內裸芯(die)面積最小的處理器高通驍龍855為例(尺寸為8.48毫米×8.64毫米,面積為73.27平方毫米),用28納米制程流片一次的標準價格為499,072.5歐元,也就是近400萬元人民幣! ? 然后,芯片設計企業可以拿到什么呢?25個裸芯,平均每個16萬元! ? 更重要的是,流片根本不是一次性的事啊! ? 流片失敗,需要修改后再次流片;流片成功,可能需要繼續修改優化,二次改進后再次流片。 ? 每一次都需要至少幾百萬元。 ? 什么叫做氪金?這才叫做氪金啊! ? 或許有知友會提出疑問,這是成本上的問題,為什么算在困難上呢?這當然是困難了,世界上最大的困難不就是沒錢嗎? ? 之所以在會提到流片費用,是因為許多人在談及芯片制造困難的時候都會指出,建立一條先進制程芯片產線需要天量資金投入,但通過流片可以看出,其實芯片設計對資金的渴求也同樣驚人。

4

第四關,越來越具有挑戰性的設計需求

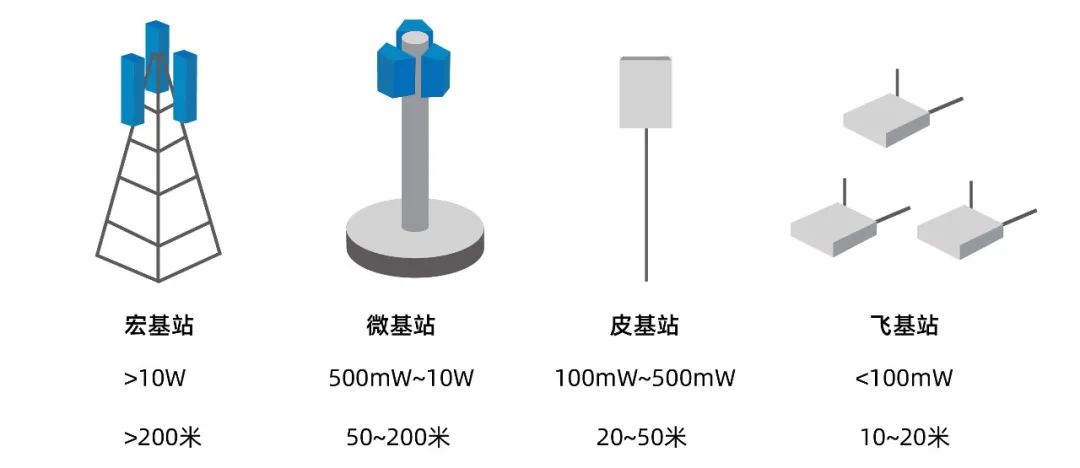

首先是隨著芯片使用場景延伸至AI、云計算、智能汽車、5G等領域,芯片的安全性、可靠性變得前所未有的重要,對芯片設計提出更高、更嚴格的要求。 ? 其次是隨著AI、智能汽車等領域快速發展,帶來專用芯片和適應行業需求的全新架構需求,這一全新的課題給芯片設計帶來更多新的挑戰。 ? 最后是隨著硅基芯片根據摩爾定律,在兩三年之后將達到1納米的工藝極限,繼續提升性能、降低功耗的重任更多落在芯片設計身上,給芯片設計更大的壓力。此外,制程工藝提升也迫切需要芯片設計的指導才能實現,也額外增加了壓力。

編輯:黃飛

電子發燒友App

電子發燒友App

評論