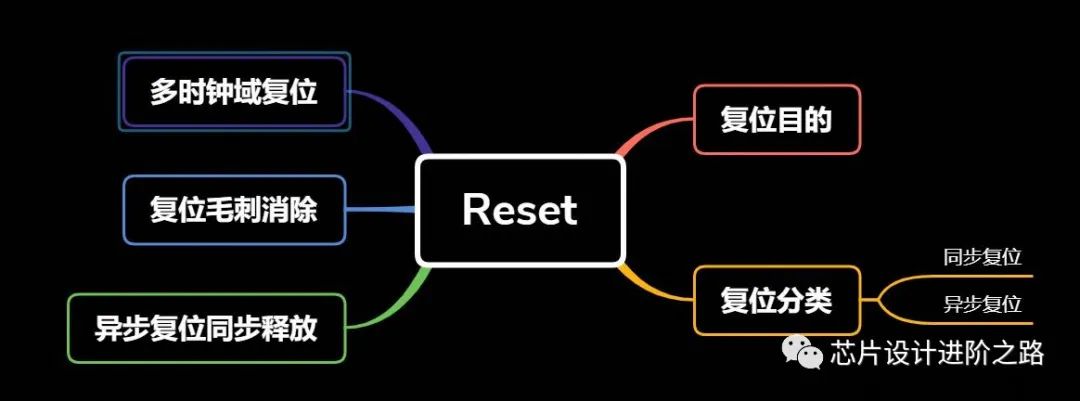

首先上思維導(dǎo)圖:

如果要問“芯片中怎么復(fù)位才對(duì)?”

很多人都會(huì)回答“異步復(fù)位同步釋放”。

但是為什么要用異步復(fù)位同步釋放,是不是所有的芯片都必須采用這種方式,估計(jì)很少人能回答上來。那么讓我們從為什么要復(fù)位開始。

1. 復(fù)位的目的

復(fù)位信號(hào)在數(shù)字電路里面的重要性僅次于時(shí)鐘信號(hào)。對(duì)一個(gè)芯片來說,復(fù)位的主要目的是使芯片電路進(jìn)入一個(gè)已知的,確定的狀態(tài)。主要是觸發(fā)器進(jìn)入確定的狀態(tài)。在一般情況下,芯片中的每個(gè)觸發(fā)器都應(yīng)該是可復(fù)位的。在某些情況下,當(dāng)在高速應(yīng)用程序中使用流水線觸發(fā)器(移位寄存器觸發(fā)器)時(shí),為了實(shí)現(xiàn)更高的性能設(shè)計(jì),可能會(huì)從某些觸發(fā)器中消除復(fù)位。這種類型設(shè)計(jì)需要在復(fù)位激活期間,運(yùn)行預(yù)先確定數(shù)量的時(shí)鐘周期,以使ASIC處于已知的狀態(tài)。

1.1 為什么需要復(fù)位呢?

1)復(fù)位可以使電路從確定的初始狀態(tài)開始運(yùn)行:

上電復(fù)位:上電的時(shí)候,為了避免上電后進(jìn)入隨機(jī)狀態(tài)而使電路紊亂,這個(gè)時(shí)候就需要上電復(fù)位。

中間復(fù)位:有時(shí)候,要求電路從初始狀態(tài)開始執(zhí)行電路的功能,要對(duì)電路進(jìn)行復(fù)位,讓它從最初的狀態(tài)開始運(yùn)行。

- 復(fù)位可以使電路從錯(cuò)誤狀態(tài)回到可以控制的確定狀態(tài):

如果電路發(fā)生了異常,比如狀態(tài)不正常,中斷異常,firmware程序跑飛,這個(gè)時(shí)候就可以對(duì)電路進(jìn)行復(fù)位,讓它從錯(cuò)誤的狀態(tài)回到一個(gè)正常的狀態(tài)。

- 電路仿真時(shí)需要電路具有已知的初始值

在仿真的時(shí)候,信號(hào)在初始狀態(tài)是未知狀態(tài)(也就是所謂的x,不過對(duì)信號(hào)初始化之后的這種情況除外,因?yàn)榉抡娴臅r(shí)候?qū)π盘?hào)初始化就使信號(hào)有了初始值,這就不是x了)。

對(duì)于數(shù)據(jù)通路(數(shù)字系統(tǒng)一般分為數(shù)據(jù)通路和控制通路,數(shù)據(jù)通路一般是對(duì)輸入的數(shù)據(jù)進(jìn)行處理,控制通路則是對(duì)運(yùn)行的情況進(jìn)行操作),在實(shí)際電路中,只要輸入是有效數(shù)據(jù)(開始的時(shí)候可能不是有效的),輸出后的狀態(tài)也是確定的;在仿真的時(shí)候,也是輸入數(shù)據(jù)有效了,輸出也就確定了。也就是說,初始不定態(tài)對(duì)數(shù)據(jù)通路的影響不明顯。

對(duì)于控制通路,在實(shí)際電路中,只要控制通路完備(比如說控制通路的狀態(tài)機(jī)是完備的),即使初始狀態(tài)即使是不定態(tài),在經(jīng)過一定的循環(huán)后,還是能回到正確的狀態(tài)上;然而在仿真的時(shí)候就不行了,仿真的時(shí)候由于初始狀態(tài)為未知態(tài),控制電路一開始就陷入了未知態(tài);仿真跟實(shí)際電路不同,仿真是“串行”的,仿真時(shí)控制信號(hào)的初始不定態(tài)會(huì)導(dǎo)致后續(xù)的控制信號(hào)結(jié)果都是不定態(tài),也就是說,初始的不定態(tài)對(duì)控制通道是致命的。

1.2 不需要復(fù)位的情況

復(fù)位信號(hào)很重要,但是并不是每一部分的電路都需要復(fù)位電路,一方面是復(fù)位電路也消耗邏輯資源、占用芯片面積,另一方面是復(fù)位信號(hào)會(huì)增加電路設(shè)計(jì)的復(fù)雜性(比如要考慮復(fù)位的策略、復(fù)位的布局布線等等)。

當(dāng)某個(gè)電路的輸出在任何時(shí)刻都可以不受到復(fù)位信號(hào)的控制就有正確的值時(shí),比如說數(shù)據(jù)通路中的對(duì)數(shù)據(jù)進(jìn)行處理的部分。在某些情況下,當(dāng)流水線的寄存器(移位寄存觸發(fā)器)在高速應(yīng)用中時(shí),應(yīng)該去掉某些寄存器的復(fù)位信號(hào)以使設(shè)計(jì)達(dá)到更高的性能,因?yàn)閹?fù)位的觸發(fā)器比不帶復(fù)位的觸發(fā)器更復(fù)雜,反應(yīng)也更慢。

2. 同步復(fù)位

2.1 同步復(fù)位的實(shí)現(xiàn)方式

同步復(fù)位的前提是,復(fù)位信號(hào)只會(huì)在時(shí)鐘的有效邊沿去影響或者復(fù)位flip-flop。Reset可以作為組合邏輯的一部分送給FF的D端。這種情況下,編碼方式必須是if/else 優(yōu)先級(jí)的方式,而且reset只能放在if條件下,其他組合邏輯放到else邏輯下。

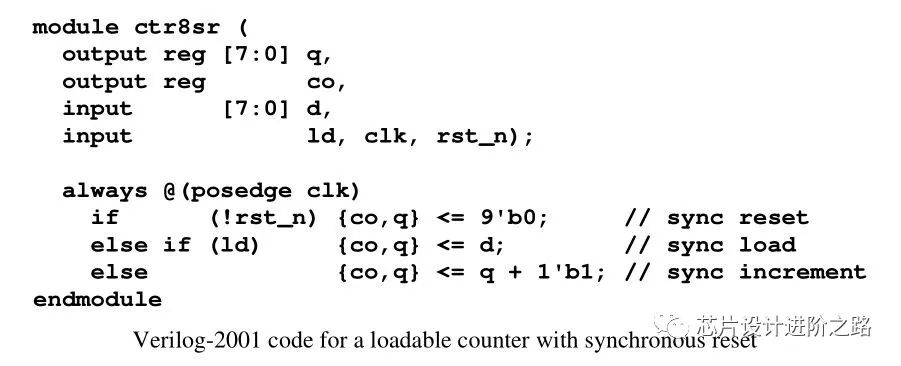

正確的方式去構(gòu)建同步復(fù)位FF的verilog代碼如下:

如果沒有嚴(yán)格遵守這種方式,會(huì)有兩個(gè)問題:

1、一些仿真器中,基于邏輯方程,邏輯可能組織復(fù)位到達(dá)觸發(fā)器。這只是一個(gè)仿真問題,不是硬件問題。但是復(fù)位的一個(gè)主要目的,就是仿真的時(shí)候?qū)㈦娐分糜谝粋€(gè)已知的確定狀態(tài)。

2、由于復(fù)位樹的高扇出,復(fù)位信號(hào)可能是一個(gè)相對(duì)于時(shí)鐘周期的“延遲到達(dá)信號(hào)”,盡管復(fù)位將從復(fù)位緩沖區(qū)樹中進(jìn)行緩沖,但明智的做法是限制復(fù)位到達(dá)本地邏輯后必須經(jīng)過的邏輯量。就是說必須對(duì)復(fù)位信號(hào)少做邏輯。

下面的列子是一個(gè)同步復(fù)位的,帶進(jìn)位的計(jì)數(shù)器(loadable counter with synchronous reset)

它的電路圖如下:

圖1 Loadable counter with synchronous reset

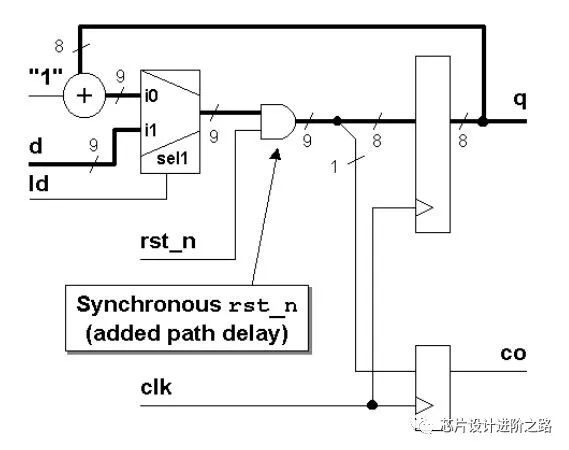

同步復(fù)位的有一個(gè)問題就是,綜合工具不能很好的把reset信號(hào)和其他的信號(hào)區(qū)分開。比如上面的電路也可能被綜合成另外的電路,如下所示:

圖2 Loadable counter with synchronous reset style 2

圖1和圖2是完全相同的。唯一的區(qū)別是圖2的reset信號(hào)被提前到了MUX之前。通過rst_n拉低,可以強(qiáng)制MUX的兩個(gè)分支的輸入為0,但是如果ld是未知的(X),并且MUX模型是悲觀的,則會(huì)保持未知(X) 不會(huì)被復(fù)位。注意,這只是在仿真過程中出現(xiàn)的問題! 實(shí)際的電路可以工作正確并將其重置為0。

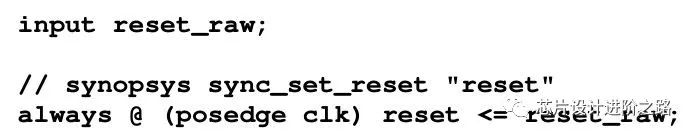

Synopsys提供編譯器指令sync_set_reset,該指令告訴綜合工具給定信號(hào)是同步reset(or set)。合成工具將這個(gè)信號(hào)“拉”到盡可能接近觸發(fā)器,防止這種初始化問題的發(fā)生:

// synopsys sync_set_reset "rst_n"

這個(gè)命令只會(huì)影響綜合,不會(huì)影響邏輯行為,所以推薦在同步復(fù)位每個(gè)模塊都加上這個(gè)信號(hào)。

另外,可以在讀取RTL之前將合成變量hdlin_ff_always_sync_set_reset設(shè)置為-true,這樣就可以得到相同的結(jié)果,而不需要在代碼本身中執(zhí)行任何指令。

2.2 同步復(fù)位的優(yōu)點(diǎn)和缺點(diǎn)

同步復(fù)位的優(yōu)點(diǎn)如下

(1) 同步復(fù)位會(huì)綜合成更小的觸發(fā)器,特別當(dāng)reset生成邏輯電路作為觸發(fā)器D輸入,但是這種情況下組合邏輯電路的數(shù)量變多,所以總的門電路節(jié)省不是那么顯著。

(2) 同步復(fù)位確保電路100%是同步的。

(3) 同步復(fù)位確保復(fù)位只發(fā)生在時(shí)鐘有效邊沿,對(duì)小的復(fù)位毛刺來說,時(shí)鐘就像濾波器。

(4) 在一些設(shè)計(jì)中,復(fù)位必須由內(nèi)部條件產(chǎn)生。同步復(fù)位能過濾時(shí)鐘間邏輯等式的毛刺。

(5) 通過使用同步重置和預(yù)先確定的時(shí)鐘數(shù)量作為復(fù)位過程的一部分。可以在復(fù)位緩沖區(qū)樹中使用觸發(fā)器,來幫助將緩沖樹的時(shí)序保持在一個(gè)時(shí)鐘周期以內(nèi)。

同步復(fù)位的缺點(diǎn)如下:

(1) 不是所有的庫(kù)都有自帶同步reset的FF, 但是可以通過把reset當(dāng)作數(shù)據(jù)輸入來解決;

(2) 同步復(fù)位需要一個(gè)脈沖延伸器保證復(fù)位脈沖足夠?qū)挘軌虮挥行r(shí)鐘沿采集到;特別是在多時(shí)鐘設(shè)計(jì)中;

(3) 同步復(fù)位電路必須要有一個(gè)時(shí)鐘來復(fù)位。如果用門控時(shí)鐘來省電,那么沒有時(shí)鐘的時(shí)候就不能復(fù)位;

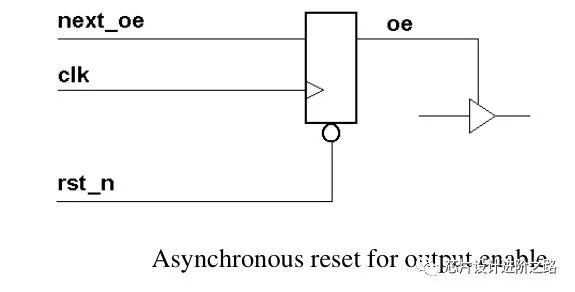

(4) 如果電路中有三態(tài)總線,那么上電時(shí)必須用異步復(fù)位,如果用同步復(fù)位,reset必須能夠復(fù)位三態(tài)信號(hào)的enable信號(hào)。如下所示

3. 異步復(fù)位

3.1 異步復(fù)位的實(shí)現(xiàn)

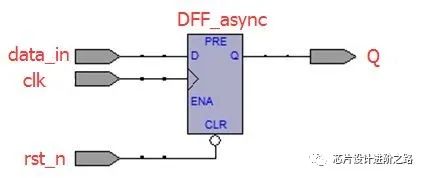

異步復(fù)位觸發(fā)器則是在設(shè)計(jì)觸發(fā)器的時(shí)候加入了一個(gè)復(fù)位引腳,也就是說復(fù)位邏輯集成在觸發(fā)器里面。(一般情況下)低電平的復(fù)位信號(hào)到達(dá)觸發(fā)器的復(fù)位端時(shí),觸發(fā)器進(jìn)入復(fù)位狀態(tài),直到復(fù)位信號(hào)撤離。帶異步復(fù)位的觸發(fā)器電路圖和RTL代碼如下所示:

關(guān)于異步復(fù)位的綜合約束,推薦將輸入reset設(shè)置為

set_ideal_network + false path

3.2 異步復(fù)位的優(yōu)點(diǎn)

1.異步復(fù)位的最大優(yōu)點(diǎn)是,vendor庫(kù)里面有異步復(fù)位FF, 這樣datapath就十分干凈。不用把reset與數(shù)據(jù)做邏輯,這樣復(fù)位路徑上就不會(huì)有額外的延時(shí),也不會(huì)受外部信號(hào)的干擾。

異步復(fù)位的進(jìn)位計(jì)數(shù)器如下:

綜合后的電路如下:

可以看到,reset路徑上十分干凈,直接由外部pin來控制,不受其他信號(hào)影響。

2.異步復(fù)位的另一個(gè)優(yōu)點(diǎn)是電路reset和時(shí)鐘無關(guān),不管有沒有時(shí)鐘,都可以reset。好處是可以實(shí)時(shí)復(fù)位,也可以加在門控時(shí)鐘里面。門控時(shí)鐘是低功耗設(shè)計(jì)的重要方法。

3.異步復(fù)位不需要加入綜合指令,綜合工具就能自動(dòng)識(shí)別。

3.3 異步復(fù)位的缺點(diǎn)

1.異步重置的最大問題是它們是異步的,在復(fù)位階段和解復(fù)位階段(復(fù)位撤離)都是異步的。復(fù)位階段不是問題,解復(fù)位才是問題。如果在觸發(fā)器的活動(dòng)時(shí)鐘邊緣或附近釋放異步復(fù)位,則觸發(fā)器的輸出可能變?yōu)閬喎€(wěn)態(tài),這樣電路的復(fù)位狀態(tài)可能會(huì)丟失,解復(fù)位失敗。

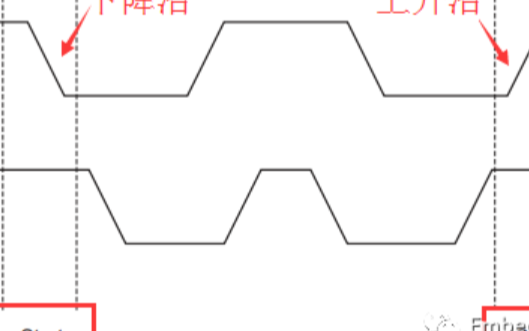

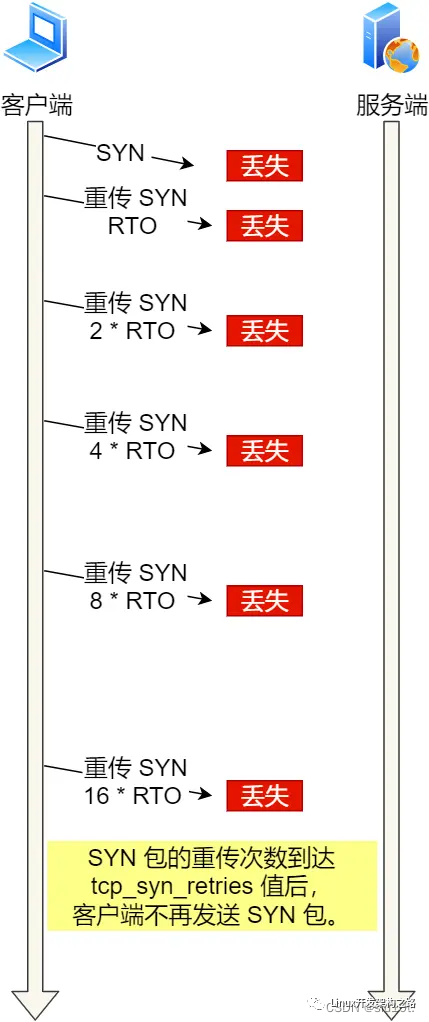

如下圖所示, 異步復(fù)位信號(hào)復(fù)位解除時(shí)是和時(shí)鐘信號(hào)完全異步的。

這種情況下有兩個(gè)問題:(1)復(fù)位恢復(fù)時(shí)間(reset recovery time) 違例

(2) 復(fù)位解除(reset removal) 發(fā)生在不同的觸發(fā)器的不同時(shí)鐘周期

下面先解釋一下兩個(gè)概念:復(fù)位恢復(fù)時(shí)間(reset recovery time)和復(fù)位解除時(shí)間(reset removal time)

復(fù)位恢復(fù)時(shí)間: 解除復(fù)位信號(hào)時(shí),復(fù)位邊沿(當(dāng)然是從有效變成無效的跳變時(shí)刻,通常是0->1那個(gè)時(shí)間點(diǎn))與下一個(gè)有效時(shí)鐘沿之間的這段時(shí)間。對(duì)應(yīng)建立時(shí)間

復(fù)位解除時(shí)間: 解除復(fù)位信號(hào)時(shí),復(fù)位邊沿與上一個(gè)有效時(shí)鐘沿之間的這段時(shí)間。對(duì)應(yīng)保持時(shí)間

異步復(fù)位的復(fù)位信號(hào)必須滿足一定的恢復(fù)時(shí)間和解除時(shí)間,否則沒法確定時(shí)鐘沿是否起作用了,即判斷不了到時(shí)是復(fù)位了還是沒復(fù)位。D觸發(fā)器如果不復(fù)位,那么輸出就是輸入的數(shù)據(jù)。

1). 不滿足復(fù)位恢復(fù)時(shí)間或者撤離時(shí)間,可能會(huì)導(dǎo)致亞穩(wěn)態(tài)問題。(注意是可能)因?yàn)槿绻敵霰旧砭褪菑?fù)位后的值,即使當(dāng)前時(shí)鐘沿不能判斷是否復(fù)位,輸出也是復(fù)位值,這時(shí)候就不會(huì)產(chǎn)生亞穩(wěn)態(tài),因?yàn)橐呀?jīng)是復(fù)位態(tài)了。

2). 不滿足復(fù)位恢復(fù)時(shí)間或者撤離時(shí)間可能會(huì)導(dǎo)致不同F(xiàn)F復(fù)位狀態(tài)不一致的問題。復(fù)位信號(hào)和時(shí)鐘信號(hào)一樣,通過復(fù)位網(wǎng)絡(luò)到達(dá)各個(gè)觸發(fā)器。復(fù)位網(wǎng)絡(luò)具有非常大的扇出和負(fù)載,到達(dá)不同的觸發(fā)器存在不同的延時(shí),不滿足復(fù)位恢復(fù)或者解除時(shí)間的情況下,就有可能在不同的觸發(fā)器的不同時(shí)鐘周期內(nèi)進(jìn)行解復(fù)位。注意,這里的假設(shè)條件是復(fù)位樹和時(shí)鐘樹已經(jīng)做成立平衡狀態(tài),不再考慮復(fù)位樹和時(shí)鐘樹沒做好的情況。

既然同步復(fù)位和異步復(fù)位都有問題,那么到底應(yīng)該怎么復(fù)位呢?能不能即有同步復(fù)位和異步的優(yōu)點(diǎn),而沒有同步復(fù)位和異步復(fù)位的缺點(diǎn)呢?小孩子才做選擇,成年人就是我都要。所以解決方案就是: 異步復(fù)位同步釋放。

4. 異步復(fù)位同步釋放

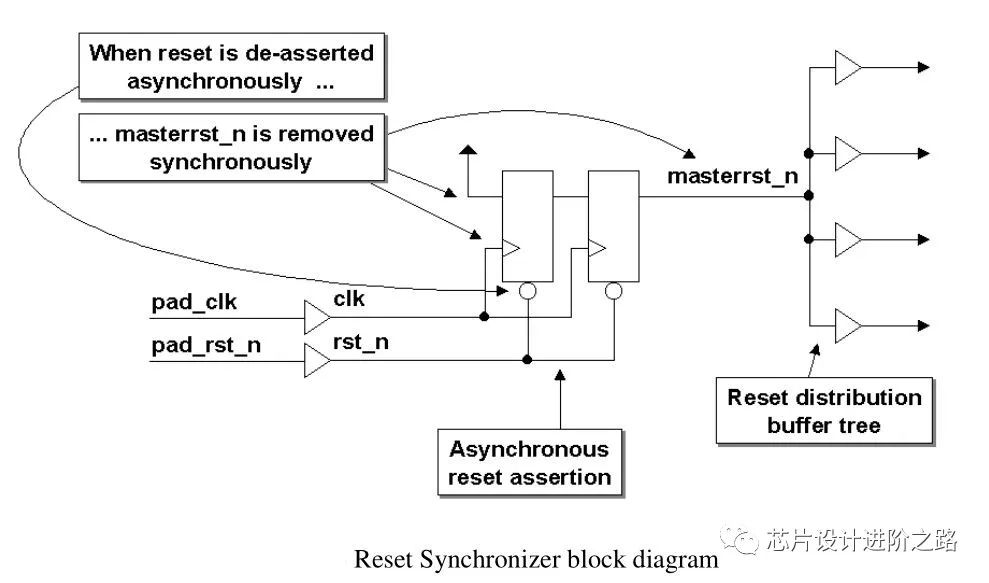

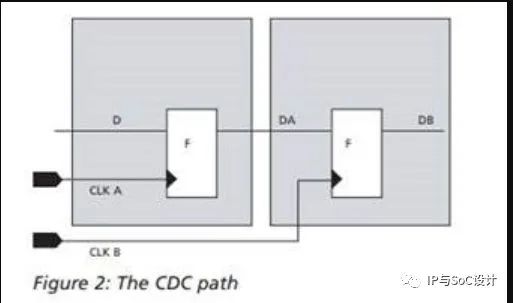

異步復(fù)位的同步釋放電路也稱為復(fù)位同步器。

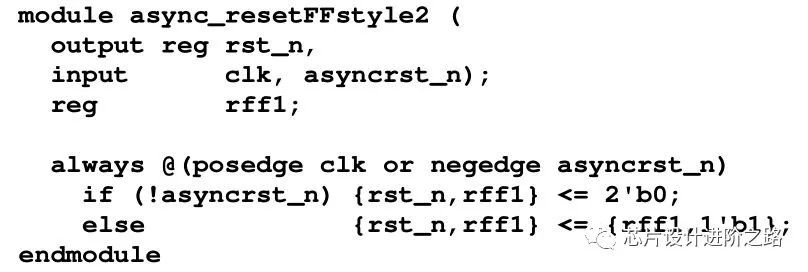

規(guī)則:每個(gè)異步復(fù)位的電路,必須包含一個(gè)復(fù)位同步器。代碼和電路如下:

復(fù)位和解復(fù)位都是通過pad_rst_n來實(shí)現(xiàn)的,第一級(jí)FF的輸入是拉成高(固定為“1”),第二級(jí)的FF用來消除解復(fù)位時(shí)可能帶來的的亞穩(wěn)態(tài)。

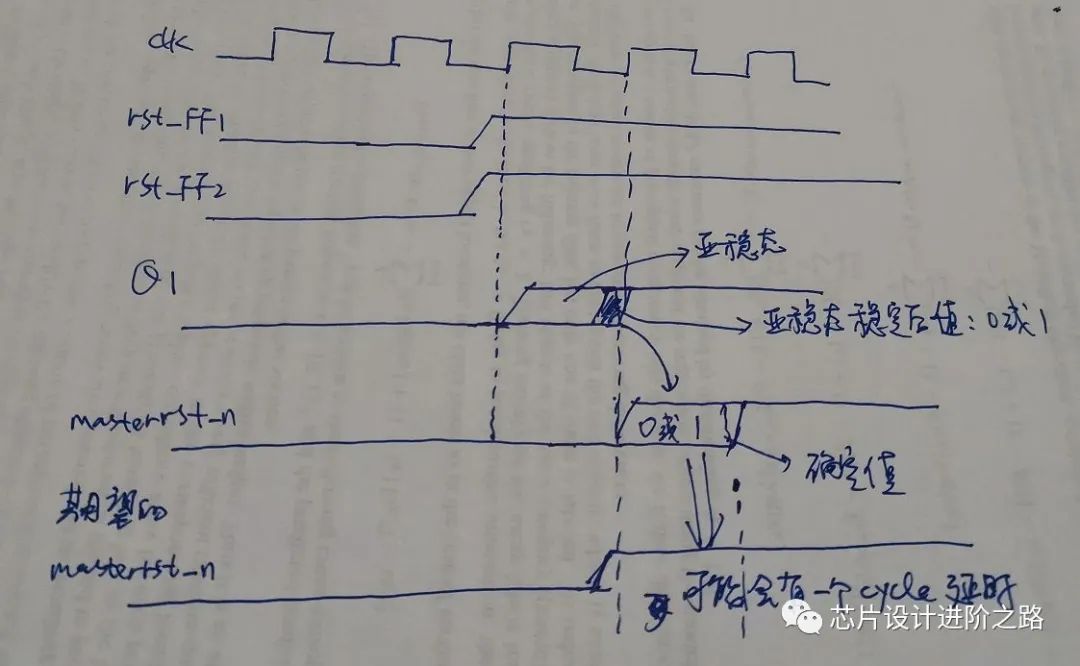

為什么兩級(jí)FF就不會(huì)出現(xiàn)亞穩(wěn)態(tài)呢?第一級(jí)FF輸入是1, 輸出的reset值是0,而reset又是異步的,如果reset剛好在clock邊沿附近,就會(huì)出現(xiàn)亞穩(wěn)態(tài)。

但是加上了第二級(jí)FF就不會(huì)出現(xiàn)亞穩(wěn)態(tài)。這是因?yàn)榈诙?jí)的FF的輸入比第一個(gè)FF延時(shí)了一個(gè)cycle,這樣第一個(gè)FF在解復(fù)位時(shí)候,即使有亞穩(wěn)態(tài),那么也只是影響下一個(gè)周期的Q1輸出,下一個(gè)周期Q1可能為0也可能為1,但是當(dāng)前Q1還是為低(0), 因?yàn)檫@時(shí)第一個(gè)FF還是復(fù)位狀態(tài)。這樣第二個(gè)FF當(dāng)前周期的輸入是0,復(fù)位輸出也是0,所以能不能復(fù)位成功都不會(huì)改變輸出為0,即當(dāng)前周期不會(huì)產(chǎn)生亞穩(wěn)態(tài)。下一個(gè)周期的Q1輸出雖然可能是0也可能是1,但是已經(jīng)穩(wěn)定,是一個(gè)確定的值,所以第二個(gè)FF輸出也是穩(wěn)定的值。如下圖所示:

(手畫的,見諒)

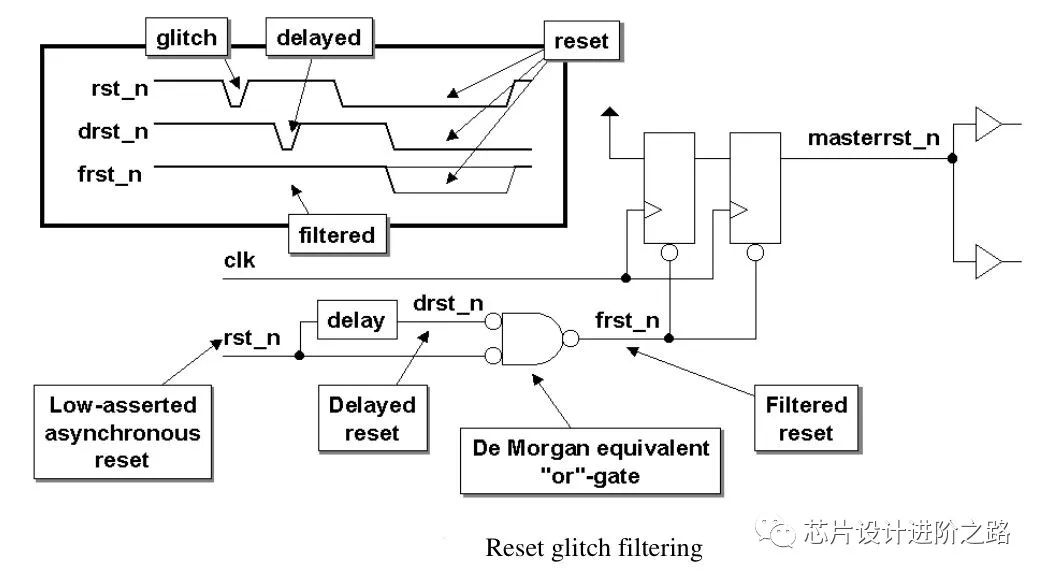

5.異步復(fù)位的抖動(dòng)或毛刺

由于異步復(fù)位和時(shí)鐘無關(guān),任何一個(gè)毛刺都可以引起復(fù)位。這是一個(gè)reset源的問題。下面的電路可以過濾毛刺,主要原理是把輸入源與上它的延時(shí)來消除毛刺。

但是這并不是一個(gè)很完美的設(shè)計(jì),主要原因是delay單元的實(shí)現(xiàn),因?yàn)椴煌瑴囟炔煌瞥滔拢琩elay值可能會(huì)不同。

有的庫(kù)里面包含Delay宏,有的沒有;沒有的話就需要手動(dòng)增加delay或者插buffer,同時(shí)增加約束讓delay不被綜合掉。

同時(shí)rst_n 輸入也必須是一個(gè)史密斯觸發(fā)器pad,進(jìn)一步消除抖動(dòng)。

并不是所有的系統(tǒng)都需要增加防抖,要根據(jù)應(yīng)用范圍來判斷。

6. 復(fù)位樹

復(fù)位樹和時(shí)鐘樹一樣應(yīng)該引起重視,因?yàn)榈湫偷臄?shù)字電路中,reset的負(fù)載和clock的負(fù)載數(shù)量一般是相當(dāng)?shù)摹2还苁峭綇?fù)位還是異步復(fù)位,對(duì)復(fù)位樹都是有時(shí)序要求的。一個(gè)典型的復(fù)位樹如下圖所示:

時(shí)鐘分布樹和重置分布樹之間的一個(gè)重要區(qū)別是時(shí)鐘樹需要緊密平衡分布重置之間的偏差(skew)。與時(shí)鐘信號(hào)不同,只要與復(fù)位信號(hào)相關(guān)的延遲足夠短,允許在一個(gè)時(shí)鐘周期內(nèi)傳播所有復(fù)位負(fù)載,并且仍然滿足所有目標(biāo)寄存器和觸發(fā)器的恢復(fù)時(shí)間,那么復(fù)位信號(hào)之間的偏差(skew)就不是關(guān)鍵。

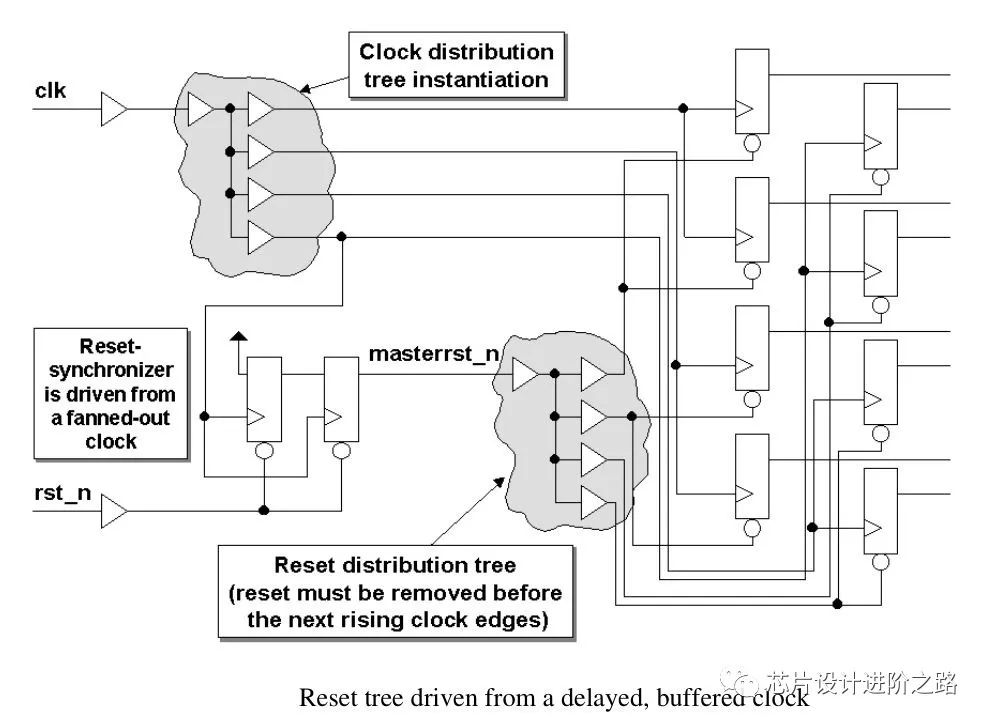

另外一個(gè)需要考慮的問題是,時(shí)鐘樹和復(fù)位樹之間的關(guān)系。到底用那個(gè)時(shí)鐘來驅(qū)動(dòng)復(fù)位樹的FF呢?如果能夠用分支clock來驅(qū)動(dòng)master reset的FF那最好了,但是在大多數(shù)情況下,沒有足夠的時(shí)間讓時(shí)鐘脈沖遍歷時(shí)鐘樹、時(shí)鐘復(fù)位驅(qū)動(dòng)觸發(fā)器,然后讓復(fù)位遍歷復(fù)位樹,所有這些都在一個(gè)時(shí)鐘周期內(nèi)完成。這種情況如下圖所示:

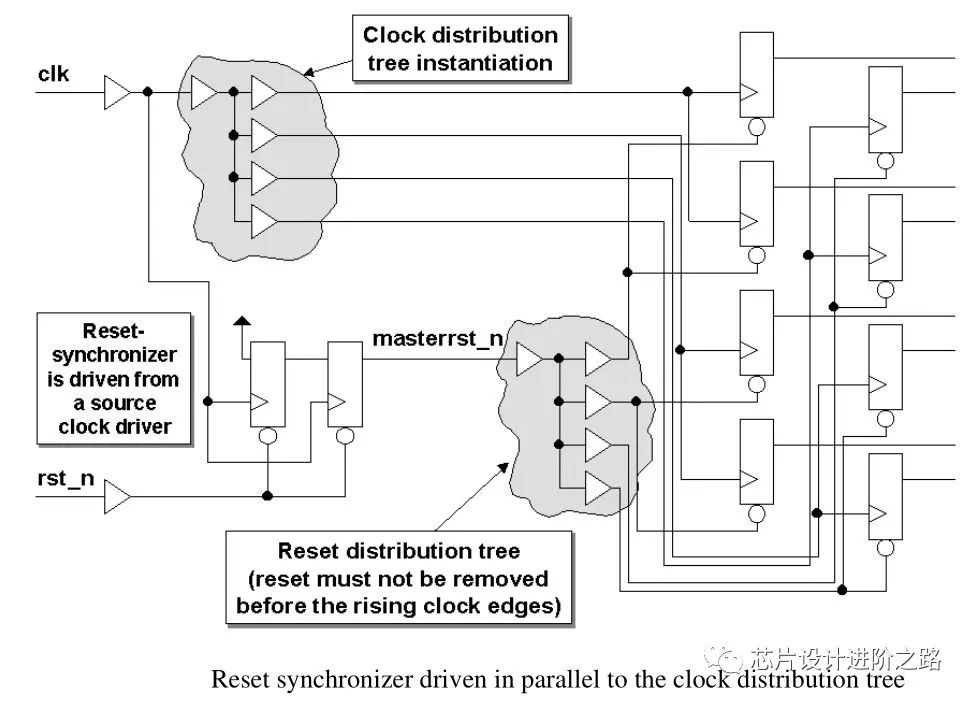

為了能讓reset到達(dá)所有邏輯的速度更快,更好的方式是用一個(gè)更早的clock來驅(qū)動(dòng)reset ff,即用源時(shí)鐘來驅(qū)動(dòng)。必須進(jìn)行Post layout timing分析,以保證復(fù)位同步器的FF不會(huì)出現(xiàn)setup/hold違例。通常情況下,兩個(gè)tree之間詳細(xì)的時(shí)序調(diào)整必須等到layout完成才能進(jìn)行。電路結(jié)構(gòu)如下圖所示:

上述的復(fù)位樹對(duì)同步復(fù)位樹和異步復(fù)位樹都是適用的。

6.1 同步復(fù)位樹

對(duì)同步復(fù)位,一種技術(shù)是通過插入FF來實(shí)現(xiàn)復(fù)位樹。這樣的好處是,reset不需要在一個(gè)時(shí)鐘周期內(nèi)到達(dá)所有的FF。所以需要幾個(gè)時(shí)鐘才能把整個(gè)設(shè)計(jì)復(fù)位掉。每個(gè)模塊都需要包含如下代碼:

同步復(fù)位時(shí)鐘樹如下所示:

采用這種技術(shù),同步復(fù)位信號(hào)可以像其他數(shù)據(jù)信號(hào)一樣處理,設(shè)計(jì)中每個(gè)模塊的timing分析都很容易,復(fù)位樹的每個(gè)階段都有合理的扇出。

6.2 異步復(fù)位樹

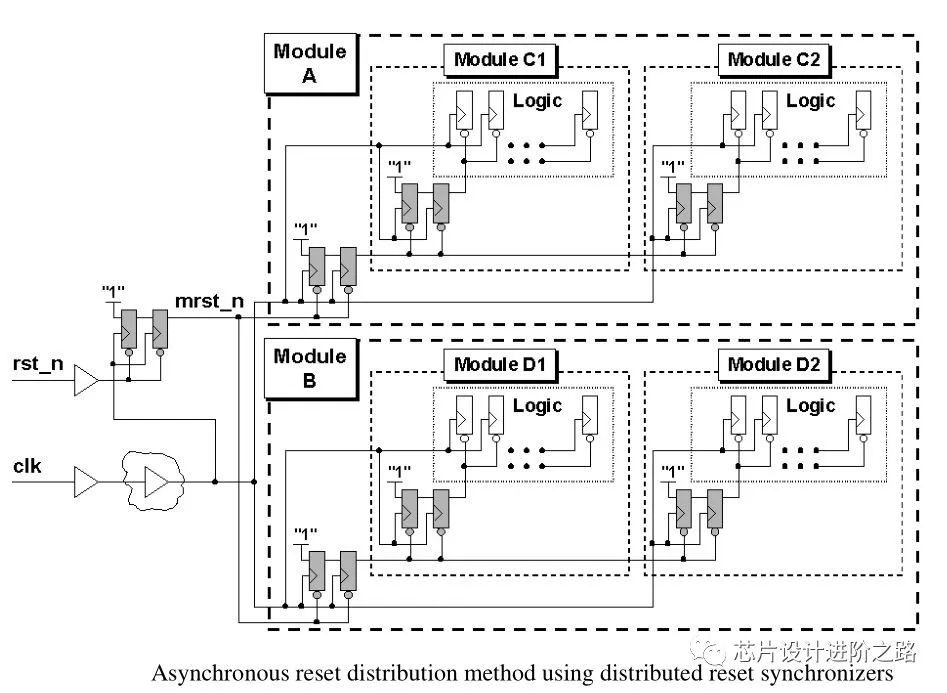

對(duì)異步復(fù)位,是通過復(fù)位同步器來完成復(fù)位樹的建立。即每個(gè)層級(jí)都加上一個(gè)異步復(fù)位同步器。如下圖所示:

異步復(fù)位樹和同步復(fù)位樹有點(diǎn)相似,但是這里的異步復(fù)位同步器是兩級(jí)的FF。這種異步復(fù)位樹,復(fù)位時(shí)可以所有的FF都同時(shí)復(fù)位,但是解復(fù)位必須要幾個(gè)cycle才能完成。

這種結(jié)構(gòu)的問題就是,不同層級(jí)解復(fù)位的時(shí)間點(diǎn)可能是不一樣的。如果設(shè)計(jì)要求整個(gè)芯片在同一個(gè)cycle來解復(fù)位,那么就需要對(duì)復(fù)位同步器做平衡設(shè)計(jì),保證到達(dá)每個(gè)復(fù)位終點(diǎn)是同一個(gè)時(shí)鐘。同步時(shí)鐘樹也存在這個(gè)問題。

使用這種結(jié)構(gòu)的好處是,不用等到P&R之后才去手動(dòng)調(diào)整timing,完全可以交給綜合工具(DC/PT)去插入buffer。

在使用異步重置時(shí),至關(guān)重要的是,設(shè)計(jì)人員要在DC和PT中使用設(shè)置為適當(dāng)設(shè)置的適當(dāng)變量,以確保從復(fù)位同步觸發(fā)器的q-output驅(qū)動(dòng)的異步復(fù)位得到緩沖(如果需要的話)和timed。有關(guān)這些設(shè)置的詳細(xì)信息可以在SolvNet文章#901989[43]中找到。文章指出,DC和PT都可以并且將時(shí)間按照本地時(shí)鐘進(jìn)行異步復(fù)位輸入,如果設(shè)置了以下變量:

這些設(shè)置應(yīng)該是Synopsys的默認(rèn)設(shè)置(只要確保它們是環(huán)境設(shè)置)。正確設(shè)置這些標(biāo)志和使用分布式復(fù)位同步器后,就可以不用類似時(shí)鐘樹去構(gòu)建緩沖復(fù)位樹了。

7. 多時(shí)鐘域復(fù)位

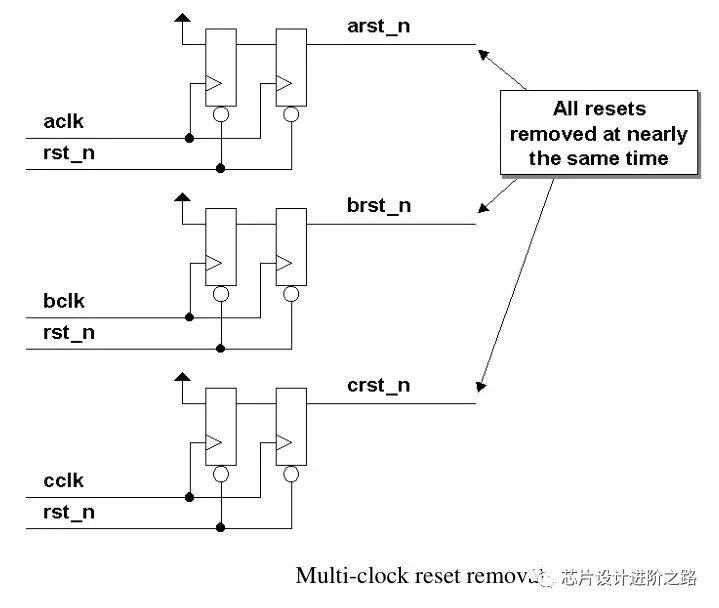

對(duì)于多時(shí)鐘域的設(shè)計(jì),每個(gè)時(shí)鐘域必須有自己?jiǎn)为?dú)的復(fù)位同步器和分布式復(fù)位樹。這樣才能保證reset能滿足不用時(shí)鐘域的reset recovery time。如下圖所示:

對(duì)于多個(gè)時(shí)鐘域的解復(fù)位順序有兩種情況:

1)大部分多時(shí)鐘域的設(shè)計(jì),解復(fù)位的順序并沒有特殊要求。即當(dāng)前時(shí)鐘域解復(fù)位的時(shí)間點(diǎn),在另一個(gè)時(shí)鐘域的精確時(shí)間點(diǎn)并不重要。通常來說,跨時(shí)鐘域的設(shè)計(jì),本身就會(huì)帶來延時(shí)的不確定性。這種情況下,上面的單獨(dú)建立不同時(shí)鐘域的復(fù)位結(jié)構(gòu)就足夠了。

2)有些多時(shí)鐘設(shè)計(jì),復(fù)位解除必須按順序進(jìn)行。這種設(shè)計(jì),可以使用優(yōu)先級(jí)的復(fù)位結(jié)構(gòu)如下所示:

這種結(jié)構(gòu),除了最高優(yōu)先級(jí)的同步器輸入是 tied 1, 其他的輸入都是上一優(yōu)先級(jí)的輸出。

8. 異步復(fù)位的DFT

在做DFT的時(shí)候,如果異步復(fù)位信號(hào)不能直接被I/O引腳驅(qū)動(dòng),就必須將異步復(fù)位信號(hào)和后面的的被驅(qū)動(dòng)電路斷開,用來保證DFT掃描和測(cè)試能夠正確進(jìn)行。兩個(gè)同步復(fù)位觸發(fā)器不應(yīng)該包含在掃描鏈種,需要手動(dòng)測(cè)試。

本文作者:烓圍瑋未。 主要從事ISP/MIPI/SOC/車規(guī)芯片設(shè)計(jì)

首發(fā)于知乎專欄:芯片設(shè)計(jì)進(jìn)階之路

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論