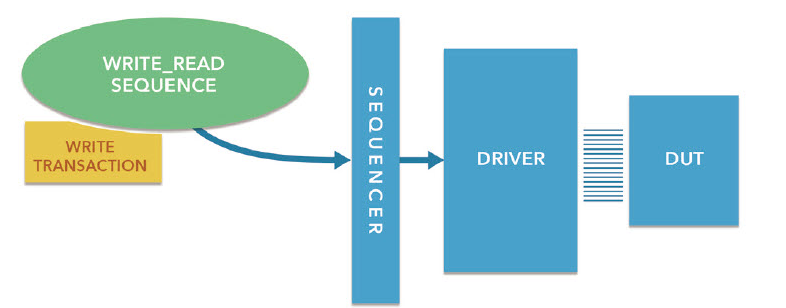

SystemVerilog通用驗證方法(UVM)是一種生成測試和檢查結果以進行功能驗證的有效方法,最適合用于塊級IC或FPGA或其他“小型”系統。在UVM測試臺中,大多數活動是通過編寫序列來生

2021-04-09 16:09:11 3584

3584

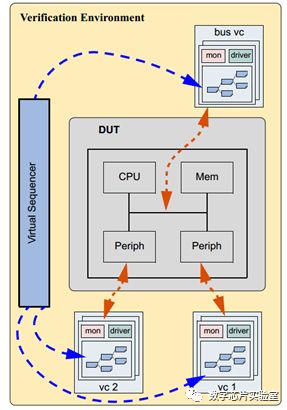

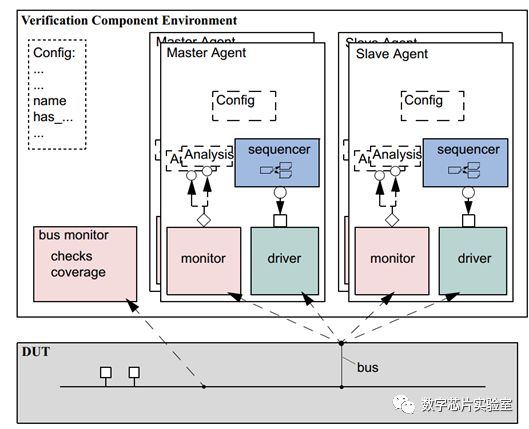

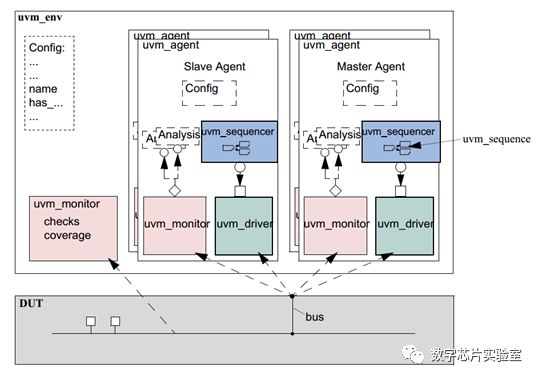

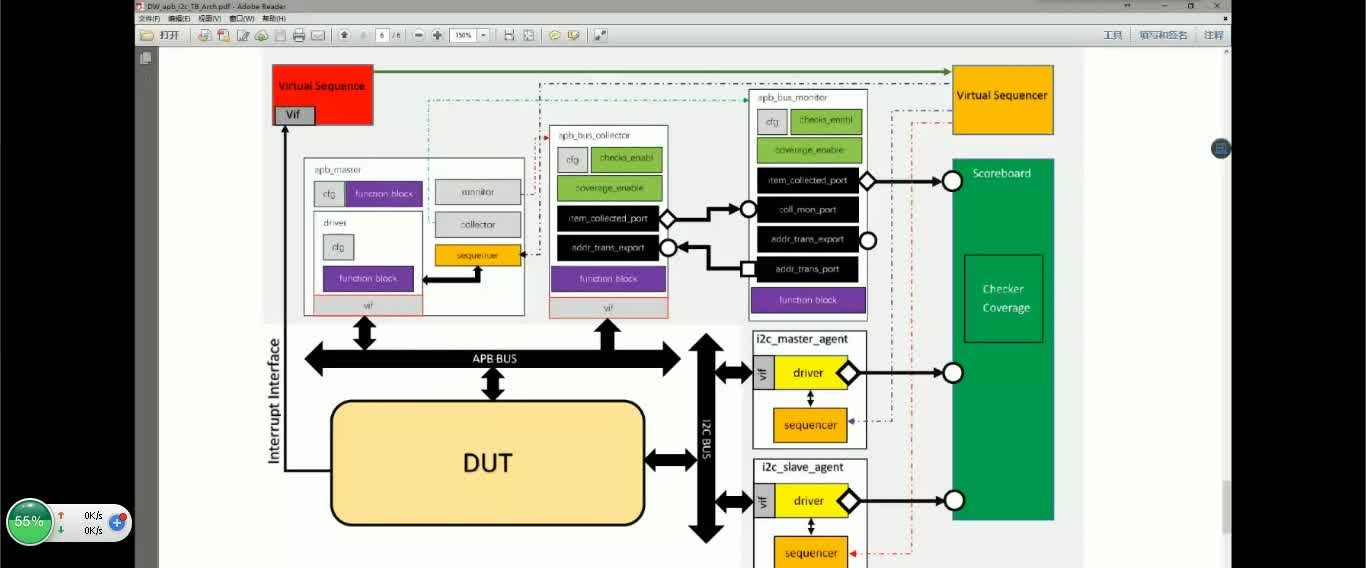

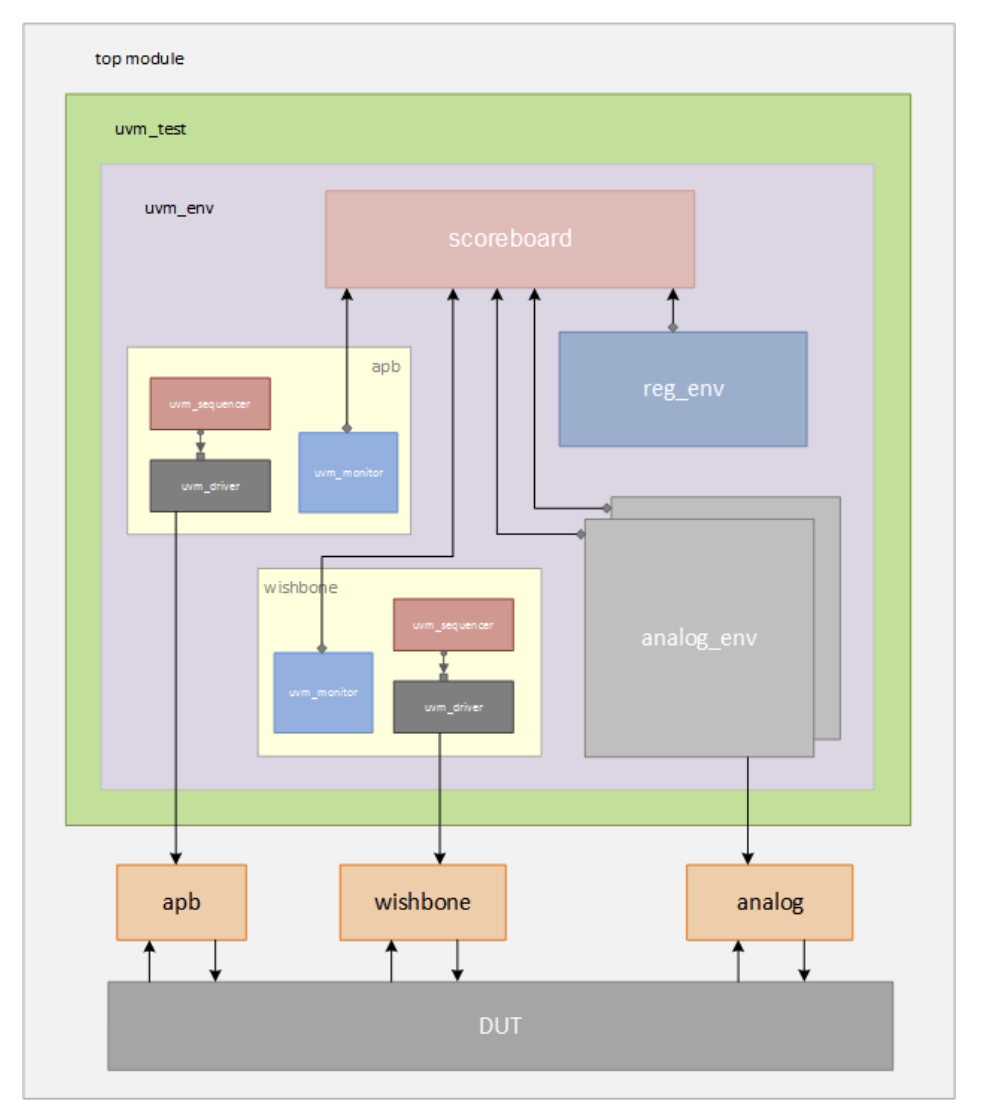

model)。一個簡單的驗證平臺框圖:在UVM中,引入了agent和sequence的概念,因此UVM中驗證平臺的典型框圖長這樣:通知:本章更新后在更新一篇《IC驗證之UVM常用宏匯總(四)》將不

2020-12-02 15:21:34

加入factory機制 上一節《IC驗證"一個簡單的UVM驗證平臺"是如何搭建的(五)》給出了一個只有driver、使用UVM搭建的驗證平臺。嚴格來說這根本就不算是UVM驗證

2020-12-08 12:07:21

本帖最后由 IC那些事兒 于 2020-12-4 15:50 編輯

上次更新完《IC驗證"UVM驗證平臺"組成》后本打算不再更新......但有人反映要繼續更新...繼續

2020-12-04 15:48:19

驗證的基本常識,將會散落在各個章節之間。UVM的一些高級功能,如何靈活地使用sequence機制、factory機制等。如何編寫代碼才能保證可重用性。可重用性是目前IC界提及最多的幾個詞匯之一,它包含

2020-12-01 15:09:14

: +define+MACRO 或者: +define+MACRO=100擴展寄存器模型中的數據位寬:`define UVM_REG_DATA_WIDTH 128擴展寄存器模型中的地址位寬:`define

2020-12-02 15:24:35

在上一節中,**《IC驗證"UVM驗證平臺加入factory機制"(六)》**雖然輸出了“main_phase is called”,但是“data is drived”并沒有

2020-12-09 18:28:15

有條理,我們要在驗證計劃當中明確要搭建什么樣的驗證平臺,目前主流的驗證平臺有基于verilog的印證平臺,基于systemverilog的驗證平臺,以及適用uvm方法學建立的驗證平臺,據uvm驗證方法

2021-01-21 15:59:03

原文鏈接:https://zhuanlan.zhihu.com/p/345775995大家好,我是一哥,上章內容主要講述兩個內容,芯片驗證以及驗證計劃。那本章我們主要講述的內容有介紹什么是uvm

2021-01-21 16:00:16

大家好,我是一哥,上章內容我們介紹什么是uvm?uvm的特點以及uvm為用戶提供了哪些資源? 本章內容我們來看一看一個典型的uvm驗證平臺應該是什么樣子的,來看一個典型的uvm測試平臺的結構

2021-01-22 15:32:04

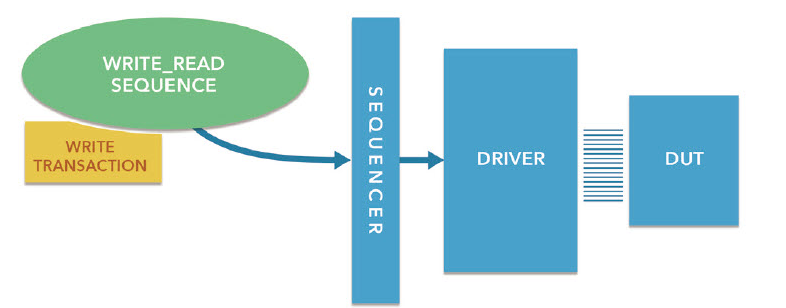

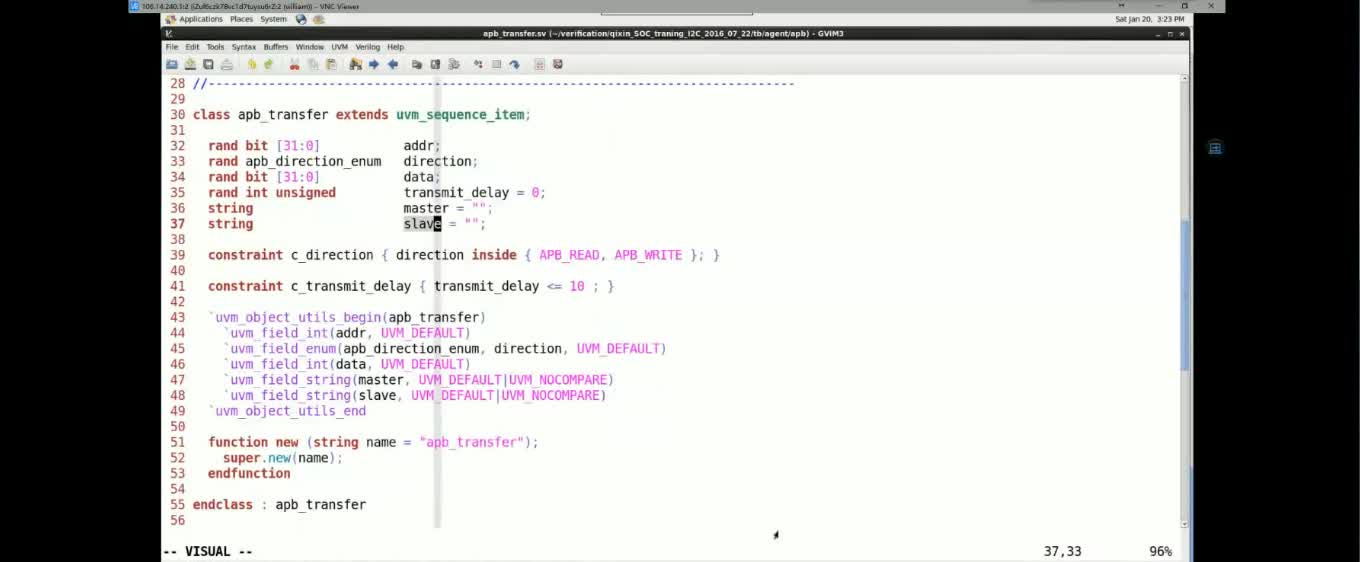

的transaction,以及創建用于產生事物的事物發生器sequence。 在uvm驗證平臺中穿梭各個組件之間的基本信息單元是一個被稱為transaction的數據對象,也就是我們前面所說的事物

2021-01-26 10:05:37

大家好,我是一哥,上章一個典型的uvm驗證平臺應該是什么樣子的?從本章開始就正式進入uvm知識的學習。先一步一步搭建一個簡單的可運行的測試平臺。 本章首先來介紹一下構成uvm測試平臺的主要組件

2021-01-22 15:33:26

數字IC是什么意思?數字IC前端設計流程有哪些?數字IC后端設計流程有哪些?

2021-10-20 06:24:49

到非常高的位置。 那么哪里可以學習數字ic設計呢,可以參考了解(IC修真院),我學習過這個課程,包含數字前端設計、驗證、后端設計等,從基礎知識,理論知識,技術原理,架構設計,分析問題能力,從應用到知識點,應有全有,實戰部分完全還原真實企業項目,是真正能提高實戰應用能力的。

2020-12-04 14:31:30

驗證方法簡介 設計驗證是用于證明設計正確性的過程,要求和規格。 在數字設計流程中,驗證可確保芯片按照設計意圖正確運行,然后再將設計送去制造。 具體來說,驗證方法是驗證集成電路設計的標準化方法。 驗證

2022-02-13 17:03:49

& IP Core Verification)”卷。 本章介紹了 IC 和 IP 核設計過程驗證中涉及的一些關鍵 Python 方法、工具、包和庫,包括以下章節: 純 Python

2022-11-03 13:07:24

海思成研無線部門高薪招聘數字IC設計/驗證高級工程師,在這里您可以近距離接觸業界最前沿的技術、最先進的工藝、最牛的設計和驗證水平;在這里您跟FELLOW一起共事,享受濃厚的技術氛圍;在這里您可感受到

2020-02-29 11:06:28

現階段的IC行業,數字IC驗證工程師非常緊缺,尤其是會UVM的驗證工程師那更是奇貨可居。但是最近和一些在校學生和剛入行的朋友們交流的時候,發現大多數人對數字IC驗證工程師的具體工作不甚了解,甚至還

2017-05-17 12:50:39

UVM Report機制概述

2020-12-21 06:55:05

大家好,我是一哥,上章內容我們介紹什么是uvm?uvm的特點以及uvm為用戶提供了哪些資源?本章內容我們來看一看一個典型的uvm驗證平臺應該是什么樣子的,來看一個典型的uvm測試平臺的結構。我們一個

2022-02-14 06:46:33

招聘崗位:芯片設計數字,驗證工程師崗位要求:1.本科及以上學歷,2年半以上工作經驗2.精通verilog,SV等語言3.有端到端項目的交付經驗4.精通VMM/UVM驗證方法學5.具備團隊合作意識,責任心強聯系方式:***簡歷投遞郵箱:lzdnewmail@163.com

2017-10-09 19:47:57

Systemverilog [1]和 UVM [2]為驗證團隊提供結構和規則。它使得在許多測試中能獲得一致的結果,并可以在團隊之間共享驗證。許多驗證團隊都在使用由C代碼編寫的驗證套件。本文將討論將基于C的測試和驗證套件集成到常規UVM測試平臺的各種方法。

2020-12-11 07:59:44

Systemverilog [1]和 UVM [2]為驗證團隊提供結構和規則。它使得在許多測試中能獲得一致的結果,并可以在團隊之間共享驗證。許多驗證團隊都在使用由C代碼編寫的驗證套件。本文將討論將基于C的測試和驗證套件集成到常規UVM測試平臺的各種方法。

2020-12-15 07:38:34

請教各位大佬,UVM是基于sv的驗證方法學,如果采用systemc語言編程,如何實現?

2019-11-07 15:30:16

),通常也叫寄存器模型,顧名思義就是對寄存器這個部件的建模。本文要介紹的內容,包括對UVM寄存器模型的概述,如何構建寄存器模型,以及如何將寄存器模型集成到驗證環境中。篇幅原因,將在下一篇文章再給出寄存器

2022-09-23 14:29:03

的物理驗證工作;3、按時匯報和推進項目進度。數字IC設計-深圳 上海 成都 杭州 蘇州 武漢 崗位要求:1、精通數字電路設計,熟練掌握Verilog,具有良好的編程風格;2、熟悉ARM Cortex-M

2018-08-02 16:18:53

新手學習SystemVerilog & UVM指南 從剛接觸System Verilog以及后來的VMM,OVM,UVM已經有很多年了,隨著電子工業的逐步發展,國內對驗證人才的需求也會急劇

2015-03-11 16:24:35

也買了一個大衣柜,專門用來放她的成堆的衣服、鞋包。” Chapter5. virtual\_sequencer/virtual\_sequence 曾經有位驗證者說過,UVM定義的virtual

2023-04-04 17:20:51

硬件驗證方法簡明介紹本書“硬件驗證方法簡明介紹”是“半導體 IP 核——不僅僅是設計”系列叢書中“驗證 IP 和 IP 核驗證”的一部分。本書調查、處理和介紹了 IC 驗證中涉及的一些關鍵方法、工具

2022-11-26 20:43:20

獵頭職位:IC驗證工程師【北京】崗位職責:1.根據芯片架構文檔和設計要點,制定驗證方案,擬定驗證計劃;2.根據驗證方案和計劃,實施驗證,包括編寫參考模型、搭建仿真驗證平臺與迭代改進、編寫完備的驗證

2017-02-15 13:39:33

。往往我們在書寫測試用例或者sequences的時候會有查詢驗證平臺組件uvm_component的需求,比如env/driver/monitor。由于sequences不是測試平臺層次結構的一部分,實現

2022-04-11 16:43:42

下uvm_info的三個參數。 ID是作為message的標記(tag)。 MSG就是真正要打印的message文本。 VERBOSITY用于傳遞uvm\_verbosity枚舉類型的數字。當

2023-03-17 16:41:28

全球電子設計創新領先企業Cadence設計系統公司,今天宣布了業界最全面的用于系統級芯片(SoC)驗證的通用驗證方法學(UVM)開源參考流程。為了配合Cadence EDA360中SoC實現能力的策略,

2010-06-28 08:29:14 2240

2240 基于UVM的CPU卡芯片驗證平臺_錢一文

2017-01-07 19:00:39 4

4 基于UVM的驗證平臺設計研究_王國軍

2017-01-07 19:00:39 4

4 基于UVM的CAN模塊自驗證方法_熊濤

2017-01-08 14:47:53 3

3 一種基于UVM的混合信號驗證環境_耿睿

2017-01-07 21:39:44 1

1 UVM使得驗證測試平臺的結構得以標準化,各種復用策略及標準對于提高驗證質量、縮短項目周期都非常有效。垂直重用是常見的復用策略之一,即同一項目測試平臺復用于不同驗證層次。驗證中常將最底層的IP級驗證平臺向更高的集成層復用,而UVM寄存器模型則是驗證平臺復用的一個關鍵部分。

2017-09-15 11:49:08 15

15 的連接、驅動器、監視器、仿真序列以及功能覆蓋率的建立。 本文呈現出了一種使用UVM驗證方法學構建基于高可配置性的高級微處理器總線架構(AMBA)的IP驗證環境,其中會使用到Synopsys公司的AMBA VIP和Ruby腳本。該驗證環境可以支持通過使用AMBA設計參數進行自

2017-09-15 14:37:34 6

6 UVM已經成為了一種高效率的、從模塊級到系統級完整驗證環境開發標準,其中一個關鍵的原則是UVM可以開發出可重用的驗證組件。獲得重用動力的一個方面表現為標準的仿真器和硬件加速之間的驗證組件和環境的復用

2017-09-15 17:08:11 14

14 毋庸置疑,UVM大大提高了我們開發驗證平臺的效率。但同時,熟練掌握UVM搭建驗證平臺也并不是一件容易的事情。同時由于不同驗證工程師搭建環境的風格不太一致,所以在一個項目中常會出現不好管理,甚至前后

2017-09-15 17:18:01 22

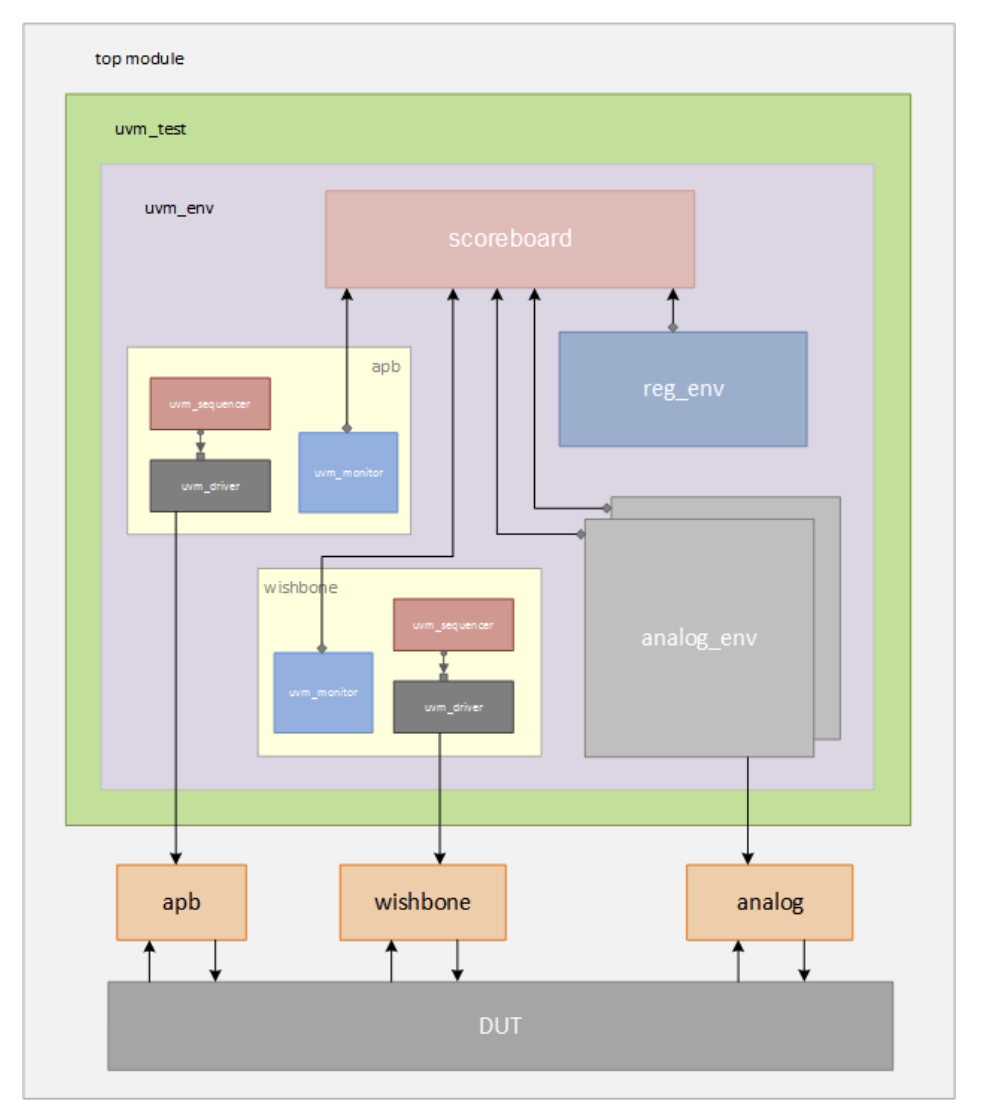

22 當我們驗證片上系統(SoC)嵌入了具有多個數字外設的微處理器以及可能的模擬模塊時,我們希望檢查所有實現的功能和可能的極端情況,以最大限度地縮短驗證時間。多種技術和方法的混合用于改進功能驗證并提取覆蓋

2019-08-09 15:25:34 6862

6862

近幾十年來,集成電路事業發展迅速,設計與工藝技術不斷發展,更多和更復雜的功能被集成到一塊芯片上。SoC的集成度和復雜度大大提高,在IC設計中就容易引入錯誤,所以驗證工作將變得艱巨。隨著IC設計規模

2020-01-27 17:21:00 6132

6132

Wilson Research Group 的一項最近研究發現,48% 的 FPGA 設計項目和 71% 的 ASIC設計項目依賴 UVM 進行設計驗證。

2020-03-02 18:12:24 1019

1019 本章第一節將大體介紹一下感性意義上的UVM,這里不會講的很詳細,因為關于UVM的歷史在網上已經有太多的資料第二節講述驗證平臺的組成,這里也只是介紹一個輪廓。第三節開始則會教我們一步一步搭建一個UVM

2020-07-01 08:00:00 69

69 盡管本指南提供了一組說明,以執行一個或多個特定的驗證任務,但應 以教育,經驗和專業判斷為補充。 并非本指南的所有方面都可能 適用于所有情況。 《 UVM 1.1用戶指南》不一定代表標準 必須謹慎判斷給定的專業服務是否足夠,也不應以此文件為依據 應用時無需考慮項目的獨特方面。

2021-03-29 10:41:32 21

21 數字IC就是傳遞、加工、處理數字信號的IC,是近年來應用最廣、發展最快的IC品種,可分為通用數字IC和專用數字IC。數字前端以設計架構為起點,以生成可以布局布線的網表為終點;是用設計的電路實現想法

2021-11-06 16:51:05 26

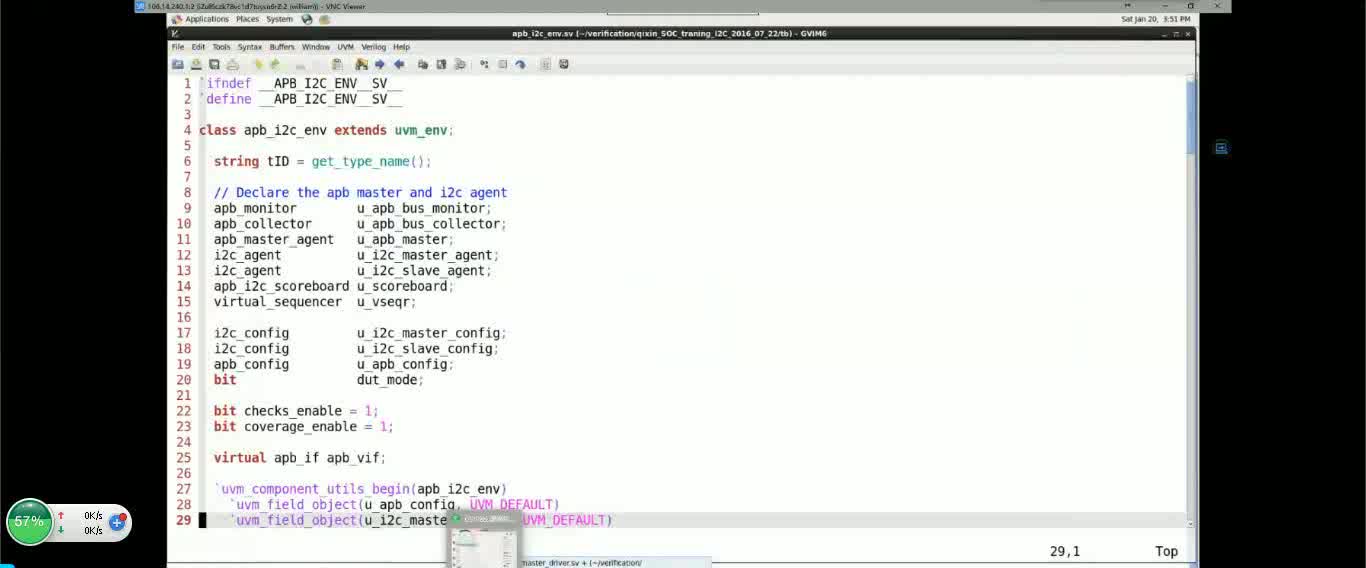

26 大家好,我是一哥,上章內容我們介紹什么是uvm?uvm的特點以及uvm為用戶提供了哪些資源?本章內容我們來看一看一個典型的uvm驗證平臺應該是什么樣子的,來看一個典型的uvm測試平臺的結構。我們

2021-12-09 13:36:13 7

7 利用Systemverilog+UVM搭建soc驗證環境

2022-08-08 14:35:05 5

5 百度百科對UVM的釋義如下:通用驗證方法學(Universal Verification Methodology, UVM)是一個以SystemVerilog類庫為主體的驗證平臺開發框架,驗證工程師可以利用其可重用組件構建具有標準化層次結構和接口的功能驗證環境。

2022-11-30 12:47:00 1060

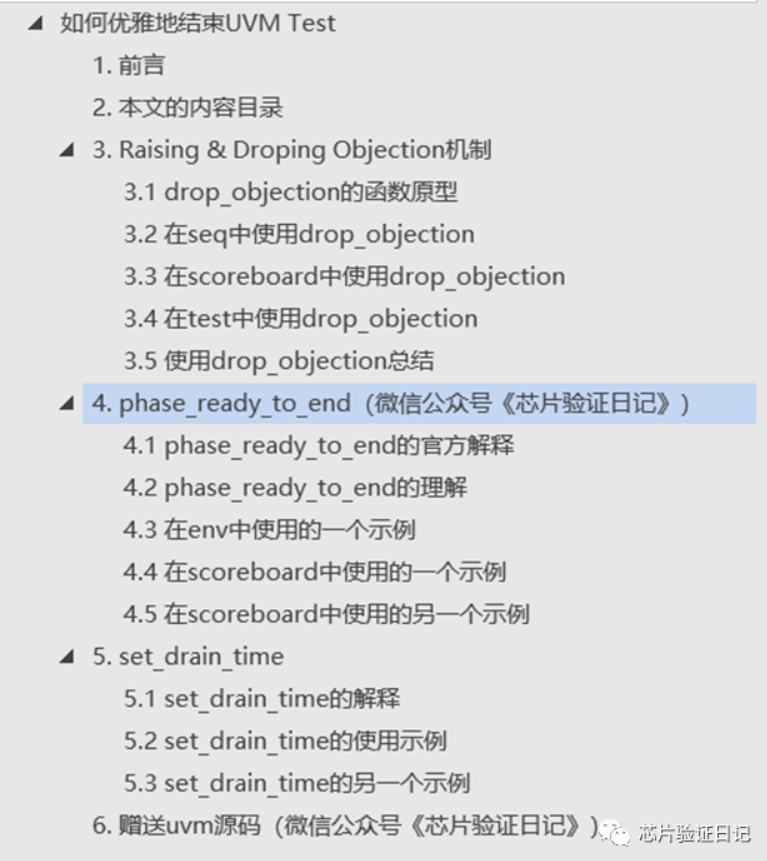

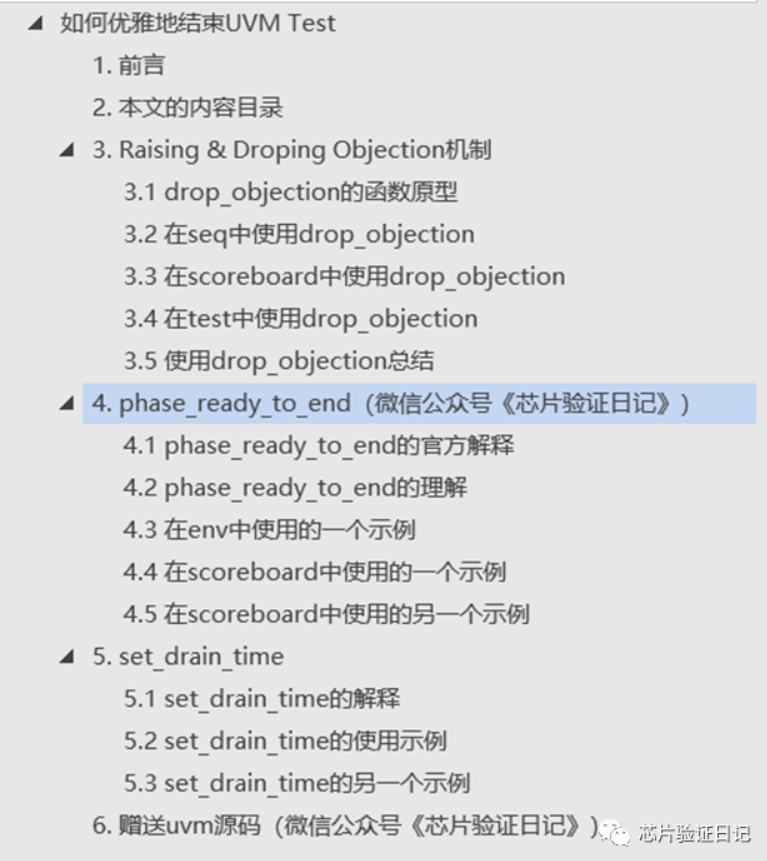

1060 分享一下在UVM驗證環境中,結束仿真的幾種方式,不同結束仿真的方式適合不同的應用場景。

2022-12-17 11:23:54 1702

1702

因為DUT是一個靜態的內容,所以testbench理應也是靜態的,其作為uvm驗證環境和DUT的全局根結點。

2023-03-21 11:33:02 982

982 UVM environment**包含多個可重用的驗證組件,并根據test case的需求進行相應的配置。例如,UVM environment可能具有多個agent(對應不同的interface)、scoreboard、functional coverage collector和一些checker

2023-03-21 11:35:25 744

744

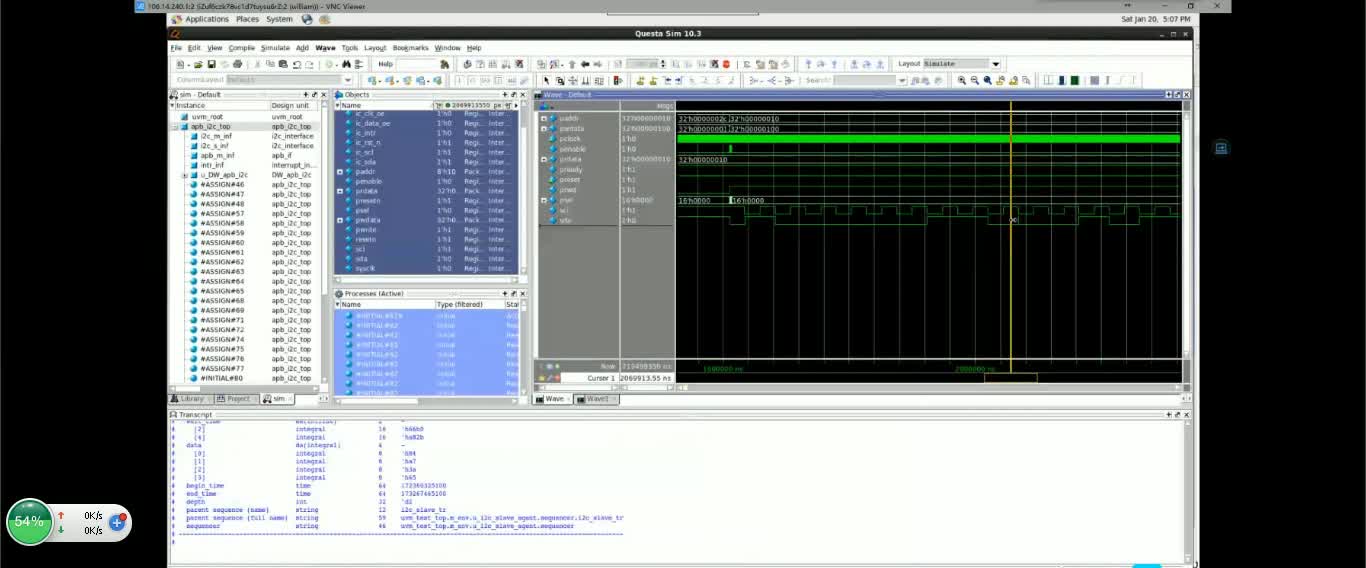

基于UVM搭建驗證環境和構造驗證激勵,調試的工作總是繞不開的。實際上,對驗證環境和激勵的調試,往往伴隨著驗證階段的前半程,并且會花掉驗證工程師很多時間和精力。

2023-04-06 09:36:03 428

428 IC設計和IC驗證都是非常重要的環節,一個好的IC產品需要二者的配合。IC設計是在滿足產品規格書的前提下,實現電路性能、功耗、面積等方面的優化,從而滿足設計需求的過程。而IC驗證是在設計完成后,必須對所設計的芯片進行正確性、可靠性、功耗等方面的驗證。

2023-04-12 14:01:33 2603

2603 IC設計和IC驗證都是非常重要的環節,一個好的IC產品需要二者的配合。IC設計是在滿足產品規格書的前提下,實現電路性能、功耗、面積等方面的優化,從而滿足設計需求的過程。而IC驗證是在設計完成后,必須對所設計的芯片進行正確性、可靠性、功耗等方面的驗證。

2023-04-13 17:50:50 4535

4535 話說螺螄殼里做道場,UVM推出這么多年以來每年DVCon會議上總還是有人分享他們基于UVM package做的一些改動,使其能夠更適合項目的要求。

2023-04-13 18:13:09 1207

1207 在UVM中,transaction 是一個類對象,它包含了建模兩個驗證組件之間的通信所需的任何信息。

2023-05-24 09:17:32 1165

1165

driver應該派生自uvm_driver,而uvm_driver派生自uvm_component。

2023-05-26 14:38:46 823

823

如下圖所示,UVM中的TLM接口為組件之間Transaction的發送和接收提供了一套統一的通信方法。

2023-05-29 09:31:44 340

340

本文使用Easier UVM Code Generator生成包含多個agent和interface的uvm驗證環境。

2023-06-06 09:13:02 584

584 有的認為驗證業務方向很重要,有的認為驗證思維更重要,有的認為驗證的通用代碼能力SV+UVM更重要。

2023-06-25 09:47:12 279

279 提高驗證生產力的關鍵之一就是在合適的**抽象層次**思考問題和完成驗證工作,為此UVM提供了 **事務級別(transaction level)** 的通信接口 **(Transaction-Level Modeling,TLM)** 。

2023-06-25 11:42:11 288

288

IC驗證,即集成電路驗證(Integrated Circuit Verification),是指針對硬件設計中的集成電路(IC)進行的一系列功能驗證、性能驗證和正確性驗證的過程。它是電子設計自動化(EDA)領域中非常重要的環節,用于確保設計的集成電路在實際生產中能夠正常運行。

2023-07-24 15:45:18 2094

2094 本篇是對UVM設計模式 ( 二 ) 參數化類、靜態變量/方法/類、單例模式、UVM_ROOT、工廠模式、UVM_FACTORY[1]中單例模式的補充,分析靜態類的使用,UVM中資源池的實現,uvm_config_db的使用。

2023-08-06 10:38:41 825

825

FPGA驗證和UVM驗證在芯片設計和驗證過程中都扮演著重要的角色,但它們之間存在明顯的區別。

2024-03-15 15:00:41 94

94

電子發燒友App

電子發燒友App

評論