作者為 劉于葦副主分析師。

要支持3DIC、Chiplet的Die-to-Die互聯(lián)和異構(gòu)集成,需要什么樣的IP和EDA工具支持?物聯(lián)網(wǎng)邊緣計(jì)算成為趨勢,需要什么樣的處理器?地緣政治環(huán)境下,RISC-V開源架構(gòu)的生態(tài)要如何繼續(xù)發(fā)展?隨著人工智能、機(jī)器學(xué)習(xí)技術(shù)的發(fā)展,本土EDA和IP企業(yè)如何借勢突破,加速融入集成電路產(chǎn)業(yè)鏈和價(jià)值鏈?

隨著全球集成電路行業(yè)整體的景氣度的提升,IC設(shè)計(jì)市場也保持著快速發(fā)展的趨勢。隨著先進(jìn)工藝節(jié)點(diǎn)不斷演進(jìn),晶體管尺寸在不斷逼近物理極限;而以ChatGPT為代表的語言大模型對(duì)芯片算力的要求不斷上漲,也在刺激著AI芯片用Chiplet等更先進(jìn)的封裝來突破摩爾定律,實(shí)現(xiàn)更優(yōu)PPA。

于是后摩爾時(shí)代對(duì)處于IC設(shè)計(jì)上游的EDA和IP,提出了更高的要求。要支持3DIC、Chiplet的Die-to-Die互聯(lián)和異構(gòu)集成,需要什么樣的IP和EDA工具支持?物聯(lián)網(wǎng)邊緣計(jì)算成為趨勢,需要什么樣的處理器?地緣政治環(huán)境下,RISC-V開源架構(gòu)的生態(tài)要如何繼續(xù)發(fā)展?隨著人工智能、機(jī)器學(xué)習(xí)技術(shù)的發(fā)展,本土EDA和IP企業(yè)如何借勢突破,加速融入集成電路產(chǎn)業(yè)鏈和價(jià)值鏈?

帶著這些業(yè)界難題,ASPENCORE在日前舉辦的國際集成電路展覽會(huì)暨研討會(huì)(IIC Shenzhen 2023)上,同期舉辦了一場“EDA/IP與IC設(shè)計(jì)論壇”,邀請(qǐng)到來自Cadence、安謀科技、Imagination、芯和半導(dǎo)體、奎芯科技、燦芯半導(dǎo)體、芯來科技等業(yè)內(nèi)先進(jìn)企業(yè)的嘉賓,就上述問題展開討論,出謀劃策,共同助推產(chǎn)業(yè)創(chuàng)新發(fā)展。?

適用大模型AI芯片的接口IP

近年來AI技術(shù)的發(fā)展十分迅猛,以ChatGPT為代表的生成式AI應(yīng)用,無論是邏輯還是語言各方面都達(dá)到甚至超過了很多人類的認(rèn)知水平。對(duì)于AI的發(fā)展,有人恐慌,有人則認(rèn)為這是科技發(fā)展的客觀規(guī)律。Cadence技術(shù)支持總監(jiān)?李志勇認(rèn)為,應(yīng)該用更積極的態(tài)度擁抱AI,利用好這個(gè)工具去做一些重復(fù)性的工作,效果比人工來的更好,在一些復(fù)雜的場景下,使用AI可以協(xié)助人類提高生產(chǎn)率。

當(dāng)前,AI芯片需求不斷增長。過去數(shù)據(jù)中心最常用的是GPU,但隨著語言大模型對(duì)算力需求各方面的增長,業(yè)界開始傾向使用針對(duì)某類應(yīng)用的專用ASIC。據(jù)Bloomberg統(tǒng)計(jì),未來10年專用ASIC的CAGR將達(dá)到33%,這個(gè)產(chǎn)業(yè)也將從37億美金增長到641億美金。

李志勇詳細(xì)介紹了AI應(yīng)用于Cloud、Edge、Endpoints等不同領(lǐng)域時(shí),對(duì)于GDDR6、DDR5、HBM2E等內(nèi)存IP的不同需求。例如DDR適合服務(wù)器等對(duì)大容量有要求的應(yīng)用;LPDDR主要用于移動(dòng)設(shè)備、ADAS等對(duì)功耗要求更高的應(yīng)用;GDDR主要滿足帶寬、成本、可靠性的要求;而對(duì)于更高容量的要求,HBM能夠提供最高的帶寬。

另外AI芯片對(duì)PCIe、CXL、高速以太網(wǎng)和Chiplet Die-to-Die接口IP也有很大需求。?從Cadence的角度來看,一顆AI SoC就是一個(gè)智能系統(tǒng),把這個(gè)智能系統(tǒng)放在終端產(chǎn)品里,要達(dá)到更好的用戶體驗(yàn)、優(yōu)化應(yīng)用負(fù)載,兼容各種應(yīng)用和平臺(tái),之間很多是互相矛盾的,但是需要盡量達(dá)到最好。

面向IoT,需要什么樣的處理器?

隨著IoT領(lǐng)域?qū)υO(shè)備算力的需求越來越高,當(dāng)我們考慮未來的IoT芯片形態(tài)應(yīng)該怎樣發(fā)展時(shí),算力是非常重要的點(diǎn)。但同時(shí)也要注意,IoT設(shè)備算力的提高,并不能以芯片的面積、功耗線性增加為代價(jià)。

“未來我們在具體的算力分割上,Arm希望一些顆粒度比較小的計(jì)算,可以用處理器上的矢量擴(kuò)展(Helium tecnology)來實(shí)現(xiàn);顆粒度比較大的計(jì)算場景,可以用一些專門的AIPU來計(jì)算。”?安謀科技產(chǎn)品總監(jiān)?陳江杉?圍繞萬物互聯(lián)時(shí)代對(duì)處理器的要求,介紹了安謀科技最新面相IoT的新一代處理器星辰STAR-MC2。

低功耗CPU需要考慮的基礎(chǔ)原則是面向微控制器市場,所以星辰STAR-MC2在具體指令級(jí)選擇上采用了Cortex-M系列。在低功耗設(shè)計(jì)方面,面積和功耗受限的情況下,CPU的中斷、調(diào)試模塊都可以跟處理器做進(jìn)一步的集成。

“無論是軟件還是生態(tài)系統(tǒng),Arm不僅開放了完整的總線標(biāo)準(zhǔn),也做了一些可靠的參考設(shè)計(jì)提供給芯片客戶,甚至提供給這些生態(tài)的客戶去開發(fā)。”?陳江杉說到。

做一款整個(gè)業(yè)界都可以遵循軟件標(biāo)準(zhǔn)和通用接口開發(fā)的處理器,需要長年的積累,“設(shè)計(jì)這款處理器的初衷,也是希望跟之前的老處理器之間有一致性和延續(xù)性前提下,又進(jìn)一步有技術(shù)的提高。”

基于上一代產(chǎn)品,安謀科技著眼于以下幾個(gè)點(diǎn)布局新的產(chǎn)品形態(tài)。首先,通過新的指令級(jí)、新的擴(kuò)展(包括矢量擴(kuò)展),在不顯著增加面積和功耗的前提下,可以增加計(jì)算密度來滿足越來越高的計(jì)算需求;同時(shí),在v8架構(gòu)下引入TrustZone信息,允許設(shè)備敏感信息運(yùn)行在平臺(tái)上,這里面包含更強(qiáng)的內(nèi)存管理單元,也包括一些軟件棧檢查的功能,更好地保證整個(gè)計(jì)算平臺(tái)的信息安全;最后,國內(nèi)汽車工業(yè)對(duì)基于ISO 26262或ISO 61508標(biāo)準(zhǔn)的可靠性有一定要求,所以安謀科技也做了完整的一套功能安全的設(shè)計(jì),并且已經(jīng)通過了業(yè)界最高的車規(guī)認(rèn)證。

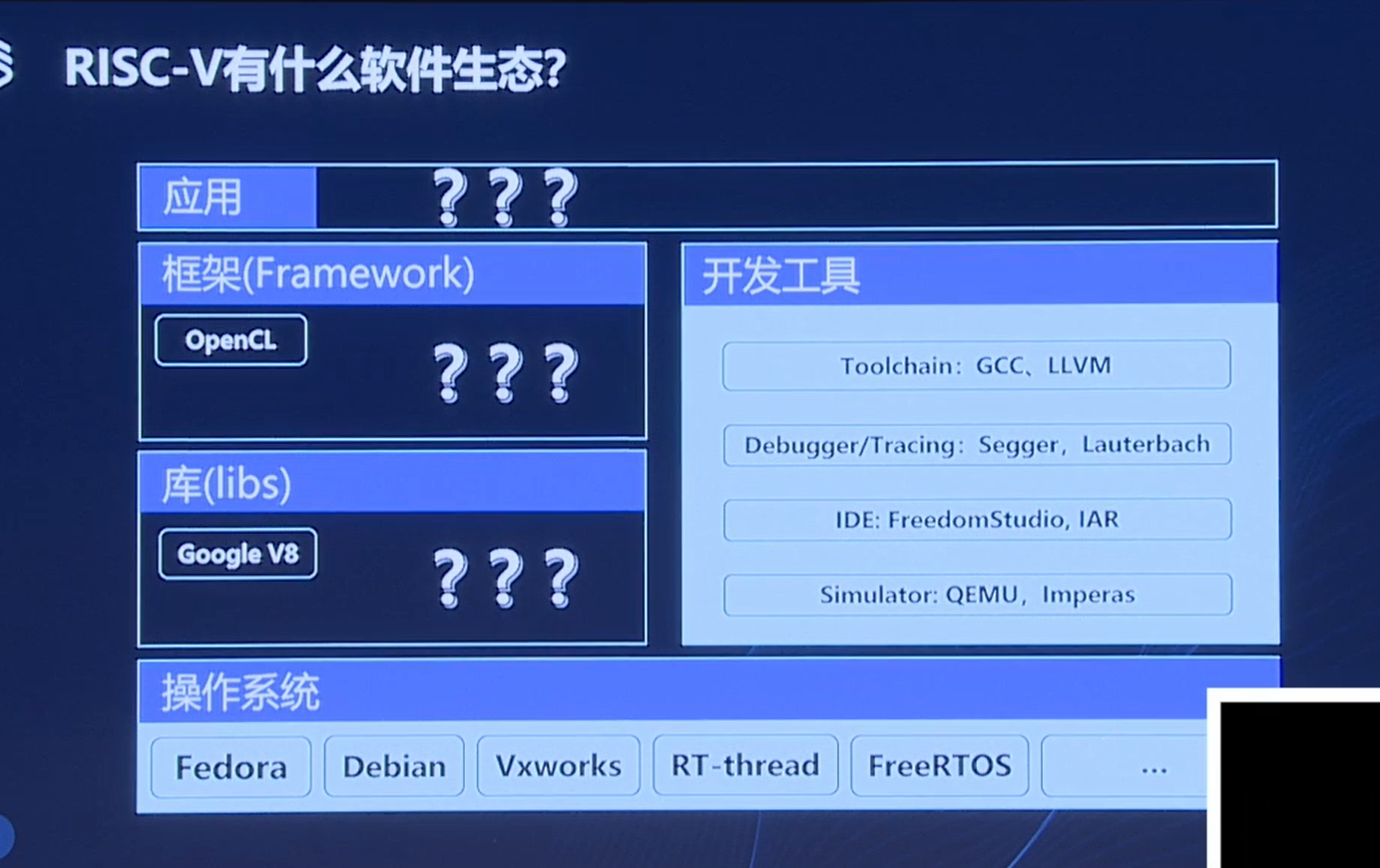

Imagination在RISC-V?上的布局

為什么現(xiàn)在RISC-V這么火?首先,RISC-V是一個(gè)基于開源的指令集架構(gòu),它在全球有非常多的開發(fā)者以及生態(tài)伙伴,而RISC-V國際基金會(huì)是一個(gè)總部在瑞士的中立機(jī)構(gòu),不受任何單一國家或公司控制。目前已經(jīng)有非常多商業(yè)公司、研究院所和高校進(jìn)入這個(gè)領(lǐng)域,生態(tài)上也有Linux、Android以及國產(chǎn)的統(tǒng)信、麒麟等表示支持 RISC-V。

“雖說RISC-V架構(gòu)是開源可授權(quán)的,但并不是說它是免費(fèi)的,各家公司之間產(chǎn)生競爭才會(huì)有創(chuàng)新。所以隨著越來越多玩家加入RISC-V產(chǎn)業(yè),開發(fā)者們在社區(qū)貢獻(xiàn)自己的力量,就會(huì)推動(dòng)它不斷創(chuàng)新,這就是RISC-V的魅力。” Imagination市場及業(yè)務(wù)發(fā)展高級(jí)經(jīng)理?黃音?介紹了公司在RISC-V領(lǐng)域的產(chǎn)品方向和布局。

Imagination有四大產(chǎn)品方向,分別是移動(dòng)領(lǐng)域、消費(fèi)電子領(lǐng)域、汽車領(lǐng)域和PC 與數(shù)據(jù)中心。說到選擇RISC-V的原因,黃音表示,首先Imagination是傳統(tǒng)的IP供應(yīng)商,在IP的授權(quán)、支持、售后上有自己的優(yōu)勢和經(jīng)驗(yàn);第二,無論CPU/GPU/NPU都是復(fù)雜的IP,需要的大量經(jīng)驗(yàn)正好是Imagination具備的;第三,Imagination之前旗下的MIPS雖然已經(jīng)剝離出來,但仍然可以永久使用其的專利;第四,Imagination在售后支持上有專業(yè)的團(tuán)隊(duì)和多年沉淀。

黃音表示,Imagination非常早期就成為了RISC-V國際基金會(huì)的會(huì)員,也有成員在董事會(huì)、技術(shù)委員任職。“在汽車、浮點(diǎn)運(yùn)算、安卓、功能安全、信息安全等不同的細(xì)分小組里也有人任職,這些領(lǐng)域?qū)<叶荚跒镽ISC-V的整個(gè)生態(tài)做貢獻(xiàn)。”今年剛成立的RISE組織是RISC-V基金會(huì)中單獨(dú)成立做軟件生態(tài)的,Imagination也是創(chuàng)始成員之一,RISE將對(duì)RISC-V生態(tài)擴(kuò)展起到非常大的作用。

EDA使能3DIC?Chiplet先進(jìn)封裝設(shè)計(jì)

EDA處于半導(dǎo)體行業(yè)中最前端的環(huán)節(jié),相當(dāng)于整個(gè)生態(tài)的支點(diǎn),用類似杠桿的方式支撐了后面IP、晶圓制造、封測以及電子系統(tǒng)應(yīng)用的整個(gè)市場規(guī)模。

“最近兩年Chiplet很火,也是每次行業(yè)大會(huì)討論最多的熱點(diǎn)議題。我將Chiplet理解為一種設(shè)計(jì)理念,其背后的支撐技術(shù)實(shí)際是先進(jìn)封裝能力。”芯和半導(dǎo)體技術(shù)市場總監(jiān)?黃曉波?首先介紹Chiplet的起源和興起的背景及驅(qū)動(dòng)力,隨后從Chiplet實(shí)現(xiàn)的關(guān)鍵技術(shù)展開,談到了芯和半導(dǎo)體針對(duì)Chiplet設(shè)計(jì)挑戰(zhàn)的一站式EDA解決方案,助力產(chǎn)業(yè)發(fā)展。

在過去50多年,摩爾定律長期牽引著整個(gè)半導(dǎo)體行業(yè)的發(fā)展,如今由于先進(jìn)工藝制程升級(jí)變緩,研發(fā)成本高昂,無法像過去那樣每18~24個(gè)月帶動(dòng)晶體管集成的數(shù)量翻倍,導(dǎo)致半導(dǎo)體性能提升面臨瓶頸。不過好在先進(jìn)封裝仍在持續(xù)演進(jìn),從1970年的MCM到SiP,再到2.5D和現(xiàn)在的3DIC、異構(gòu)集成,先進(jìn)封裝技術(shù)為半導(dǎo)體行業(yè)的突破打開了另一扇大門。

Chiplet實(shí)現(xiàn)的關(guān)鍵技術(shù)包括Die-to-Die互連、先進(jìn)封裝3D異構(gòu)集成以及全新的設(shè)計(jì)流程和EDA工具。“芯和半導(dǎo)體提供一站式3DIC Chiplet EDA多物理場仿真平臺(tái),從信號(hào)完整性、電源完整性、多物理場分析及系統(tǒng)驗(yàn)證等維度支撐Chiplet設(shè)計(jì)的實(shí)現(xiàn)與落地,目前已經(jīng)被國際領(lǐng)先的算力芯片設(shè)計(jì)公司選購采用,成功驗(yàn)證了該方案對(duì)Chiplet先進(jìn)封裝工藝、接口協(xié)議標(biāo)準(zhǔn)、數(shù)據(jù)格式兼容和典型互連結(jié)構(gòu)的全面支持,希望與產(chǎn)業(yè)鏈上下游伙伴共建共享Chiplet發(fā)展的繁榮生態(tài)。”?黃曉波說到。

實(shí)現(xiàn)邊緣計(jì)算Chiplet互聯(lián)的關(guān)鍵IP

近年來大量公司涌入AI領(lǐng)域展開布局,雖然ChatGPT一類的大模型很火,但巨大的投入也讓大部分公司望而卻步,邊緣AI計(jì)算是一個(gè)更大眾的選擇方向。據(jù)市場機(jī)構(gòu)預(yù)測,到2024年,邊緣AI芯片的增長速度會(huì)超過整體的芯片市場。

“不過現(xiàn)在AI SoC對(duì)算力的要求越來越高,設(shè)計(jì)難度也就越來越大。唯一的解決辦法是通過Die-to-Die互聯(lián),把I/O部分放到旁邊,再通過主Die接口訪問I/O Die,實(shí)現(xiàn)數(shù)據(jù)之間的交互。”?奎芯科技資深產(chǎn)品經(jīng)理?王尚元?強(qiáng)調(diào),多Die也會(huì)帶來一些問題,比如封裝良率降低帶來的成本問題,只能通過把Die做小來分?jǐn)偝杀荆八袁F(xiàn)在AI算力的瓶頸就被卡在互聯(lián)跟內(nèi)存上。”

在這兩個(gè)卡脖子的地方,奎芯科技作為IP廠商,在互聯(lián)方面推出了PCIe,在內(nèi)存接口上推出了LPDDR。王尚元首先介紹了AI芯片目前對(duì)內(nèi)存的選擇,無非是LPDDR4X/5X、GDDR6、HBM2E/3這幾種解決方案,“從帶寬、容量、功耗、顆粒成本等方面比較來看,GDDR6帶寬對(duì)AI推理是最理想的,而DDR在做訓(xùn)練、電源管理、動(dòng)態(tài)功耗的動(dòng)態(tài)頻點(diǎn)切換時(shí)不可缺少。”

據(jù)介紹,奎芯科技的LPDDR PHY具有高適配、低延時(shí)、低功耗、易擴(kuò)展、高可靠5大優(yōu)勢。同時(shí)在做訓(xùn)練時(shí),這款LPDDR PHY內(nèi)部的獨(dú)立Training機(jī)制可以通過不同的場景,做快速訓(xùn)練,并且可適配不同廠家、不同型號(hào)的顆粒。

同時(shí)為了增加互聯(lián)的帶寬,奎芯科技符合UCIe標(biāo)準(zhǔn)的接口IP支持Chiplet中計(jì)算和存儲(chǔ)小芯片之間互聯(lián),還可以把I/O小芯片單獨(dú)放出去,在小芯片跟I/O之間做互聯(lián)。由于UCIe是開放的、支持多協(xié)議的封裝內(nèi)互聯(lián)標(biāo)準(zhǔn),所以在通用物理層和鏈接層之上支持多種協(xié)議,不需要做協(xié)議轉(zhuǎn)換。

打造國產(chǎn)一站式IP與SoC設(shè)計(jì)服務(wù)平臺(tái)

燦芯半導(dǎo)體主要為客戶提供IP和IC設(shè)計(jì)服務(wù),IP方面包括模擬類IP和高速接口IP,設(shè)計(jì)服務(wù)專注于ASIC和SoC設(shè)計(jì)服務(wù)平臺(tái),SoC方面主要專注在65nm以下的工藝節(jié)點(diǎn),以及65nm以上的高性能模擬類IP的設(shè)計(jì)。五大塊主營業(yè)務(wù)包括:1、為客戶提供芯片全定制服務(wù);2、芯片工程定制服務(wù);3、SoC系統(tǒng)設(shè)計(jì)平臺(tái);4、IP定制化及整體解決方案;5、作為ASIC生態(tài)系統(tǒng)的重要組成部分。

燦芯半導(dǎo)體IP項(xiàng)目總監(jiān)?饒青重點(diǎn)介紹了公司高速接口IP的主要性能和指標(biāo)。????接口IPYouDDR目前經(jīng)過硅驗(yàn)證,最高速率達(dá)到4266Mbps;YouSerdes系列最高速率可到32Gbps,支持包括PCIe、USB3.1/3.0、SATA Gen 3.0/2.0/1.0等多種協(xié)議;PCIe PHY的IP可以向下兼容到PCIe1.0,支持16 LAN,具有低延遲和小面積的特點(diǎn)。此外還有YouUSB 2.0 OTG PHY IP、MIPI CSI2/DSI2接口解決方案、TCAM IP以及基于45/55nm開發(fā)的16bit 1~5Msps SAR ADC等產(chǎn)品。

在IC設(shè)計(jì)方面,燦芯半導(dǎo)體的IoT平臺(tái)基于55nm工藝開發(fā),使用ARM Cortex M系列平臺(tái)。而基于ARM Cortex A系列核架構(gòu)開發(fā)的AP解決方案,經(jīng)過了40nm和28nm的工藝流片,“我們可以為客戶提供整套軟件套件,縮短客戶SoC產(chǎn)品上市的時(shí)間。”?饒青說到,同時(shí)從客戶端反饋來看,越來越多的客戶基于國際環(huán)境及成本考慮,想把FPGA方案轉(zhuǎn)成ASIC。“基于燦芯自有的SoC設(shè)計(jì)流程經(jīng)驗(yàn)以及IP種類的儲(chǔ)備,可以為客戶提供比較完善的FPGA轉(zhuǎn)化為ASIC的國產(chǎn)替代方案。”

RISC-V?CPU?IP助力國產(chǎn)芯

從內(nèi)核到軟件的溝通橋梁就是ISA。RISC-V為什么這么重要?因?yàn)樵谝郧埃瑥慕涌诘酵ㄓ嵍加袠?biāo)準(zhǔn)接口,唯獨(dú)ISA層面沒有標(biāo)準(zhǔn),因?yàn)镮SA屬于Intel或ARM這樣的單一公司。這極大影響了整個(gè)產(chǎn)業(yè)的能動(dòng)性和發(fā)展。

最開始Intel的X86不做架構(gòu)和IP授權(quán),僅以芯片的形式開放。隨后Arm雖然開啟了IP和架構(gòu)授權(quán)的形式,但這兩家公司仍然對(duì)指令級(jí)的發(fā)展具有決定權(quán)。“后續(xù)一些小的架構(gòu)在發(fā)展的過程中逐步消亡,也證明了如果不開放生態(tài)的話,就不會(huì)收獲用戶。”?芯來科技戰(zhàn)略市場副總?李玨?表示,直到2013年以后RISC-V出現(xiàn),才成為一個(gè)公開化的國際標(biāo)準(zhǔn),在大家的關(guān)注下于2018年開始正式產(chǎn)業(yè)化。“正如倪光南院士所說,RISC-V會(huì)與x86、ARM呈三分天下之勢,我們也拭目以待。”

李玨分享了公司成立五年來利用RISC-V開放架構(gòu),做自主可控的IP生態(tài),以及和其他的IP、芯片公司合作,把RISC-V一步步在國內(nèi)落地的經(jīng)驗(yàn)。他認(rèn)為在這幾年支撐芯來成長的,是這幾個(gè)關(guān)鍵詞:

第一,RISC-V的天然基因:開放。因?yàn)殚_放了,才有軟件、硬件、集成電路公司、EDA公司來支持RISC-V。

第二,繁榮。這個(gè)繁榮是從AIoT賽道起跑的,過去的PC時(shí)代和移動(dòng)互聯(lián)網(wǎng)時(shí)代都不可能給RISC-V這個(gè)機(jī)會(huì),直到AIoT時(shí)代,RISC-V從邊緣AI、IoT設(shè)備、IoT芯片出發(fā),才開始讓大家從接受RISC-V,到在高算力AI芯片中嘗試使用RISC-V。

第三,自主。從國際形勢來看,有一個(gè)自主可控的、不受外國公司制約的指令集,對(duì)我們開發(fā)使用自己應(yīng)用、賦能的CPU IP產(chǎn)業(yè)來說有極大的促進(jìn)作用。

“從整個(gè)RISC-V的生態(tài)來說,芯來科技是一家中立的IP商,我們希望在產(chǎn)業(yè)里為大家提供更多的價(jià)值。”?李玨說到,五年來芯來推出了2369的完整系列,可以對(duì)標(biāo)ARM從M0一直到A55、A53級(jí)別的各種CPU,還可以做差異化功能。擁有國際上第一個(gè)完成ISO 26262 ASIL-D產(chǎn)品認(rèn)證的RISC-V CPU IP,也是國內(nèi)第一家CPU IP公司獲得ASIL D的認(rèn)證。

編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論