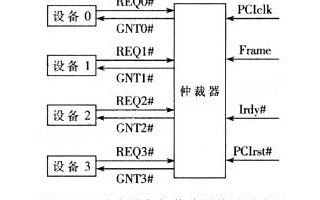

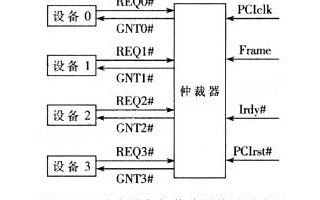

,為了使PCI設(shè)備能夠更方便地應(yīng)用在嵌入式系統(tǒng)中,本文介紹了一種基于CPLD(復(fù)雜可編程邏輯器件)的PCI總線仲裁器的設(shè)計(jì)方法,此方法可以為系統(tǒng)量身定制適合于系統(tǒng)本身的PCI總線仲裁器。而不必局限于特定的芯片要求,在體積、功能、成本等諸多方面都有很好的應(yīng)用前景。

2020-06-26 09:30:00 928

928

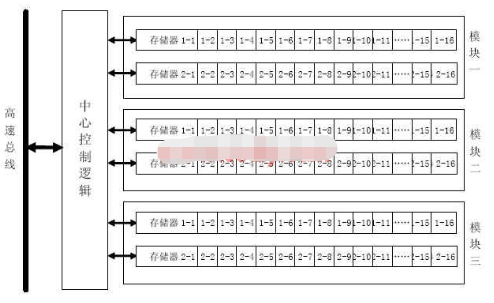

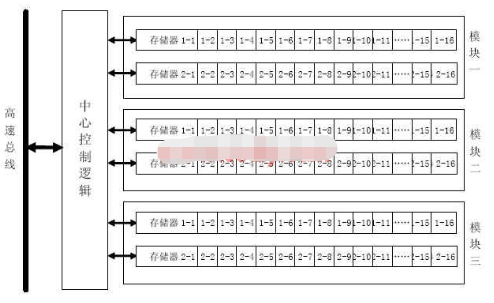

本文介紹了一種以FPGA作為控制器,F(xiàn)LASH MEMORY作為主存儲(chǔ)器的大容量高速存儲(chǔ)系統(tǒng)方案,并對(duì)關(guān)鍵技術(shù)及實(shí)現(xiàn)途徑進(jìn)行了論述,在存儲(chǔ)容量及存儲(chǔ)速度上實(shí)現(xiàn)了突破。

2020-07-30 17:53:54 1917

1917

一、概述2通道數(shù)據(jù)采集系統(tǒng)可以實(shí)現(xiàn)150MS/s采樣,連續(xù)采集存儲(chǔ)以及實(shí)時(shí)信號(hào)處理等功能。用QT1138AC采集卡,在FIFO采集模式下,是將板載內(nèi)存虛擬為一個(gè)大容量FIFO允許采集數(shù)據(jù)由該

2016-07-25 11:35:43

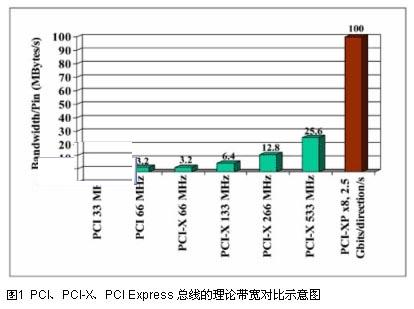

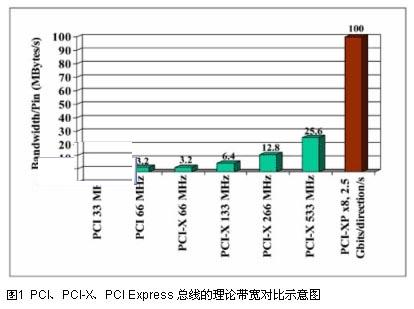

還將就PC 總線技術(shù)的演變歷程、PCI Express 的物理層和軟件層、PCI Express 所能帶來的益處和競(jìng)爭(zhēng)優(yōu)勢(shì)以及此項(xiàng)嶄新技術(shù)在測(cè)量自動(dòng)化系統(tǒng)領(lǐng)域里預(yù)示的令人振奮的深遠(yuǎn)意義,做個(gè)整體技術(shù)

2019-05-10 07:00:07

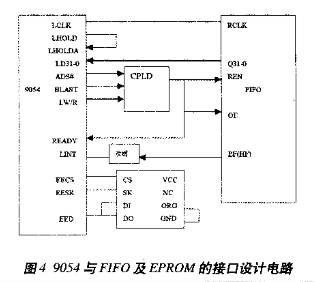

。PCI9054工作在初始化器模式時(shí),要求本地端的總線是32位的。在這里,用CPLD實(shí)現(xiàn)將80C51單片機(jī)的8位數(shù)據(jù)與16位地址轉(zhuǎn)換成32位的數(shù)據(jù)和地址,使用RAM的目的是提高8051的數(shù)據(jù)傳輸速度和處理復(fù)雜

2008-10-09 11:23:38

讀寫信號(hào)、BLAST#、READY#、ADS#和8051單片機(jī)相連。PCI9054工作在初始化器模式時(shí),要求本地端的總線是32位的。在這里,用CPLD實(shí)現(xiàn)將80C51單片機(jī)的8位數(shù)據(jù)與16位地址轉(zhuǎn)換成

2018-12-05 10:12:42

時(shí)鐘的下降沿信號(hào)會(huì)發(fā)生變化,而在時(shí)鐘上升沿信號(hào)必須保持穩(wěn)定。 1.2 CPLD設(shè)計(jì)規(guī)劃 出于對(duì)單片機(jī)和CPLD處理能力和系統(tǒng)成本的考慮,下面的規(guī)劃不支持PCI總線的線性突傳輸?shù)刃枰B續(xù)幾個(gè)數(shù)據(jù)周期的讀寫方式

2019-04-24 07:00:09

PCI總線是一種不依附于某個(gè)具體處理器的局部總線。從結(jié)構(gòu)上看,PCI是在CPU和原來的系統(tǒng)總線之間插入的一級(jí)總線,具體由一個(gè)橋接電路實(shí)現(xiàn)對(duì)這一層的管理,并實(shí)現(xiàn)上下之間的接口以協(xié)調(diào)數(shù)據(jù)的傳送。管理器提供了

2008-12-09 13:46:13

文章目錄存儲(chǔ)系統(tǒng)的層次結(jié)構(gòu)技術(shù)指標(biāo)層次結(jié)構(gòu)局部性原理主存儲(chǔ)器讀寫存儲(chǔ)器只讀存儲(chǔ)器存儲(chǔ)器地址譯碼主存空間分配高速緩沖存儲(chǔ)器工作原理地址映射替換算法寫入策略80486的L1 CachePentium

2021-07-29 09:47:21

存儲(chǔ)系統(tǒng)的層次結(jié)構(gòu)是怎樣的?怎么解決容量/速度和價(jià)格矛盾的問題?

2021-11-02 09:22:03

MMU。而一些復(fù)雜的系統(tǒng)可能包含一種或多種下面提到的技術(shù),從而提供功能更為強(qiáng)大的存儲(chǔ)系統(tǒng)。(1)系統(tǒng)中可能包含多種類型的存儲(chǔ)器件,一般都有Flash、SRAM、SDRAM等接口。(2)使用指令/數(shù)據(jù)

2022-04-20 09:23:59

的速度是480Mbits/s,完全可以滿足圖像采集、傳輸以及后續(xù)處理的要求。系統(tǒng)中采用 DSP+CPLD的硬件設(shè)計(jì)方案,采用現(xiàn)場(chǎng)可編程芯片 CPLD及兩片 SRAM構(gòu)成的圖像采集和存儲(chǔ)系統(tǒng),可以根據(jù)

2019-06-20 07:31:29

是480Mbits/s,完全可以滿足圖像采集、傳輸以及后續(xù)處理的要求。系統(tǒng)中采用 DSP+CPLD的硬件設(shè)計(jì)方案,采用現(xiàn)場(chǎng)可編程芯片 CPLD及兩片 SRAM構(gòu)成的圖像采集和存儲(chǔ)系統(tǒng),可以根據(jù)

2019-07-26 07:16:41

DMA),這是因?yàn)椋?b class="flag-6" style="color: red">系統(tǒng)DMAC完成實(shí)際的傳輸過程,所以它相對(duì)于傳輸過程的“前兩方”(傳輸?shù)陌l(fā)送者和接收者)來說是“第三方”。 標(biāo)準(zhǔn)DMA技術(shù)主要有兩個(gè)缺點(diǎn):(1)8237 DMAC的數(shù)據(jù)傳輸速度太慢

2019-07-01 08:10:07

界面圖。4 結(jié)束語基于PCI Express總線技術(shù)和Raid磁盤技術(shù)研制的高速大容量數(shù)據(jù)存儲(chǔ)系統(tǒng),其最高采樣速率可達(dá)210MHz,存儲(chǔ)容量為2TB。如果要擴(kuò)展存儲(chǔ)容量,只需更換Raid磁盤陣列控制卡并

2019-06-11 05:00:06

DVB-ASI碼流接收卡。如果使用支持64位PCI總線的PCI_MT64功能模塊,則最多可以實(shí)現(xiàn)8路ASI信號(hào)的接收。結(jié)語 本系統(tǒng)采用FPGA加PCI IP核的模式實(shí)現(xiàn)對(duì)高速、大容量DVB傳輸流的實(shí)時(shí)

2012-11-28 15:38:05

到底什么是云存儲(chǔ)?云存儲(chǔ)系統(tǒng)的結(jié)構(gòu)是如何構(gòu)成的?云存儲(chǔ)有哪些技術(shù)前提?

2021-06-02 06:27:45

其他單元的仿真測(cè)試提供配套的功能。ADLINK公司PCI-9846高分辨率高速數(shù)據(jù)采集卡在武器數(shù)據(jù)鏈測(cè)試系統(tǒng)中,以其寬動(dòng)態(tài)范圍、板載512MB內(nèi)存及不受PCI總線速率限制的突出特點(diǎn),助力武器數(shù)據(jù)鏈測(cè)試

2019-08-29 06:47:59

CPLD技術(shù)在PCI總線開關(guān)中的應(yīng)用使用CPLD技術(shù)開發(fā)PCI板卡有什么優(yōu)點(diǎn)

2021-04-08 06:47:28

器件及其解決方案l存儲(chǔ)系統(tǒng)架構(gòu)設(shè)計(jì)l數(shù)據(jù)存儲(chǔ)的可靠性、可用性、安全性l數(shù)據(jù)安全與備份容災(zāi)研究五、大會(huì)交流形式1、特邀演講:大會(huì)將邀請(qǐng)國(guó)內(nèi)外數(shù)據(jù)存儲(chǔ)技術(shù)領(lǐng)域的著名專家,就數(shù)據(jù)存儲(chǔ)技術(shù)的應(yīng)用和最新動(dòng)態(tài)做特邀

2014-04-25 14:43:18

, 因此如何來實(shí)現(xiàn)該監(jiān)控系統(tǒng)中大量數(shù)據(jù)的高效、快速、準(zhǔn)確地采集和傳輸成為設(shè)計(jì)該監(jiān)控系統(tǒng)所面臨的一個(gè)主要難題。而本文所研究的基于PCI 總線的高速數(shù)據(jù)通信卡的設(shè)計(jì)正是解決上述難題的關(guān)鍵技術(shù)之一。PCI

2010-09-22 08:51:09

性,因此本文選擇了PCI總線。33MHz、32位的PCI總線的數(shù)據(jù)傳輸速率最高可達(dá)133MBps, 完全可以滿足高速實(shí)時(shí)傳輸?shù)男枨蟆_x擇了Altera公司的PCI編譯器軟件包來實(shí)現(xiàn)PCI接口控制電路

2018-12-07 10:34:34

基于PCI總線的母板,該板上有自定義的總線接插件,可以插接其他基于該總線的數(shù)據(jù)采集DSP子板,此外,該板上還有整個(gè)系統(tǒng)的邏輯控制單元以及數(shù)據(jù)緩沖存儲(chǔ)芯片;其他各個(gè)功能模塊都基于該擴(kuò)展板來實(shí)現(xiàn);各個(gè)模塊

2009-04-20 10:51:10

獨(dú)立的配置空間,可實(shí)現(xiàn)即插即用。這些優(yōu)點(diǎn)使得PCI總線在數(shù)據(jù)采集、嵌入式系統(tǒng)和測(cè)控等領(lǐng)域得到廣泛應(yīng)用。實(shí)現(xiàn)PCI總線協(xié)議目前主要有專用接口芯片和CPLD實(shí)現(xiàn)兩種方式。專用接口芯片使用簡(jiǎn)單方便、工作穩(wěn)定

2019-05-29 05:00:02

可調(diào)用成員函數(shù)inw(),outw()實(shí)現(xiàn)。(4)中斷操作在本系統(tǒng)中的PCI中斷是由PCI設(shè)備發(fā)出的要求上位機(jī)接收數(shù)據(jù)的中斷請(qǐng)求,中斷服務(wù)程序要完成的功能是上位機(jī)從DSP的片內(nèi)RAM中讀取數(shù)據(jù)。對(duì)硬件

2018-12-17 11:29:06

設(shè)計(jì)高溫環(huán)境下(最高120°)基于FPGA的數(shù)據(jù)采集存儲(chǔ)系統(tǒng),就是通過傳感器采集數(shù)據(jù),通過FPGA來控制,把數(shù)據(jù)存儲(chǔ)到存儲(chǔ)芯片上,回頭可以通過接口讀取數(shù)據(jù)顯示在計(jì)算機(jī)上,求大師給我指導(dǎo),我急需整個(gè)系統(tǒng)的protel原理圖,請(qǐng)各位幫忙,我將感激不盡。最好有附件畫出整個(gè)原理圖,謝謝!

2012-10-29 21:37:12

服務(wù)平臺(tái)采用全芯片硬件設(shè)計(jì)方式無需任何CPU負(fù)載參與,將現(xiàn)有存儲(chǔ)系統(tǒng)應(yīng)用實(shí)現(xiàn)于一顆專用芯片。改變了現(xiàn)有傳統(tǒng)存儲(chǔ)架構(gòu),從而將存儲(chǔ)系統(tǒng)的各項(xiàng)指標(biāo)進(jìn)行了跨越式提升。帶寬可達(dá)640Gbps,存儲(chǔ)容量容量可達(dá)

2022-09-21 11:05:30

本文的應(yīng)用背景為某一工業(yè)測(cè)控系統(tǒng),該系統(tǒng)采用FPGA實(shí)現(xiàn)測(cè)量數(shù)據(jù)的采集和控制信號(hào)的輸出,通過定制PCI接口IP實(shí)現(xiàn)一個(gè)32位目標(biāo)設(shè)備的PCI總線接口轉(zhuǎn)換。PCI核選用AlteraPCI編譯器所包括

2018-12-04 10:35:21

基于SD卡的駕駛行為再現(xiàn)存儲(chǔ)系統(tǒng)設(shè)計(jì)摘要:本文以ABS 采集系統(tǒng)為基礎(chǔ),利用嵌入式技術(shù)設(shè)計(jì)了以SD 卡為存儲(chǔ)介質(zhì)的駕駛行為再現(xiàn)存儲(chǔ)系統(tǒng),對(duì)ABS 的數(shù)據(jù)進(jìn)行讀寫操作。本系統(tǒng)采用了目前通用的通信方式

2009-05-17 11:54:45

針對(duì)航天測(cè)試系統(tǒng)的應(yīng)用需求,利用FPGA的設(shè)計(jì)微型數(shù)字存儲(chǔ)系統(tǒng)勢(shì)在必行,那我們具體該怎么做呢?

2019-08-01 08:14:33

如何去設(shè)計(jì)微型數(shù)字存儲(chǔ)系統(tǒng)的硬件部分?如何去設(shè)計(jì)微型數(shù)字存儲(chǔ)系統(tǒng)的軟件部分?

2021-05-13 07:22:46

如何設(shè)計(jì)一個(gè)基于PC主機(jī)北橋的長(zhǎng)時(shí)間不間斷高速采集和存儲(chǔ)的系統(tǒng)。本文最后介紹了利用PC主機(jī)、PCI-E接口芯片PEX8311、Switch芯片PEX8616和RAID磁盤陣列卡,構(gòu)建一個(gè) 的實(shí)時(shí)海量存儲(chǔ)系統(tǒng)的案例。

2021-04-15 06:32:11

、衛(wèi)星、無線電、光電、激光等高頻物理信號(hào)),因試驗(yàn)、監(jiān)測(cè)及裝備的需要,對(duì)于原始信號(hào)的長(zhǎng)時(shí)間捕捉與存儲(chǔ)需求也日益增強(qiáng)。做為實(shí)現(xiàn)這些需求的手段,一般搭建一套高速數(shù)據(jù)采集存儲(chǔ)系統(tǒng)是比較常規(guī)的方式。坤馳科技做為

2019-07-04 06:08:14

本文提出了一種新的包括PCI9054單周期讀、寫和存儲(chǔ)器映射傳輸?shù)脑O(shè)計(jì),并討論了通用PCI總線高速數(shù)據(jù)采集卡的實(shí)現(xiàn)方案。

2021-06-08 06:28:30

怎么實(shí)現(xiàn)基于VW2010的視頻存儲(chǔ)系統(tǒng)的設(shè)計(jì)?

2021-06-03 07:14:51

夠這些“冷數(shù)據(jù)”能夠內(nèi)儲(chǔ)存到低成本、低能耗的媒介上,因而松下聯(lián)開發(fā)了一種基于freeze ray技術(shù)的光盤存儲(chǔ)系統(tǒng)。另據(jù)外媒報(bào)道稱,該光盤存儲(chǔ)系統(tǒng)是松下秘密與全球最大社交網(wǎng)平臺(tái)Facebook歷時(shí)

2016-01-06 18:23:32

PCI總線特點(diǎn)及開發(fā)現(xiàn)狀PCI接口配置空間的實(shí)現(xiàn)求一款在PCI總線上利用FPGA技術(shù)設(shè)計(jì)PCI總線接口的設(shè)計(jì)方案

2021-04-15 06:17:20

和防盜控制器互相存儲(chǔ)對(duì)方信息,校驗(yàn)碼中還摻雜了隨即碼,從而大幅提高防盜能力。校驗(yàn)信息通過Can-Bus傳遞大幅提高了信息傳遞的可靠性,使防盜系統(tǒng)的工作穩(wěn)定可靠。就目前而言,Can-Bus總線技術(shù)一般

2015-06-24 13:56:39

用CPLD設(shè)計(jì)所構(gòu)成的CPI接口系統(tǒng)具有簡(jiǎn)潔、可靠等優(yōu)點(diǎn),是一種行之有效的設(shè)計(jì)途徑。很多技術(shù)雜志和網(wǎng)站上,都有不少用CPLD設(shè)計(jì)PCI常規(guī)傳輸系統(tǒng)的文章。但用這些方法在MzxPlusII

2019-06-17 05:00:11

區(qū)間數(shù)灰色關(guān)聯(lián)分析的網(wǎng)絡(luò)存儲(chǔ)系統(tǒng)可生存性態(tài)勢(shì)定量評(píng)估方法。從規(guī)范化多指標(biāo)區(qū)間數(shù)決策矩陣出發(fā),結(jié)合待評(píng)估系統(tǒng)的實(shí)際評(píng)估要求,細(xì)化各指標(biāo),利用測(cè)試工具進(jìn)行數(shù)據(jù)采集,并通過定量評(píng)估方法對(duì)數(shù)據(jù)結(jié)果進(jìn)行處理,得到

2010-04-24 09:43:16

的實(shí)時(shí)性,因此本文選擇了PCI總線。33MHz、32位的PCI總線的數(shù)據(jù)傳輸速率最高可達(dá)133MBps, 完全可以滿足高速實(shí)時(shí)傳輸?shù)男枨蟆_x擇了Altera公司的PCI編譯器軟件包來實(shí)現(xiàn)PCI接口控制電路

2019-05-05 09:29:32

采用PCI總線流水式高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)摘要:目前基于PCI總線的高速數(shù)據(jù)采集系統(tǒng),大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來設(shè)計(jì),其通用性、靈活性差,不能

2009-10-30 15:09:49

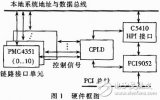

;計(jì)算機(jī)對(duì)結(jié)果數(shù)據(jù)進(jìn)行分析處理、按一定的標(biāo)準(zhǔn)進(jìn)行判別,將測(cè)試結(jié)果進(jìn)行顯示、控制分選機(jī)對(duì)被測(cè)器件進(jìn)行分選。1 PCI總線及其接口的實(shí)現(xiàn)自動(dòng)化集成電路測(cè)試系統(tǒng)(ATE)的結(jié)構(gòu)圖如圖1所示。本設(shè)計(jì)的接口總線選用

2019-05-30 05:00:02

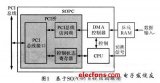

核處理器NIOSⅡ作為系統(tǒng)的主控制器,結(jié)合ARINC429專用器件和其他外圍設(shè)備實(shí)現(xiàn)數(shù)據(jù)的收發(fā)功能。 ARI NC429接口板由數(shù)據(jù)收發(fā)、存儲(chǔ)器擴(kuò)展、監(jiān)控、PCI總線接口等模塊組成。NIOSⅡ控制

2019-04-26 07:00:08

基于CPLD的系統(tǒng)中I2C總線的設(shè)計(jì) 摘要: 在介紹I2C總線協(xié)議的基礎(chǔ)上,討論了基于CPLD的系統(tǒng)中I2C總線的設(shè)計(jì)技術(shù),并結(jié)合工程實(shí)例設(shè)計(jì)了I2C總線IP核,

2008-08-13 13:43:38 31

31 目前基于PCI總線的高速數(shù)據(jù)采集系統(tǒng),大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來設(shè)計(jì),其通用性、靈活性差,不能很好地發(fā)揮PCI總線的性能。針對(duì)這些不足,在分析

2009-03-16 18:02:05 10

10 實(shí)時(shí)操作系統(tǒng)VxWorks下PCI總線配置技術(shù)

2009-03-29 12:26:26 19

19 基于PCI總線的高速數(shù)據(jù)采集卡系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn):本文介紹一種基于PCI總線的高速數(shù)據(jù)采集卡系統(tǒng)的設(shè)計(jì)方法,討論了設(shè)計(jì)高速數(shù)據(jù)采集系統(tǒng)的關(guān)鍵技術(shù),給出了系統(tǒng)整體設(shè)計(jì)方案和P

2009-06-22 19:04:54 44

44 本文結(jié)合ADLINK 公司的PCI-7300A_RevB 超高速數(shù)字I/O 卡的應(yīng)用,介紹一種大容量、高速、實(shí)時(shí)數(shù)據(jù)采集與存儲(chǔ)系統(tǒng)的實(shí)現(xiàn)方法。并根據(jù)自己的開發(fā)經(jīng)驗(yàn),指出實(shí)現(xiàn)過程中應(yīng)該注意的一些問

2009-08-07 09:58:20 14

14 本文針對(duì)干涉成像光譜儀,詳細(xì)分析了干涉成像光譜信號(hào)特征及其時(shí)序關(guān)系,研究了干涉成像光譜數(shù)據(jù)傳輸系統(tǒng)的關(guān)鍵技術(shù),提出了使用CPLD 技術(shù),設(shè)計(jì)基于微機(jī)PCI 總線的干涉成像

2009-09-01 08:21:37 17

17 針對(duì)數(shù)據(jù)加密算法的硬件設(shè)計(jì),主要討論了一個(gè)基于PCI 總線的數(shù)據(jù)加密系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)過程。首先對(duì)系統(tǒng)體系結(jié)構(gòu)以及在FPGA 芯片內(nèi)部對(duì)PCI 接口模塊的實(shí)現(xiàn)進(jìn)行了分析,然

2009-09-17 12:00:31 29

29 由高速圖像采集子系統(tǒng)和GPS 精密授時(shí)子系統(tǒng)構(gòu)成,為圖像采集提供精確的時(shí)間基準(zhǔn)。設(shè)計(jì)并實(shí)現(xiàn)了基于PCI 總線的GPS 時(shí)間獲取板卡,并完成了一系列軟件的設(shè)計(jì)開發(fā)。首先通過CPLD

2009-12-19 14:01:07 21

21 針對(duì)數(shù)據(jù)加密算法的硬件設(shè)計(jì),主要討論了一個(gè)基于PCI 總線的數(shù)據(jù)加密系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)過程。首先對(duì)系統(tǒng)體系結(jié)構(gòu)以及在FPGA 芯片內(nèi)部對(duì)PCI 接口模塊的實(shí)現(xiàn)進(jìn)行了分析,

2009-12-25 15:51:52 14

14 本文主要針對(duì)兩種不同F(xiàn)lash 的特征,在研究目前的Flash 存儲(chǔ)技術(shù)基礎(chǔ)之上,設(shè)計(jì)了一種數(shù)據(jù)存儲(chǔ)系統(tǒng),實(shí)現(xiàn)對(duì)數(shù)據(jù)進(jìn)行高速存儲(chǔ),其中在NorFlash 上保存NandFlash的有效塊列表,而

2010-01-20 14:52:27 4

4 基于CPLD 的雷達(dá)高度表高速大容量數(shù)據(jù)采集存儲(chǔ)系統(tǒng)設(shè)計(jì)作者:李貴新 袁嗣杰 轉(zhuǎn)貼自:微計(jì)算機(jī)信息摘 要:本文介紹了一種利用CPLD 器件作控制核心,基于SCSI 硬盤的雷達(dá)高

2010-01-27 14:18:26 22

22 PCI總線協(xié)議的FPGA實(shí)現(xiàn)及驅(qū)動(dòng)設(shè)計(jì)

摘要! 采用FPGA技術(shù)! 在公司的flex6000系列芯片上實(shí)現(xiàn)了從設(shè)備模式pci總線的簡(jiǎn)化協(xié)議!并給出了WIndowsx 系統(tǒng)下的虛擬設(shè)備驅(qū)動(dòng)程序

2010-03-12 14:30:27 36

36 PCI 9656是PLX公司設(shè)計(jì)的一款高速PCI I/O芯片,可應(yīng)用于66MHz、64bit PCI和CompactPCI總線。文章簡(jiǎn)述了PCI 9656的主要功能,介紹了一種應(yīng)用PCI 9656的CompactPCI數(shù)據(jù)接收卡設(shè)計(jì)。設(shè)計(jì)中采用MAXII系

2010-08-06 16:15:13 26

26 本文介紹一種基于PCI Express 總線的高速數(shù)據(jù)采集卡的設(shè)計(jì)方案及功能實(shí)現(xiàn)。給出系統(tǒng)的基本結(jié)構(gòu)及單元組成,重點(diǎn)闡述系統(tǒng)硬件設(shè)計(jì)的關(guān)鍵技術(shù)和本地總線的控制邏輯,詳細(xì)探

2010-09-22 08:15:04 62

62 摘 要: 本文采用Altera的CPLD實(shí)現(xiàn)了PCI總線至UTOPIA接口的邏輯轉(zhuǎn)換控制,為低成本實(shí)現(xiàn)ATM終端奠定了基礎(chǔ)。

2006-03-11 13:16:50 864

864

PCI Express總線技術(shù)白皮書

1.1 PCI Express總線的起源和現(xiàn)狀 2001年春季的IDF上Intel正式公布PCI Express,是取代PCI總線的第三代IO技術(shù),也稱為

2009-10-04 09:39:14 1031

1031

基于PCI總線多通道數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

摘 要:基于PCI總線的高速數(shù)據(jù)采集系統(tǒng)是近年來數(shù)據(jù)采集及其傳輸技術(shù)的一個(gè)發(fā)展方向。文中

2009-10-22 17:52:10 1312

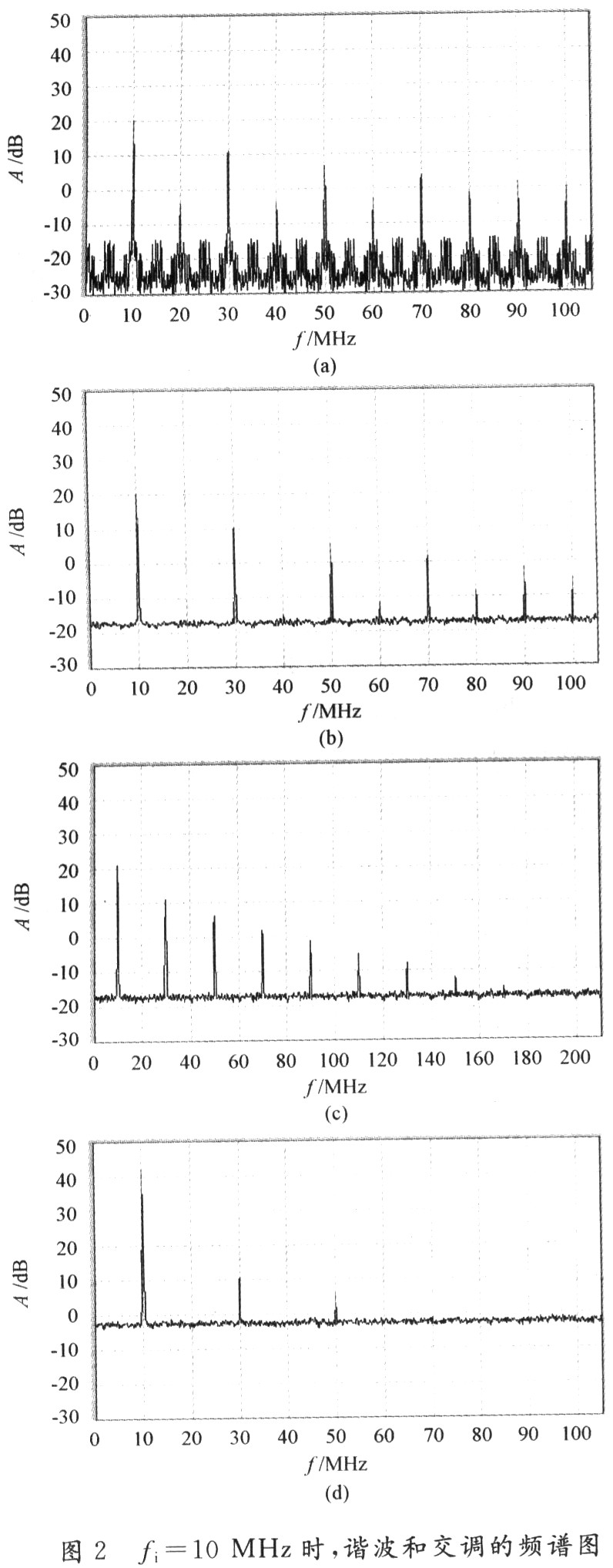

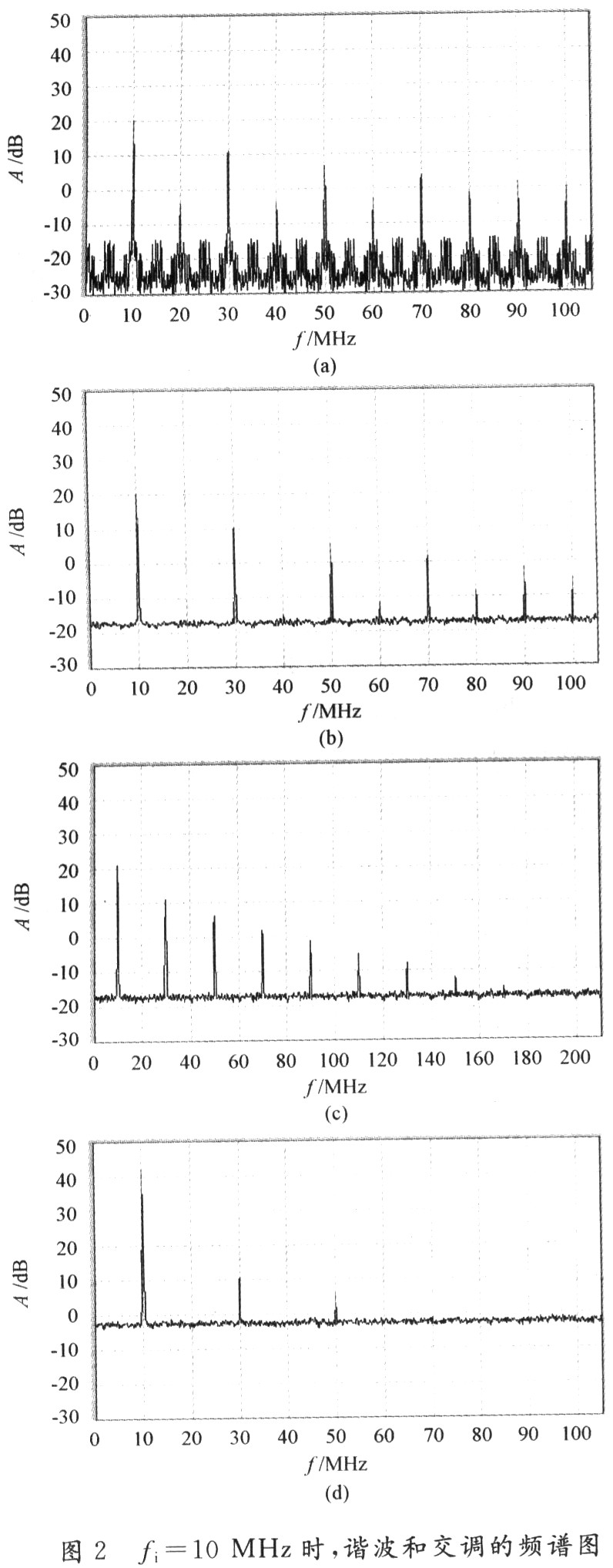

1312 數(shù)字射頻存儲(chǔ)系統(tǒng)關(guān)鍵技術(shù)仿真研究

0 引 言 數(shù)字射頻存儲(chǔ)器(DRFM)是現(xiàn)代電子對(duì)抗系統(tǒng)中有源雷達(dá)干擾機(jī)的主要組成部分,用于將接收到的雷達(dá)信號(hào)精

2009-11-10 09:48:59 630

630

PCI總線接口技術(shù)及其在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

一種基于PCI總線的高速數(shù)據(jù)采集傳輸系統(tǒng)的實(shí)現(xiàn),討論了PCI總線控制器9054的性能及三種傳輸模式,

2009-12-08 14:39:06 1016

1016

PCI總線的熱插拔技術(shù)及實(shí)現(xiàn)

摘要:具有熱插拔PCI槽現(xiàn)已成為許多需要長(zhǎng)時(shí)間不間斷工作和能夠在線維修的計(jì)算機(jī)系統(tǒng)的必備功能。文中介紹了

2010-03-03 19:27:08 1871

1871

提出了一種使用CPLD解決雙端口RAM地址譯碼和PCI接口芯片局部總線仲裁的的硬件設(shè)計(jì)方案,并給出了PCI總線接口芯片

2011-01-07 12:13:03 1891

1891

本文采用W78E516B單片機(jī)為核心來外擴(kuò)FM1808存儲(chǔ)器的存儲(chǔ)電路,并成功地運(yùn)用到了綜合驗(yàn)光儀的數(shù)據(jù)存儲(chǔ)系統(tǒng)中。該存儲(chǔ)系統(tǒng)降低了電路的復(fù)雜性,保證了數(shù)據(jù)的可靠,在整個(gè)綜合驗(yàn)光儀的使用中

2011-01-18 09:58:24 1655

1655

摘要:隨著數(shù)字信號(hào)處理技術(shù)和計(jì)算機(jī)技術(shù)的不斷發(fā)展,基于DSP的PCI總線數(shù)據(jù)采集系統(tǒng)將會(huì)得到越來越廣泛的應(yīng)用。以實(shí)際開發(fā)的系統(tǒng)為背景,詳細(xì)論述了基于DSP的PCI總線結(jié)構(gòu)的數(shù)據(jù)采集系統(tǒng)硬件及軟件設(shè)計(jì)方案和實(shí)現(xiàn)方法。 關(guān)鍵詞:DSP;PCI總線;驅(qū)動(dòng)模型;數(shù)字

2011-02-28 00:36:31 119

119 PCI數(shù)據(jù)總線技術(shù)規(guī)范 修訂版2.2 (PCI Local Bus Specification)

2011-03-23 10:17:12 32

32 分析當(dāng)前網(wǎng)絡(luò)存儲(chǔ)系統(tǒng)存在的問題,給出一種基于企業(yè)卷管理系統(tǒng)技術(shù)的帶外虛擬網(wǎng)絡(luò)存儲(chǔ)系統(tǒng)基本結(jié)構(gòu)。分別闡述該存儲(chǔ)系統(tǒng)的客戶端、內(nèi)部數(shù)據(jù)的讀/寫操作、存儲(chǔ)系統(tǒng)在線存儲(chǔ)容量

2011-05-18 18:50:31 38

38 基于CPLD的PWM控制器電路結(jié)構(gòu)簡(jiǎn)單,設(shè)計(jì)方便,簡(jiǎn)化了外部線路設(shè)計(jì),節(jié)省了PCB板空間,解決了機(jī)電一體化開發(fā)平臺(tái)中MCU模塊與功率模塊基于PCI總線的通信

2011-05-24 10:26:47 869

869

本內(nèi)容詳細(xì)介紹了高速數(shù)據(jù)采集與存儲(chǔ)系統(tǒng)技術(shù)方案

2011-07-07 17:43:53 69

69 超高幀頻實(shí)時(shí)圖像的長(zhǎng)序列采集存儲(chǔ)一直是難于解決的問題。本文基于SCSI 總線的理論體系,提出一種新的圖像數(shù)據(jù)采集存儲(chǔ)系統(tǒng)的技術(shù)方案和體系結(jié)構(gòu),并設(shè)計(jì)出一種超高速、數(shù)字化

2011-07-18 16:02:43 31

31 本文提出了一種基于PCI Express總線接口的、具備可擴(kuò)展性能、并可大容量存儲(chǔ)數(shù)據(jù)的采集系統(tǒng)。該系統(tǒng)的最高采樣速率可達(dá)80 MHz,利用計(jì)算機(jī)并通過PCI Express總線和采集卡、Raid磁盤陣列相

2011-08-31 15:02:16 1851

1851

本文利用“FPGA+單片機(jī)”作為存儲(chǔ)控制器,采用基于LZW算法的數(shù)據(jù)壓縮技術(shù),以SDRAM作為周期存儲(chǔ)和緩存,SD卡作為最終存儲(chǔ)載體,實(shí)現(xiàn)車載CAN總線記錄儀實(shí)現(xiàn)大容量存儲(chǔ)系統(tǒng)。

2011-09-08 16:24:59 2172

2172

出了一種PCI總線從設(shè)備的CPLD實(shí)現(xiàn)方法。該方法遵從PCI規(guī)范2.2版,實(shí)現(xiàn)了資源自動(dòng)配置并且支持數(shù)據(jù)突發(fā)傳輸。試驗(yàn)證明該方法的有效性,其突發(fā)傳輸速率可達(dá)20 MBs -1 。

2011-11-30 17:06:11 60

60 本文提出一種采用可編程片上系統(tǒng)SOPC實(shí)現(xiàn)偵察接收機(jī)PCI總線高速數(shù)據(jù)傳輸系統(tǒng)的設(shè)計(jì)方案。

2012-02-10 11:20:05 1350

1350

的重要基礎(chǔ)。對(duì)如何保證云存儲(chǔ)系統(tǒng)的服務(wù)質(zhì)量及可靠性,對(duì)于保證海量用戶的訪問效率,維護(hù)海量數(shù)據(jù)存儲(chǔ)的可用性及用戶技術(shù)服務(wù)平臺(tái)的開發(fā)有著重大意義。

2013-01-25 16:48:24 62

62 安防視頻監(jiān)控系統(tǒng)之存儲(chǔ)系統(tǒng)選型及技術(shù)對(duì)比,有興趣的同學(xué)可以下載學(xué)習(xí)

2016-05-04 15:48:56 0

0 網(wǎng)絡(luò)存儲(chǔ)系統(tǒng)容錯(cuò)編碼技術(shù)進(jìn)展

2017-01-24 17:21:04 8

8 基于CPLD的SGPIO總線實(shí)現(xiàn)及應(yīng)用

2017-01-24 16:00:51 75

75 雙平面頁編程技術(shù),將寫入速度提高到30 MB/s,有效地滿足了圖像高速存儲(chǔ)的要求。針對(duì)數(shù)據(jù)的碼率匹配,通過構(gòu)建片內(nèi)FIFO緩存來實(shí)現(xiàn)。測(cè)試結(jié)果表明,所設(shè)計(jì)的數(shù)據(jù)存儲(chǔ)系統(tǒng)能夠穩(wěn)定地接收并存儲(chǔ)圖像數(shù)據(jù),而且具有很高的可靠性。

2017-11-18 05:26:03 3788

3788

進(jìn)行通信。但是HPI口總線是一個(gè)非常特殊的總線,它采用訪問寄存器的方式來進(jìn)行DSP內(nèi)部數(shù)據(jù)的讀寫,HPI口單純映射到PCI的I/O空間或者存儲(chǔ)器空間,有不可避免的缺點(diǎn)。本文提出了一種雙映射方法,成功地解決了這一問題,實(shí)現(xiàn)了DSP與PCI9052之間方便、高速的數(shù)據(jù)通信。

2018-07-12 14:41:00 1586

1586

由于采用了存儲(chǔ)虛擬化技術(shù),數(shù)據(jù)中心的運(yùn)維人員在日常管理與維護(hù)中通常無需對(duì)單一存儲(chǔ)設(shè)備進(jìn)行操作,而是通過存儲(chǔ)虛擬化控制器提供的統(tǒng)一界面,對(duì)存儲(chǔ)資源進(jìn)行管理。對(duì)存儲(chǔ)系統(tǒng)擴(kuò)容時(shí),可以靈活地根據(jù)需求、成本、項(xiàng)目預(yù)算等因素考慮采用利舊,對(duì)原有設(shè)備擴(kuò)容及采購(gòu)異構(gòu)存儲(chǔ)等多種方案,實(shí)現(xiàn)了業(yè)務(wù)的不中斷操作。

2018-08-16 18:03:18 6275

6275 說一說AI技術(shù)在存儲(chǔ)中的應(yīng)用,和對(duì)存儲(chǔ)系統(tǒng)帶來的創(chuàng)新性改進(jìn)。

2018-10-24 15:41:58 4084

4084 快照是存儲(chǔ)系統(tǒng)中的一種數(shù)據(jù)保護(hù)技術(shù),主要是實(shí)現(xiàn)數(shù)據(jù)的邏輯保護(hù)。所謂邏輯保護(hù),就是當(dāng)數(shù)據(jù)出現(xiàn)誤刪除或者病毒等原因?qū)е?b class="flag-6" style="color: red">數(shù)據(jù)破壞的情況。通過快照技術(shù),可以將數(shù)據(jù)恢復(fù)到某一個(gè)時(shí)間點(diǎn)的數(shù)據(jù)。

2019-09-02 10:54:03 815

815

實(shí)現(xiàn)PCI總線協(xié)議目前主要有專用接口芯片和CPLD實(shí)現(xiàn)兩種方式。專用接口芯片使用簡(jiǎn)單方便、工作穩(wěn)定可靠,但往往具體應(yīng)用中只用到部分功能,并且需要可編程邏輯配合使用,這樣不僅浪費(fèi)專用芯片的資源,而且

2020-03-20 09:54:04 1268

1268

隨著計(jì)算機(jī)技術(shù)和存儲(chǔ)技術(shù)的發(fā)展,數(shù)據(jù)正以爆炸式的速度增長(zhǎng),海量數(shù)據(jù)對(duì)存儲(chǔ)系統(tǒng)提出了巨大的挑戰(zhàn)。為了保障存儲(chǔ)系統(tǒng)的CAP,Consistency(一致性)、 Availability(可用性

2020-07-11 11:29:24 3233

3233

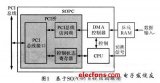

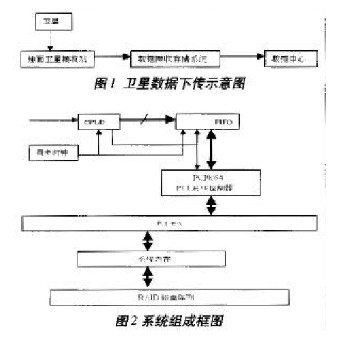

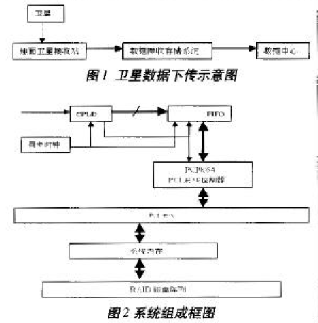

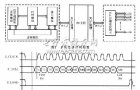

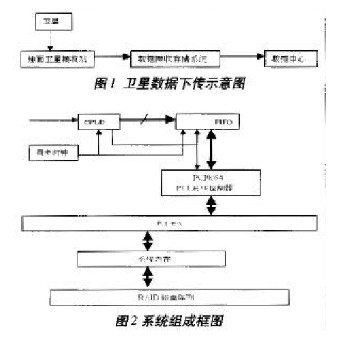

數(shù)據(jù)接收和存儲(chǔ)系統(tǒng)主要包括數(shù)據(jù)接收和預(yù)處理,數(shù)據(jù)傳送,數(shù)據(jù)存儲(chǔ)等部分。本文主要介紹CPLD,PCI總線結(jié)構(gòu),總線控制器PCI9054。其系統(tǒng)組成如圖2所示。

2020-08-12 16:39:56 4302

4302

系統(tǒng)中ADC板卡,DSP板卡以及其他 功能模塊之間的數(shù)據(jù)傳輸和控制通道,ADC板卡采集到的數(shù)據(jù)通過PCI總線主控模式高速傳輸?shù)紻SP板卡中進(jìn)行數(shù)字信號(hào)處理,實(shí)現(xiàn)接收機(jī)功能。結(jié)果表明, 該系統(tǒng)具有結(jié)構(gòu)簡(jiǎn)單,精度高等優(yōu)點(diǎn),并充分體現(xiàn)軟件無線電的靈

2020-11-19 17:48:01 13

13 針對(duì)硬盤存儲(chǔ)圖像速度慢、可靠性差的弊端,分析了以Flash作為存儲(chǔ)介質(zhì)的可行性,提出了一種基于閃存Flash的存儲(chǔ)系統(tǒng)設(shè)計(jì)方案。利用并行與流水線技術(shù)相結(jié)合,有效提高了存儲(chǔ)容量和操作速度。整個(gè)存儲(chǔ)系統(tǒng)

2021-03-23 15:44:59 10

10 。分布式存儲(chǔ)能增強(qiáng)存儲(chǔ)系統(tǒng)可靠性、柔性生存力、抗數(shù)據(jù)損毀風(fēng)險(xiǎn);是實(shí)現(xiàn)網(wǎng)絡(luò)熱點(diǎn)訪問負(fù)載均衡的技術(shù)途徑、提高邊緣計(jì)算的處理效率;能達(dá)成數(shù)據(jù)共享服務(wù)和隱私保護(hù)的便利性。 02 存儲(chǔ)系統(tǒng)局部再生修復(fù)技術(shù)的興起 數(shù)據(jù)編碼分布式存

2021-06-01 11:31:18 2275

2275 PCI總線的存儲(chǔ)器讀寫總線事務(wù) 總線的基本任務(wù)是實(shí)現(xiàn)數(shù)據(jù)傳送,將一組數(shù)據(jù)從一個(gè)設(shè)備傳送到另一個(gè)設(shè)備,當(dāng)然總線也可以將一個(gè)設(shè)備的數(shù)據(jù)廣播到多個(gè)設(shè)備。在處理器系統(tǒng)中,這些數(shù)據(jù)傳送都要依賴一定的規(guī)則

2021-07-18 10:06:12 2274

2274

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論