前言

在測控、儀器儀表、語音信號處理和圖像通信領域中往往需要多處理器分工完成數字信號處理(DSP)算法和與外部系統的通信、控制、數據采集和人機接口功能。在多機系統中,CPU之間的通信常采用以下幾種方式:(1)串行通信。這種方式相對簡單,由于受到波特率的限制,在不同檔次單片機之間需要通信業務大的場合得不到很好的通信效果。(2)并行通信。利用CPU的I/O功能在CPU之間增加緩沖器或鎖存器實現雙機通信。通信性能較串行通信有所提高,但仍然得不到理想的效果。(3)利用共享式存儲器實現。DMA方式就是其中的一種,能夠達到數據的高速傳輸,但不能同時訪問存儲器,CPU必須等待總線,而且有些CPU不支持DMA功能。另一種是利用多端口存儲器,雙口RAM和FIFO是常用的兩種多端口的存儲器,允許多CPU同時訪問存儲器,大大提高了通信效率,而且對CPU沒有過多的要求,特別適合異種CPU之間異步高速系統中。因此,受到硬件設計者的青睞。

一、兩種多端口存儲器

1.雙口RAM的仲裁控制

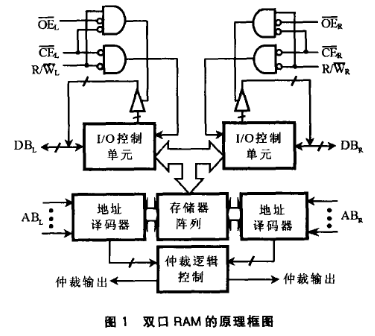

雙口RAM是常見的共享式多端口存儲器,以圖1所示通用雙口靜態RAM為例來說明雙口RAM的工作原理和仲裁邏輯控制。雙口RAM最大的特點是存儲數據共享。圖1中,一個存儲器配備兩套獨立的地址、數據和控制線,允許兩個獨立的CPU或控制器同時異步地訪問存儲單元。既然數據共享,就必須存在訪問仲裁控制。內部仲裁邏輯控制提供以下功能:對同一地址單元訪問的時序控制;存儲單元數據塊的訪問權限分配;信令交換邏輯(例如中斷信號)等。

(1)對同一地址單元訪問的競爭控制

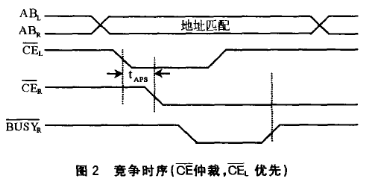

如果同時訪問雙口RAM的同一存儲單元,勢必造成數據訪問失真。為了防止沖突的發生,采用Busy邏輯控制,也稱硬件地址仲裁邏輯。圖2給出了地址總線發生匹配時的競爭時序。,此處只給出了地址總線選通信信號先于片選脈沖信號的情況,而且,兩端的片選信號至少相差tAPS――仲裁最小時間間隔(IDT7132為5ns),內部仲裁邏輯控制才可給后訪問的一方輸出Busy閉鎖信號,將訪問權交給另一方直至結束對該地址單元的訪問,才撤消Busy閉鎖信號,將訪問權交給另一方直至結束對該地址單元的訪問,才撤消Busy閉鎖信號。即使在極限情況,兩個CPU幾乎同時訪問同一單元――地址匹配時片選信號低跳變之差少于tAPS,Busy閉鎖信號也僅輸出給其中任一CPU,只允許一個CPU訪問該地址單元。仲裁控制不會同時向兩個CPU發Busy閉鎖信號。

(2)存儲單元數據塊的訪問權限分配

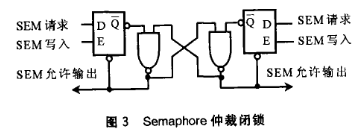

存儲單元數據塊的訪問權限分配只允許在某一時間段內由1個CPU對自定義的某一數據塊進行讀寫操作,這將有助于存儲數據的保護,更有效地避免地址沖突。信號量(Semaphore,簡稱SEM)仲裁閉鎖就是一種硬件電路結合軟件實現訪問權限分配方法。SEM單元是與存儲單元無關的獨立標志單元,圖3給出了一個信號量閉鎖邏輯框圖。兩個觸發器在初始化時均使SEM允許輸出為高電平,等待雙方申請SEM。如果收到一方寫入的SEM信號(通常低電平寫入),如圖3所示,仲裁電路將使其中一個觸發器的SEM允許輸出端為低電平,而閉鎖另一個SEM允許輸出端使其繼續保持高電平。只有當先請求的一方撤消SEM信號,即寫入高電平,才使另一SEM允許輸出端的閉鎖得到解除,恢復等待新的SEM申請。

(3)信令交換邏輯(signaling logic)

為了提高數據的交換能力,有些雙口RAM采用信令交換邏輯來通知對方。IDT7130(1K容量)就是采用中斷方式交換信令。利用兩個特殊的單元(3FFH和3FEH)作為信令字和中斷源。假設左端CPU向3FFH寫入信令,將由寫信號和地址選通信號觸發右端的中斷輸出,只有當右端的CPU響應中斷并讀取3FFH信令字單元,其中斷才被雙口RAM撤消。

以上是雙口RAM自身提供的仲裁邏輯控制,也可采用自行設計的仲裁協議。下面的實例將介紹這種方法。

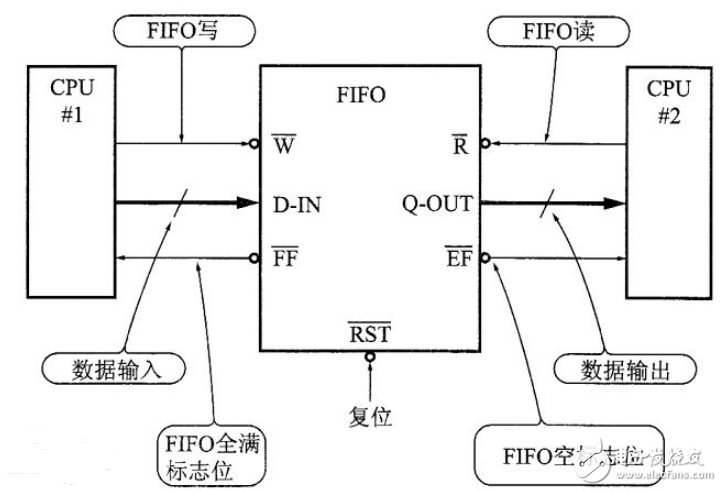

2.FIFO的工作原理

FIFO(First In First Out)全稱是先進先出的存儲器。先進先出也是FIFO的主要特點。

20世紀80年代早期,FIFO芯片是基于移位寄存器的中規模邏輯器件。容量為n的這種FIFO中,輸入的數據逐個寄存器移位,經n次移位才能輸出。因此,這種FIFO的輸入到輸出延時與容量成正比,工作效率得到限制。

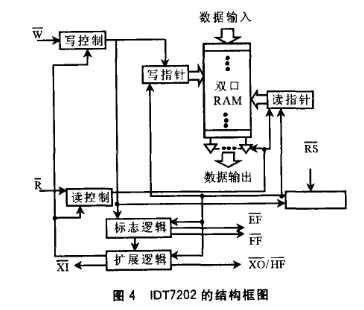

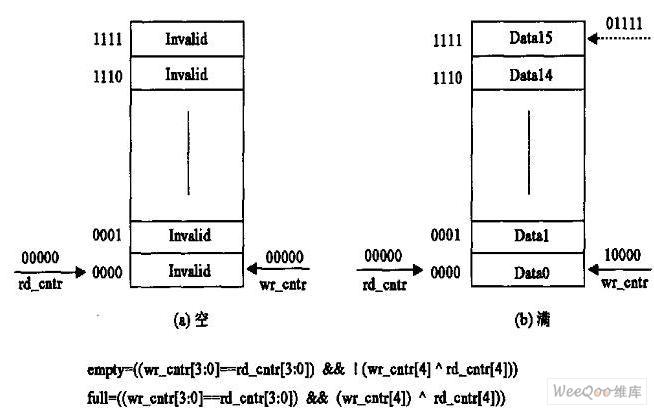

為了提高FIFO的容量和減小輸出延時,現在FIFO內部存儲器均采用雙口RAM,數據從輸入到讀出的延遲大大縮小。以通用的IDT7202為例,結構框圖如圖4所示。輸入和輸出具有兩套數據線。獨立的讀寫地址指針在讀寫脈沖的控制下順序地從雙口RAM讀寫數據,讀寫指針均從第一個存儲單元開始,到最后個存儲單元,然后,又回到第一個存儲單元。標志邏輯部分即內部仲裁電路通過對讀指針和寫指針的比較,相應給出雙口RAM的空(EF)和滿(FF)狀態指示,甚至還有中間指示(XO/HF)。如果內部仲裁僅提供空和滿狀態指示,FIFO的傳輸效率得不到充分的艇。新型的FIFO提供可編程標志功能,例如,可以設置空加4或滿減4的標志輸出。目前,為了使容量得到更大提高,存儲單元采用動態RAM代替靜態RAM,并將刷新電路集成在芯片,且內部仲裁單元決定器件的輸入、讀出及自動刷新操作。

FIFO只允許兩端一個寫,一個讀,因此FIFO是一種半共享式存儲器。在雙機系統中,只允許一個CPU往FIFO寫數據,另一個CPU從FIFO讀數據。而且,只要注意標志輸出,空指示不寫,滿指示不讀,就不會發生寫入數據丟失和讀出數據無效。

3.其他多端口存儲器

以上只介紹了兩種雙端口存儲器。隨著電子工藝的飛速發展,出現了三端口及以上的存儲器,并且在存儲深度和寬度上得到很大發展,仲裁邏輯控制更加復雜;但多端口存儲器源彼雙端口存儲器,基本更加復雜;但多端口存儲器源自雙端口存儲器,基本工作原理入雙端口存儲器相似,這里不一一詳述。

二、雙口RAM實現數據采集系統

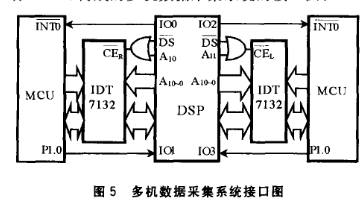

數字信號處理器(DSP)能實時快速地實現各種數字信號處理算法,而DSP的控制功能不強,可以采用8051單片機控制數據采集板,將采集的原始數據送給DSP處理并將處理結果傳送給8位單片機。圖5給出了利用1片數字信號處理器TMS320F206(以下簡稱DSP)和2片AT89C51單片機(以下簡稱MCU)構成多機數據采集系統接口圖。

本系統采用兩片CMOS靜態雙口RAM(IDT7132)實現MCU和DSP的數據雙向傳遞。雙口RAM作為DSP的片外數據存儲器,即用外部數據存儲器選通信號DS和高位地址信號經高速或門輸出選通雙口RAM的片選信號。這樣可以利用DSP的重復操作指令(RPT)和數據存儲器塊移動指令(BLDD)減少數據傳送時間,雙口RAM的8位數據總線接在DSP的低8位。IDT7132的仲裁邏輯控制只提供Busy邏輯輸出,而由于MCU無Busy功能,只能采用自行設計的軟件協議仲裁方法。將雙口RAM劃分為兩塊:上行數據區(DSP接收MCU采集的數據區)和下地數據區(DSP輸出處理結果區)。此處的上行數據區將遠大于下行數據區。采用DSP的4個I/O口與MCU中斷口和I/O口相連,并在數據區中規定一個信令交換單元。以DSP采集右端MCU上行數據為例,說明仲裁流程。

(1)初始化時,DSP置IO3為輸出口,保持高電平,IO2為輸入口(MCU使其初始化為低電平)。

(2)DSP需要采集MCU數據時,向右端IDT7132下行數據區的下行信令字單元(此處設為00H)寫入需要取數的信令字,再向右端MCU發中斷,置IO3為低電平,然后查詢IO2等待MCU應答。

(3)MCU及時響應中斷后,則先從IDT7132的下行數據區的下行信令字單元讀取DSP請求信息,檢測為DSP需要取數的下行信令。然后,向IDT7132上行數據區的上行信令字單元寫入數據,準備好需要DSP取數據的信令(00H)或數據未準備好的信令(01H)。最后,向DSP發送應答信號,置IO2為高電平(此處高電平的持續時間不過長,只要DSP可以檢測到即可)。

(4)DSP檢測到IO2為高是平,表明MCU應答,立即讀取IDT7132上行數據區的上行信令字單元。若為可以取數據的上行信令,則從IDT7132上行數據區取出采集數據,完成后,需要向右端MCU發送采集結束下行信令(01H);若為數據未準備好的上行信令(01H),則跳轉至與左端MCU通信程序中。

以下是DSP部分采集右端MCU數據的部分代碼:

rx1: splk #0020h,60h

out 60h,wsgr ;設置等待狀態寄存器,指令周期為50ns;而IDT7132選用55ns,則需插入1個等待狀態

splk #0000h,dn-sig ;向下行信令字單元寫入00h(dn-sig表示下行信令字單元),通知MCU需要接收上行的語音數據

call int0gr ;向右端MCU發中斷

reply:in 70h,iosr

bit 70h,12 ;檢測IO3

bcnd reply,ntc ;IO3為低,返回reply,繼續檢測

lacl up-sig ;讀上行信令字單元(up-sig表示下行信令字單元)到累加器中

sacl 70h

bit 70h,15

bcnd rx2,tc ;若為01H,表示MCU沒有準備好,跳之與另一MCU通信rx2處;為00H,表示允許采集數據

mar *,ar1

lar ar1,#data-buf ;將目的數據塊首地址存入ar1輔助寄存器

rpt #data-size ;重復下一條指令(data-size+1)次

bldd #up-data,*+

splk #0000h,dn-sig ;向下行信令字單元寫入01h,表示采集數據結束,讓出雙口RAM上行數據區的使用權

call int0gr ;向右端MCU發中斷

b rx2

RPT和BLDD是TMS320F206的高級指令,充分體現了DSP的流水線特點。RPT沒有時間開銷,它使下一條指令重復執行;BLDD是數據存儲器間塊移動指令,源和目的塊不一定都要在片內或片外。當RPT和BLDD一起使用時,中斷應該禁止,而且一旦流水線啟動,BLDD就變成了單周期指令,如上述程序,DSP采集100Byte的數據,指令周期為50ns,一個等待狀態周期則僅需50ns2100=10000ns=10μs,充分節省了采集時間,使DSP將更多的時間投入到算法中。

以下是產生中斷子程序:

int0gr:in 70h,iosr ;讀IO狀態寄存器到70H單元中

lacl 70h

and #0fffbh

sacl 71h

out 71h,iosr;置IO2為低電平,下跳變觸發INT0中斷

call wait1 ;延時,低電平的持續時間需滿足MCU接收中斷的要求

lacl 70h

or #0004h

sacl 71h

out 71h,iosr ;恢復IO2為高電平

ret

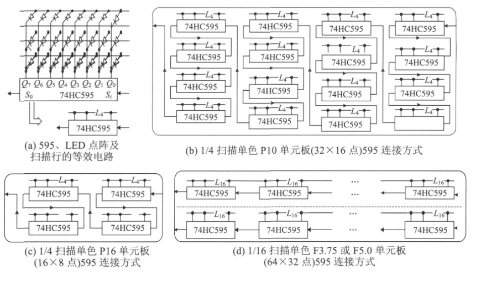

三、FIFO的雙向擴展和語音數據交換系統

用DSP實現語音壓縮和解壓算法得到了廣泛的應用。例如,用TMS320LC549可以實現基于G.723.1壓縮算法的全雙工語音編解碼器。G.723.1語音解碼器可將輸入的PCM編碼壓縮為6.3和5.3Kbps的語音數據,壓縮出的語音數據是每30ms突發輸出一幀。比如,6.3Kbps的速率,編解碼器每30ms輸出24Byte壓縮語音幀(包括信令數據),同樣,編解碼器每30ms突發接收24Byte語音數據解壓,輸出PCM編碼。為了實現語音數據的全雙工實時交換,可采用雙向FIFO設計交換系統。下面,以1片AT89C51(簡稱MCU)與2片TMS320LC549(簡稱DSP)實現語音數據雙向交換為例,介紹FIFO的具體應用。其中DSP用于語音數據的壓縮解壓;MCU用于轉發語音數據流和監控;FIFO用于CPU之間的數據緩沖。

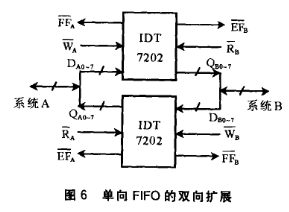

首先,用2片單向FIFO IDT7202擴展為雙向FIFO(也可使用專用的雙向FIFO),如圖6所示可以在A和B系統之間實現雙向通信。

圖7為語音雙向交換的原理簡圖(圖中未給出模擬話路和PCM編解碼器等)。MCU分別通過兩個雙向FIFO與相應的DSP實現語音數據交換。MCU對雙向FIFO的選通控制采用一片16V8GAL電路。DSP壓縮完一幀用中斷通知MCU取壓縮的語音數據。

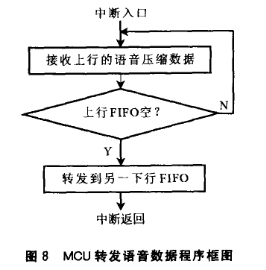

MCU在中斷服務程序中接收壓縮語音。圖8給出了MCU的中斷服務程序。如圖8所吉,MCU分別在兩個對等的中斷服務程序中,從上行的FIFO接收上行的語音數據,然后轉發給另一個下行的FIFO。DSP檢測下行FIFO的空標志。若為空間,則從下行的FIFO中接收需要解壓的語音數據,并對語音數據包解壓回放。

由上可以看出,利用FIFO實現多機接口,硬件和通信流程簡單,并且在實際的調試中,本系統的語音數據得到實時交換,沒有出現語音幀丟失的情況,語音延時符合要求,可以實現全雙工通信。

結束語

本文介紹了以雙口RAM和FIFO為例,利用多端口存儲器設計多機系統。現對雙口RA幾FIFO比較如下:(1)FIFO的仲裁控制簡單,但其容量不如雙口RAM。由于先進先出的特點,特別適合數據緩沖和突發傳送數據。某些芯片的內部就集成小容量FIFO,例如,DSP的同步串口就集成兩個FIFO,用于接收和發送數據緩沖。雙口RAM的仲裁邏輯比FIFO復雜,但其容量較大。由于存儲數據完全共享,適用于雙機系統的全局存儲器和大容量數據存儲共享,例如大容量磁盤的數據緩存可采用雙口RAM。(2)FIFO只給外部提供一個讀和一個寫信號,因此CPU用一個I/O地址便可讀或寫FIFO,使硬件趨于簡單,給編程也帶來一些方便,但CPU不能對FIFO內部的存儲器進行尋址。雙口RAM由于有兩套地址線,使硬件較FIFO復雜,但允許CPU訪問內部存儲單元,因此CPU之間可以自己定主和分配數據塊以及數據單元,使軟件設計更加靈活。

在異種機系統設計中,利用雙口RAM和FIFO能夠實時、快速、靈活和方便地進行相互通信,得到滿意的效果。

責任編輯:gt

電子發燒友App

電子發燒友App

評論