一、引言

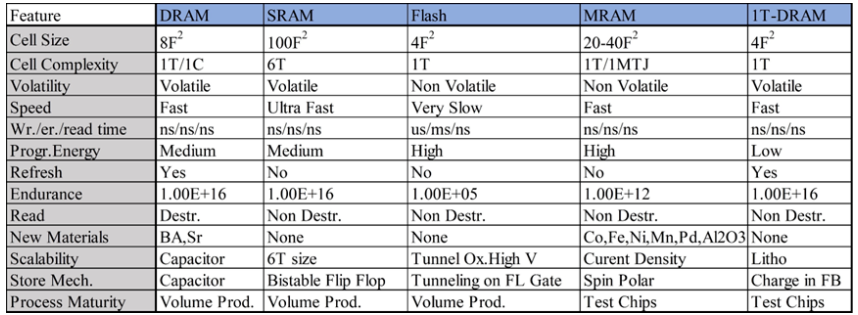

對(duì)大容量的高速低功耗嵌入式存儲(chǔ)器的需求不斷增加。通常有兩種存儲(chǔ)器,一個(gè)是嵌入式的靜態(tài)隨機(jī)存儲(chǔ)器(SRAM),另一個(gè)是嵌入式動(dòng)態(tài)隨機(jī)存儲(chǔ)器(DRAM)。SRAM有著很高的運(yùn)行速度,但是SRAM的存儲(chǔ)單元是由六個(gè)晶體管組成的,在大規(guī)模集成電路中SRAM存儲(chǔ)陣列將會(huì)占據(jù)很大的面積。此外SRAM存儲(chǔ)單元中晶體管需要相互匹配,這樣就會(huì)導(dǎo)致SRAM很難按比例縮小。由一個(gè)晶體管和一個(gè)電容組(1T-1C)成的嵌入式DRAM,不僅具有較快的運(yùn)行的速度還具有更小的單元面積。然而DRAM需要復(fù)雜的堆疊電容器或深溝電容器才能在較小的單元中獲得足夠的存儲(chǔ)電容。表一給出了1T-DRAM與其他存儲(chǔ)器的特點(diǎn)對(duì)比[1]。

基于這種情況,無(wú)電容的1T-DRAM被推出,1T-DRAM不需要復(fù)雜的存儲(chǔ)電容器,可以與邏輯器件有著良好的工藝兼容性。由于這獨(dú)特的優(yōu)勢(shì),近年來,無(wú)電容1T-DRAM作為下一代的DRAM引起了極大的關(guān)注。1T-DRAM使用體硅來積累硅薄膜中的多余的空穴載流子,1T-DRAM的存儲(chǔ)單元可以根據(jù)過剩載流子產(chǎn)生的機(jī)制分為不同的組,這些額外的載流子主要通過四種機(jī)制來實(shí)現(xiàn):1)碰撞電離;2)雙極型結(jié)型場(chǎng)效應(yīng)晶體管;3)帶間隧穿(BTBT)和4)柵極隧穿電流。

表一 1T-DRAM vs. 其他存儲(chǔ)器技術(shù)

本文將對(duì)這四種機(jī)制的1T-DRAM進(jìn)行分析,比較這四只機(jī)制的1T-DRAM之間的機(jī)理,通過對(duì)機(jī)理的分析得到不同機(jī)制的1T-DRAM的優(yōu)點(diǎn)和缺點(diǎn)。

二、碰撞電離機(jī)制的1T-DRAM

碰撞電離機(jī)制的1T-DRAM是最早被提出的1T-DRAM,隨著特征尺寸F的不斷縮小,DRAM和嵌入式DRAM的制造面臨著減小存儲(chǔ)單元面積的挑戰(zhàn),21世紀(jì)初DRAM芯片的單元采用的是1T/1C的結(jié)構(gòu),但是特征尺寸面積為8F2,減小單元尺寸的主要問題在于需要提供恒定電容值的電容,而電容的面積很難減小[2]。隨著SOI技術(shù)成為主流的技術(shù),SOI基底上制作1T/1C的DRAM是普遍采用的方法,但是在部分耗盡(PD) SOI MOSFET 中,器件工作過程中體充電是一個(gè)主要的問題,并努力的來抑制體充電效應(yīng)[3]。在這種情況下S. Okhonin首次提出了在SOI上制作1T-DRAM,它利用了體充電的效應(yīng),利用PDN或P-MOSFET的體中的正電荷或者負(fù)電荷來存儲(chǔ)“1”或“0”二進(jìn)制狀態(tài),當(dāng)體中多數(shù)載流子的增加導(dǎo)致電位和漏極電流的增加此時(shí)表示“ON”狀態(tài)( bit“1”),而當(dāng)多數(shù)電荷從體內(nèi)移除導(dǎo)致電流降低表示“OFF”狀態(tài)( bit “0”)。存儲(chǔ)單元的面積也實(shí)現(xiàn)了4F2的特征尺寸面積而且不需要額外制作電容的復(fù)雜步驟[2]。

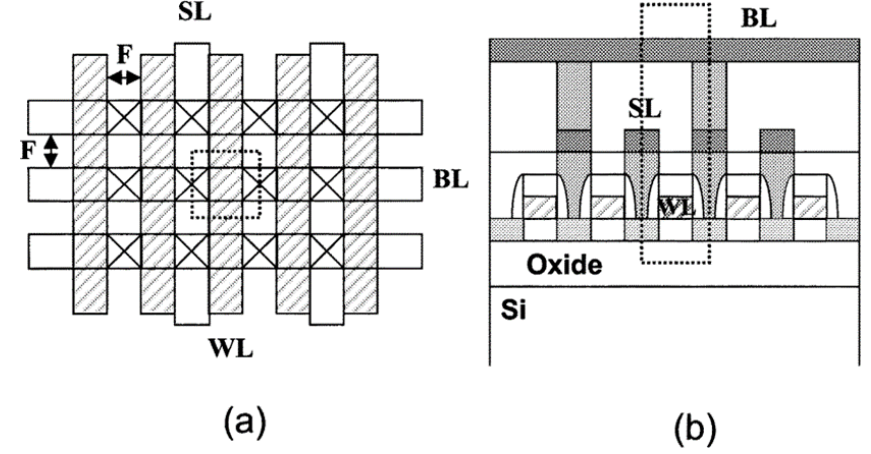

S. Okhonin提出的1T-DRAM采用的是0.25 μm 和0.13 μm PD SOI CMOS 技術(shù),這個(gè)1T-DRAM的存儲(chǔ)單元比當(dāng)時(shí)1T/1C存儲(chǔ)單元的面積至少小兩倍。圖一是該1T-DRAM的版圖和存儲(chǔ)單元的截面圖,該1T-DRAM在25nm的器件中寫入“1”和“0”都只需要3ns,在Vd低壓狀態(tài)(通常為0.2V到0.3V)下讀取數(shù)據(jù)不改變存儲(chǔ)單元的存儲(chǔ)狀態(tài),允許在低功耗操作的完整刷新間隔期間進(jìn)行非破壞性讀出模式,在1T/1C DRAM 中則是不被允許的,并且在1010次寫入“1”和“0”的情況下存儲(chǔ)的信息沒有衰減[4]。

圖一、4F2 1T-DRAM (a)版圖 (b)存儲(chǔ)單元截面圖

三、雙極型結(jié)型場(chǎng)效應(yīng)晶體管結(jié)構(gòu)的1T-DRAM[5]

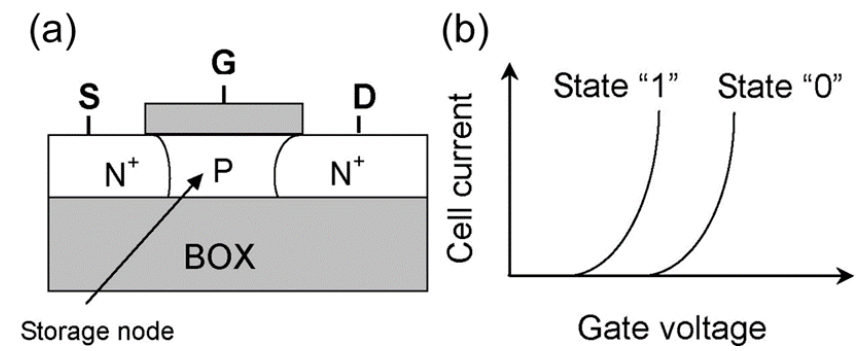

圖二、(a)碰撞電離機(jī)制的1T-DRAM存儲(chǔ)單元 (b)狀態(tài)“1”和“0”的Ig-Vg曲線

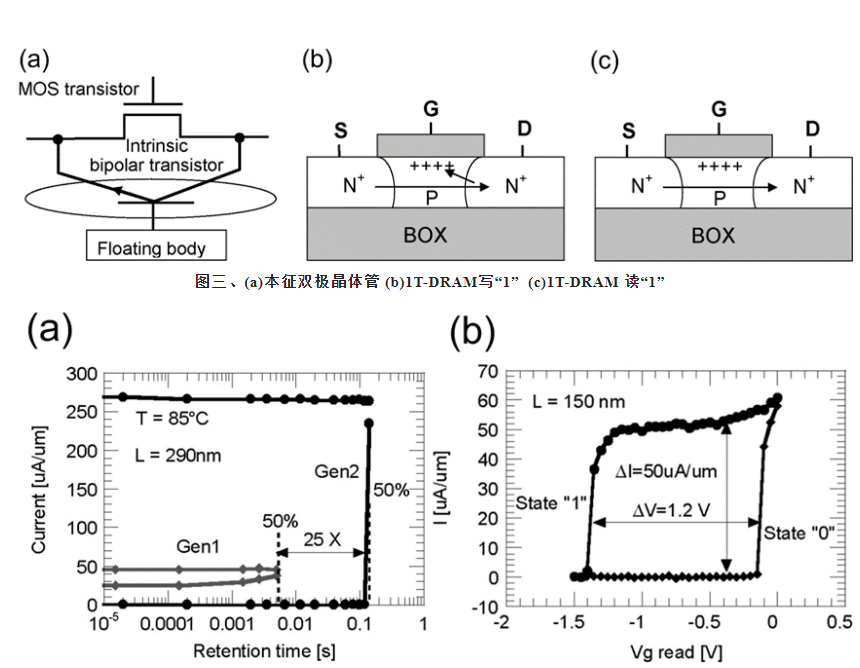

電離機(jī)制的1T-DRAM利用了晶體管的浮體充當(dāng)存儲(chǔ)節(jié)點(diǎn)(圖二a),利用通道中的碰撞電離產(chǎn)生多數(shù)載流子,浮體電荷可以引起晶體管的閾值電壓的偏離從而導(dǎo)致晶體管電流的改變(圖二b)。利用MOS器件中寄生的Bipolar晶體管來存儲(chǔ)數(shù)據(jù)的存儲(chǔ)單元如圖三(a)所示,在N溝道的MOS器件中N+源,P型襯底和N+分別構(gòu)成了NPN型Bipolar的發(fā)射極、基極和集電極。在碰撞電離機(jī)制中的1T-DRAM存儲(chǔ)單元中的浮體中產(chǎn)生過剩的多數(shù)載流子來寫“1”,在Bipolar結(jié)構(gòu)的1T-DRAM由Bipolar來產(chǎn)生多數(shù)載流子來寫“1”。利用雙極中的電流來讀取數(shù)據(jù),Bipolar為“ON”狀態(tài)時(shí)代表存儲(chǔ)的數(shù)據(jù)為“1”( 圖三(b) ),為“OFF”狀態(tài)時(shí)為數(shù)據(jù)“0” ( 圖三(c) ),通常寫“1”和讀“1”的電流會(huì)很大而寫“0”和讀“0”的電流會(huì)很小。與碰撞電離機(jī)制相比Bipolar結(jié)構(gòu)的1T-DRAM的數(shù)據(jù)保留時(shí)間更長(zhǎng),單元余量即“1”和“0”之間的差異會(huì)更大,更高的余量提供更快的數(shù)據(jù)讀取時(shí)間和更好的設(shè)備可擴(kuò)展性(圖四),并且Bipolar結(jié)構(gòu)比碰撞電離的1T-DRAM存儲(chǔ)單元中存儲(chǔ)電荷對(duì)雙極的電流有著更好的控制能力,并且不需要任何的背柵偏置,并且對(duì)陣列的訪問數(shù)據(jù)時(shí)間可以減小到2ns。

圖四、(a)同一晶體管上測(cè)量Gen1(碰撞電離 1T-DRAM)和(Bipolar 1T-DRAM)的保留和編程窗口 (b)Bipolar 1T-DRAM的編程窗口。

四、BTBT機(jī)制的1T-DRAM

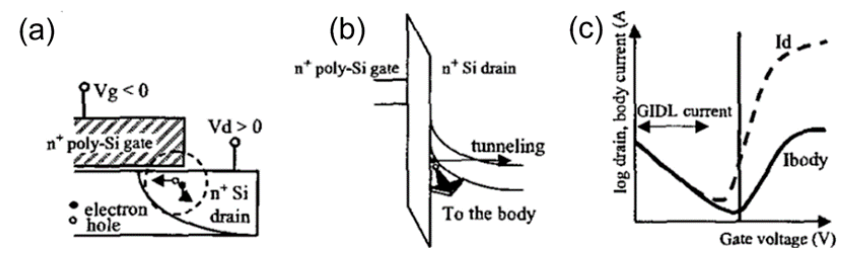

碰撞電離機(jī)制的1T-DRAM當(dāng)要提高寫入的速度時(shí),需要增加碰撞電流,增加碰撞電流會(huì)降低存儲(chǔ)器件的可靠性,因?yàn)闊彷d流子會(huì)注入到柵介質(zhì)中,利用GIDL電流進(jìn)行寫操作的1T-DRAM具有低功耗和高速操作的特性并有著更高的可靠性[6]。GIDL電流來自于帶間隧穿,在正柵極偏壓下和負(fù)漏偏壓下均會(huì)產(chǎn)生GIDL電流,BTBT機(jī)制的1T-DRAM的寫“1”操作如圖五所示[6,7]。在E. Yoshida提出的BTBT機(jī)制的1T-DRAM寫“1”最快僅需要1ns,在內(nèi)存的操作中可以比碰撞電離機(jī)制的1T-DRAM可以低四個(gè)數(shù)量級(jí)的功耗[6]。

圖五、(a)橫截面示意圖 (b)能帶圖 (c)GIDL電流曲線。GIDL 電流是由柵漏重疊區(qū)域中的帶間隧穿引起的

五、柵極隧穿電流機(jī)制的1T-DRAM

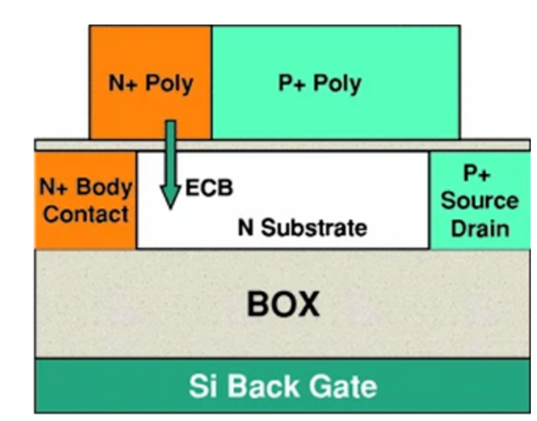

Guegan, G.提出了直接?xùn)艠O隧穿電流機(jī)制的1T-DRAM,存儲(chǔ)單元的原理圖如圖六所示。

圖六、柵極隧穿電流機(jī)制1T-DRAM原理圖

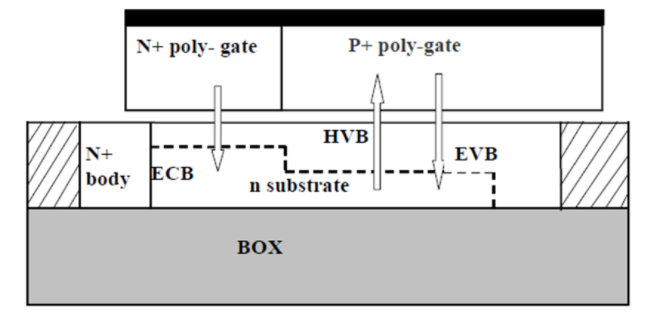

圖中可以看出柵極被分為N+和P+多晶硅柵,襯底也被分為兩部分左邊是一部分N+高摻雜的體接觸,右邊是N型襯底,柵和襯底之間是一個(gè)薄的氧化硅薄膜[8]。隧穿電流的機(jī)理圖如圖七所示,EVB和HVB分別代表的是來自N+多晶硅柵到硅襯底的電子隧穿電流和硅襯底價(jià)帶到P+多晶硅柵的空穴隧穿電流[8]。來自N+多晶硅柵的ECB電流是起主要作用的電流機(jī)制,N+多晶硅柵的勢(shì)壘高度只有3.1eV,電子密度較高,因?yàn)檫@個(gè)原因存儲(chǔ)單元采用了pMOSFET而不是傳統(tǒng)的nMOSFET。

圖七、強(qiáng)反型情況下主要的隧穿電流

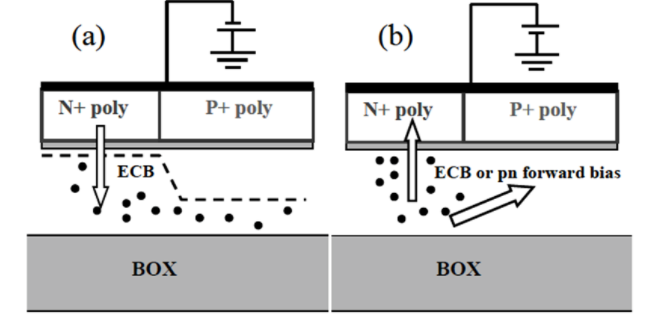

通過對(duì)體的中性區(qū)進(jìn)行電荷的注入和清除,1T-DRAM起到了保存“1”和“0”的二進(jìn)制狀態(tài)。寫“1”和寫“0”的原理如圖八所示,寫“1”時(shí)ECB電流注入到體中,寫“0”時(shí)通過正向偏置pn結(jié)和ECB隧穿電流同時(shí)清除體中的電子。柵極隧穿電流機(jī)制的1T-DRAM不需要大的偏置電壓,并且寫“1”時(shí)的功耗比碰撞電離機(jī)制和BTBT機(jī)制的1T-DRAM要分別小6到2個(gè)數(shù)量級(jí)[8,9]。

圖八、(a)寫“1”原理圖 (b)寫“0”原理圖

六、總結(jié)

傳統(tǒng)主流的DRAM存儲(chǔ)單元為1T/1C結(jié)構(gòu),相對(duì)于SRAM的六管存儲(chǔ)單元已經(jīng)非常小了,僅有6F2的特征尺寸面積,但是隨著人們對(duì)存儲(chǔ)容量的需求不斷增加,人們不得不尋找更小的存儲(chǔ)單元,由于1T/1C的結(jié)構(gòu)中電容需要有一定的容量電容不能隨著晶體管的尺寸縮小而縮小,因此1T-DRAM被提出來增加存儲(chǔ)容量,1T-DRAM僅有4F2的特征尺寸并且讀寫速度以及“1”和“0”的余量并沒有明顯的下降。1T-DRAM主要采用的機(jī)理有四種分別是離子碰撞、Bipolar結(jié)構(gòu)、BTBT機(jī)制和柵極隧穿電流機(jī)制,通過這四種機(jī)制向體浮體中注入電子,再通過檢測(cè)漏極電流來判斷存儲(chǔ)的是“1”還是“0”。碰撞電離機(jī)制的1T-DRAM最先被提出,它讀寫速度和單元余量符合要求,在經(jīng)過1010次讀寫后讀寫能力也沒有下降,滿足DRAM存儲(chǔ)器的基本要求。Bipolar結(jié)構(gòu)的1T-DRAM相對(duì)于碰撞電離機(jī)制的1T-DRAM的數(shù)據(jù)保留時(shí)間更長(zhǎng)、單元余量更大、更快的數(shù)據(jù)讀取時(shí)間、更好的數(shù)據(jù)擴(kuò)展能力并且不需要背柵控制并且電荷對(duì)電流的控制能力更強(qiáng)。碰撞電離機(jī)制的1T-DRAM當(dāng)要提高寫入的速度時(shí),需要增加碰撞電流,增加碰撞電流會(huì)降低存儲(chǔ)器件的可靠性,因?yàn)闊彷d流子會(huì)注入到柵介質(zhì)中,利用GIDL電流進(jìn)行寫操作的1T-DRAM具有低功耗和高速操作的特性并有著更高的可靠性。柵極隧穿電流機(jī)制的1T-DRAM不需要大的偏置電壓,并且寫“1”時(shí)的功耗比碰撞電離機(jī)制和BTBT機(jī)制的1T-DRAM要分別小6到2個(gè)數(shù)量級(jí)。

七、參考文獻(xiàn):

[1] Fazan, Okhonin, Nagoga, et al. Capacitor-less 1-transistor DRAM[C]。 2002 IEEE International SOI Conference, 2002: 10-13.

[2] Okhonin S, Nagoga M, Sallese J M, et al. A SOI capacitor-less 1T-DRAM concept[C]。 2001 IEEE International SOI Conference. Proceedings (Cat. No.01CH37207), 2001: 153-154.

[3] Yoshimi M, Terauchi M, Nishiyama A, et al. Suppression of the floating-body effect in SOI MOSFET‘s by the bandgap engineering method using a Si/sub 1-x/Ge/sub x/source structure[J]。 IEEE Transactions on Electron Devices, 1997, 44(3): 423-430.

[4] Okhonin S, Nagoga M, Sallese J M, et al. A capacitor-less 1T-DRAM cell[J]。 IEEE Electron Device Letters, 2002, 23(2): 85-87.

[5] Okhonin S, Nagoga M, Carman E, et al. New Generation of Z-RAM[C]。 2007 IEEE International Electron Devices Meeting, 2007: 925-928.

[6] Yoshida E, Tanaka T. A design of a capacitorless 1T-DRAM cell using gate-induced drain leakage (GIDL) current for low-power and high-speed embedded memory[C]。 IEEE International Electron Devices Meeting 2003, 2003: 37.6.1-37.6.4.

[7] Tanaka T, Yoshida E, Miyashita T. Scalability study on a capacitorless 1T-DRAM: From single-gate PD-SOI to double-gate FinDRAM[C]。 IEDM Technical Digest. IEEE International Electron Devices Meeting, 2004., 2004: 919-922.

[8] Guegan G, Touret P, Molas G, el al. A novel capacitor-less 1T-DRAM on partially depleted SOI pMOSFET based on direct-tunneling current in the partial n+ poly gate[J]。 Solid State Devices and Materials (SSDM), 2010.

[9] Bawedin M, Cristoloveanu S, Hubert A, et al.: Floating-Body SOI Memory: The Scaling Tournament, Nazarov A, Colinge J P, Balestra F, Raskin J-P, Gamiz F, Lysenko V S, editor, Semiconductor-On-Insulator Materials for Nanoelectronics Applications, Berlin, Heidelberg: Springer Berlin Heidelberg, 2011: 393-421.

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論