存算一體作為一種新型算力,有望解決傳統馮諾依曼架構下的“存儲墻〞、“功耗墻〞 問題,已被確定為算力網絡十大關鍵技術之一。存算一體將存儲與計算有機融合,以其巨大的能效比提升潛力,有望成為數字經濟時代的先進生產力。

本白皮書全面閘釋了存算一體的核心技術、發展路線、應用場景和產業鏈生態。希望產學研各界能凝聚共識、加強合作、協同發展,推動存算一體技術成熟和生態繁榮,加快存算一體產業化進程,助力我國在先進計算領域實現高水平自立自強。

存算一體是先進算力的代表性技術

回顧60多年計算行業的發展史,芯片的算力提升一直按照摩爾定律的節奏推進,但主流的計算范式始終遵循馮-諾依曼架構設計。進入二十一世紀,信息爆炸式增長,大規模數據處理成為挑戰,算力的需求呈現指數級提升,業界需要從各種維度探索芯片算力提升的方法。

1965年,戈登-摩爾歸納了晶體管的發展規律-摩爾定律,成為了丈量半導體行業技術進步、產品迭代和企業發展的標尺。然市,隨著半導體工藝逼近物理極限,摩爾定律的節奏明顯放緩,集成電路的發展進入后摩爾時代,業界主要從三大方向探索算力提升的技術路徑:“More Moore(深度摩爾)"、“More than Moore (超越摩爾)〞、"Beyond CMOS(新器件)〞,其中深度摩爾沿著摩爾定律的道路繼續推進,通過新型技術持續微縮晶體管提升計算密度;超越摩爾則是發展摩爾定律演進過程中未開發的部分,如先進封裝技術擴展計算性能;新器件則是探素除傳統硅基路線之外的芯片材料在計算產業的應用。三大方向為半導體行業延續高速發展的節奏提供了可能。

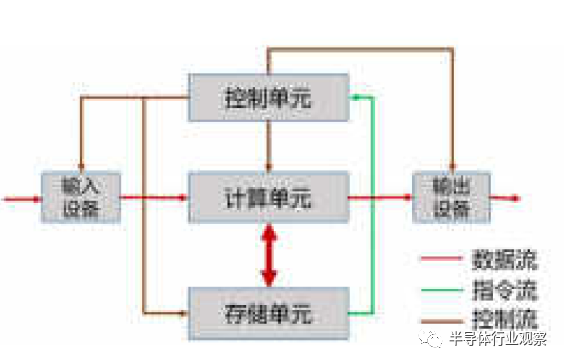

除了上述維度,業界也在通過變革當前計算架構來實現算力的突破。目前,主流芯片如CPU、 GPU (Graphics Processing Unit)、DPU(Data Processing Unit)均按照馮-諾依曼架構設計。馮氏架構以計算為中心(如圖1-1),計算和存儲分離,二者配合完成數據的存取與運算。

圖1-1:馮諾依曼架構

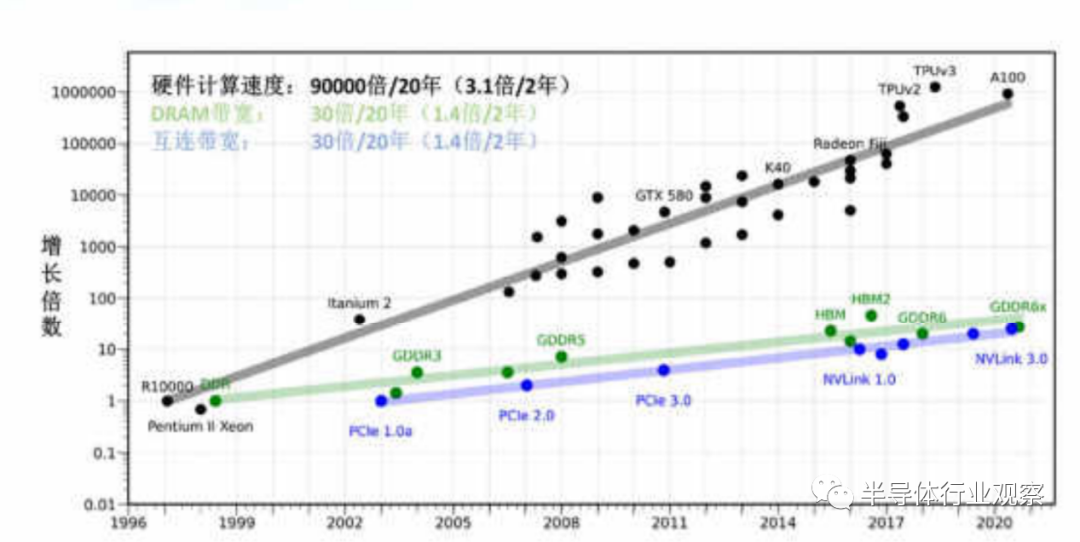

然而,由于處理器的設計以提升計算速度為主,存儲則更注重容量提升和成本優化,“存”“算〞之間性能失配 (如圖1-2),從而導致了訪存帶寬低、時延長、功耗高等問題,即通常所說的“〝存儲墻〞和“功耗墻”。訪存愈密集,“墻”的問題愈嚴重,算力提升愈困難。隨著以人工智能計算單元為代表的訪存密集型應用快速崛起,訪存時延和功耗開銷無法忽視,計算架構的變革顯得尤為迫切。

圖1-2:存儲計算性能剪刀差

存算一體作為一種新的計算架構,被認為是具有潛力的革命性技術,受到國內外的高度關注。核心是將存儲與計算完全融合,有效克服馮·諾依曼架構瓶頸,并結合后摩爾時代先進封裝、新型存儲器件等技術,實現計算能效的數量級提升。

存算一體技術路線建議

由于“墻〞的問題存在已久,業界已形成多種解決思路,包括對計算或存儲部件本身的性能提是升,以及存與算的協同優化,即存算一體技術。

目前學術界和工業界均在開展存算一體技術研究,學術界主要關注狹義的存算一體,即利用存儲介質進行計算;工業界關注商用化進程,著重宣傳廣義存算一體概念,但分類方法尚未完全統一。本章節將對廣義存算一體技術進行分類,望達成廣泛共識。

一、存算一體技術分類建議

根據存儲與計算的距離遠近,我們將廣義存算一體的技術方案分為三大類,分別是近存計算 (Processing Near Memory, PNM)、存內處理(Processing ln Memory.PlM) 和行內計算 (Computing in Memory, CIM)。存內計算即狹義的存算一體。

(1)近存計算 (PNM)

近存計算通過芯片封裝和板卡組裝等方式,將存儲單元和計算單元集成,增加訪存帶寬、減少數據搬移,提升整體計算效率。近存計算仍是存算分離架構,本質上計算操作由位于存儲外部、獨立的計算單元完成,其技術成熟度較高,主要包括存儲上移、計算下移兩種方式:

圖2-1:高帶寬內存方案

a.存儲上移:

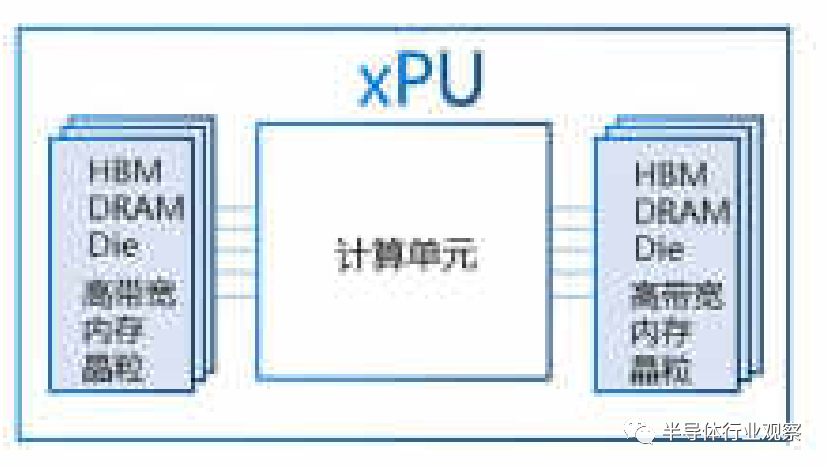

采用先進封裝技術將存儲器向處理器(如CPU、GPU)靠近,增加計算和存儲問的鏈路數量,提供更高訪存帶寬。典型的產品形態為高帶寬內存 (High Bandwidth Memory.HBM),將內存顆粒通過硅通孔 (Through Silicon Via,TSV)多層堆香實現存儲容量提升,同時基于硅中介板的高速接口與計算單元互聯提供高帶寬存儲服務,如圖2-1。

b.計算下移:

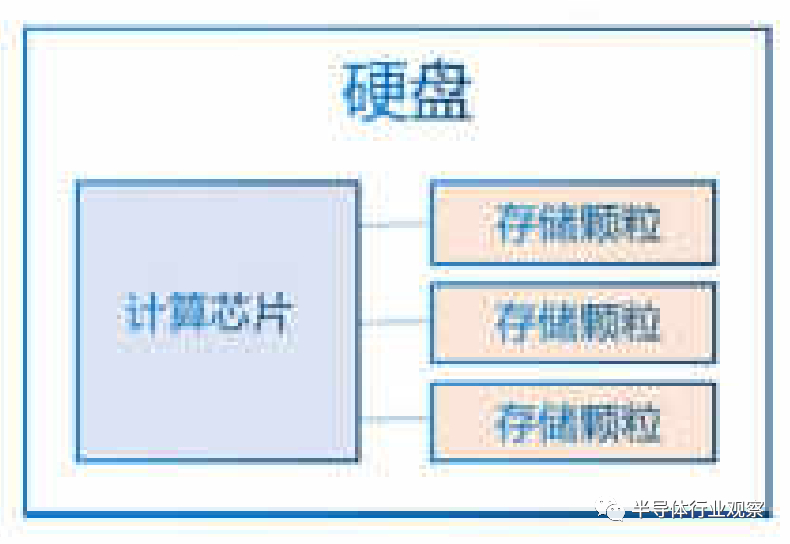

采用板卡集成技術將數據處理能力卸載到存儲器,由近端處理器進行數據處理,有效減少存儲器與遠端處理器的數據搬移開銷。典型的方案為可計算存儲 (ComputationalStorage Drives, CSD),通過在存儲設備引入計算引擎,承擔如數據壓縮、搜索、視頻文件轉碼等本地處理,減少遠端處理器(如CPU) 的負載,如圖2-2。

圖2-2:可計算存儲方案

近存計算已應用于人工智能、大數據、邊緣計算等場景,因其基本保持原有計算架構,產品化方案可較快投入使用。

(2)存內處理(PIM)

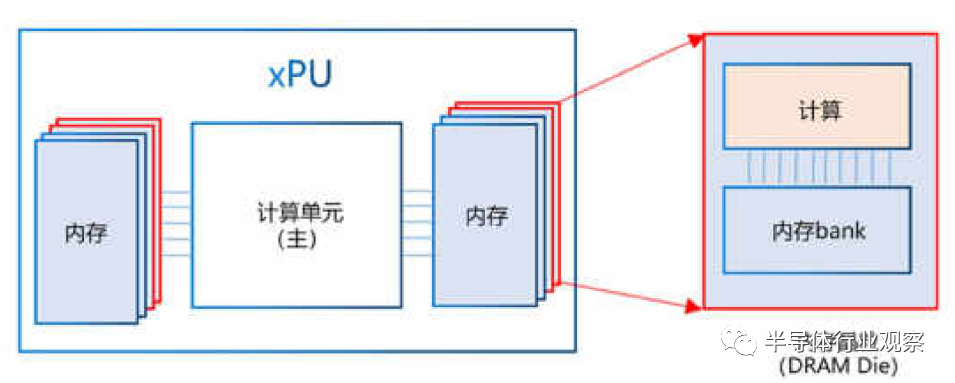

存內處理是在芯片制造的過程中,將存和算集成在同一個晶粒 (Die)中,使存儲器本身具備了一定算的能力。存內處理本質上仍是存算分離,相比于近存計算,〝存”與“算”距離更近。當前存內處理方案大多在內存(DRAM)芯片中實現部分數據處理,較為典型的產品形態為HBM-PIM和PIM-DIMM,在DRAM Die中內置處理單元,提供大吞吐低延遲片上處理能力,可應用于語音識別、數據庫索引搜索、基因匹配等場景,如圖2-3。

圖2-3:基于DRAM的PIM方案示例

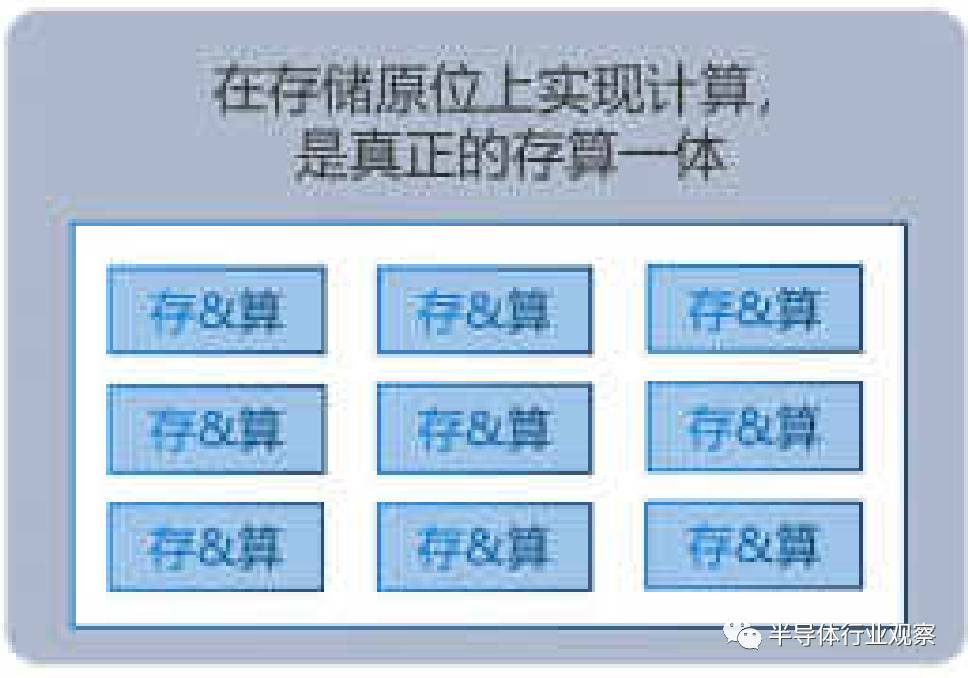

(3)存內計算(CIM)

存內計算即狹義的存算一體,在芯片設計過程中,不再區分存儲單元和計算單元,真正實現存算融合,如圖2-4。存內計算是計算新范式的研究熱點,其本質是利用不同存儲介質的物理特性,對存儲電路進行重新設計使其同時具備計算和存儲能力,直接消除“存〞“算〞界限,使計算能效達到數量級提升的目標。在存儲原位上實現計算

是真正的存算一體。

圖2-4:CIM存內計算

存內計算最典型的場景是為A算法提供向量矩陣乘的算子加速,目前已經在神經網絡領域開展大量研究,如卷積神經網絡 (ConvolutionalNeural Network,CNN)、循環神經網絡 (Recurrent Neural Network,RNN)等。存內計算有望激發人工智能領域的下一波浪潮,是廣義存算一體技術的攻關重點。

二、存內計算分析

1.存內計算原理

存內計算主要包含數字和模擬兩種實現方式,二者適用于不同應用場景。模擬存內計算能效高,但誤差較大,適用于低精度、低功耗計算場景,如端側可穿戴設備等。相比之下,數字存內計算誤差低,但單位面積功耗較大,適用于高精度、功耗不敏感的計算場景,未來可應用于云邊Al場景。一直以來,主流的存內計算大多采用模擬計算實現,近兩年數宇存內計算的研究熱度也在飛速提升。

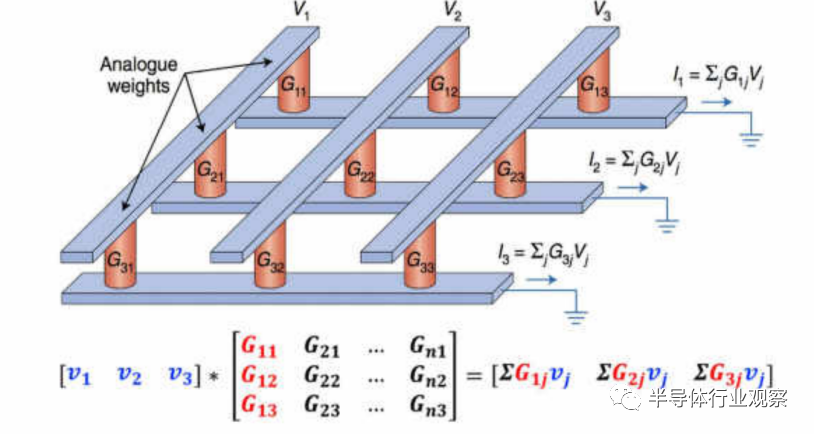

a.模擬存內計算

圖2-5:基于RRAM的模擬存內計算陣列

模擬存內計算主要基于物理定律(歐姆定律和基爾霍夫定律),在存算陣列上實現乘加運算。我們以存內計算介質材料之一阻變隨機存儲器 (Resistive Random Access Memory, RRAM,又名憶阻器)為例,來描述存內計算如何實現在數據寫入的同時完成計算。

憶阻器電路可以做成陣列結構,與矩陣形狀類似,利用其矩陣運算能力,可以廣泛應用于A!推理場景中。在Al推理過程中,通過輸入矢量與模型的參數知完成來加運算,便可以得到推理結果。

以矩陣乘加運算為例(如圖2-5所示),將模型的輸入數據設為矩陣M,模型的參數設為矩陣[G],運算后的輸出數據設為矩陣1。運算前,先將模型參數矩陣按行列位置存入憶阻器(即[G]),在輸入端給定不同電壓值來表示輸入矢量(即M),根據歐姆定律(電流=電壓/電阻),便可在輸出端得到對應的電流矢量,再根據基爾霍夫定律將電流相加,即得到輸出結果(即[I])。多個存算陣列并行,便可完成多個矩陣乘加計算。

由于整個運算過程無需再從存儲器中反復讀取大量模型參數,繞開了馮-諾依曼架構的瓶頸,能效比得到顯著提升。除憶阻器外,其他存儲介質也可通過不同的物理機制滿足同樣的并行計算需求。

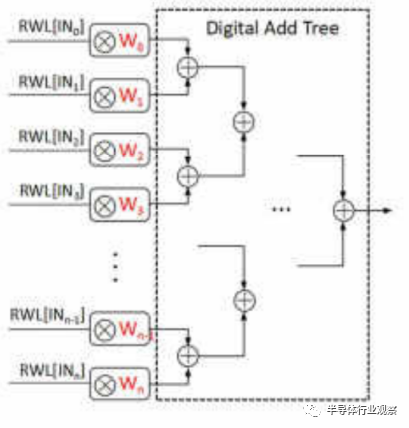

b.數字存內計算

數字存內計算通過在存儲陣列內部加入邏輯計算電路,如與門和加法器等,使數字存內計算陣列具備存儲及計算能力。我們以靜態隨機存儲器(Static Random-Access Memory, SRAM) 為例,來描述數字存內計算基本原理。

圖2-6:基于SRAM的數字存內計算加法樹

如圖2-6,輸入數據為向量[IN0IN1…INn],存儲單元中依次存入模型參數[W0W1…Wn],通過控制存儲器的讀字線 (Read Word Line, RWL),實現輸入數據與存儲單元內模型參數的乘法操作,通過數字加法樹[Digital and tree]實現累加,即可完成向量乘法運算。對多個向量重復以上過程,便可實現矩陣乘加計算。

數字存內計算的存儲單元只能存儲單比特數據,且需增加部分傳統邏輯電路,一定程度上限制了面積及能效優勢。因此,當前業界多采用可兼容先進工藝的SRAM來實現數字存內計算。

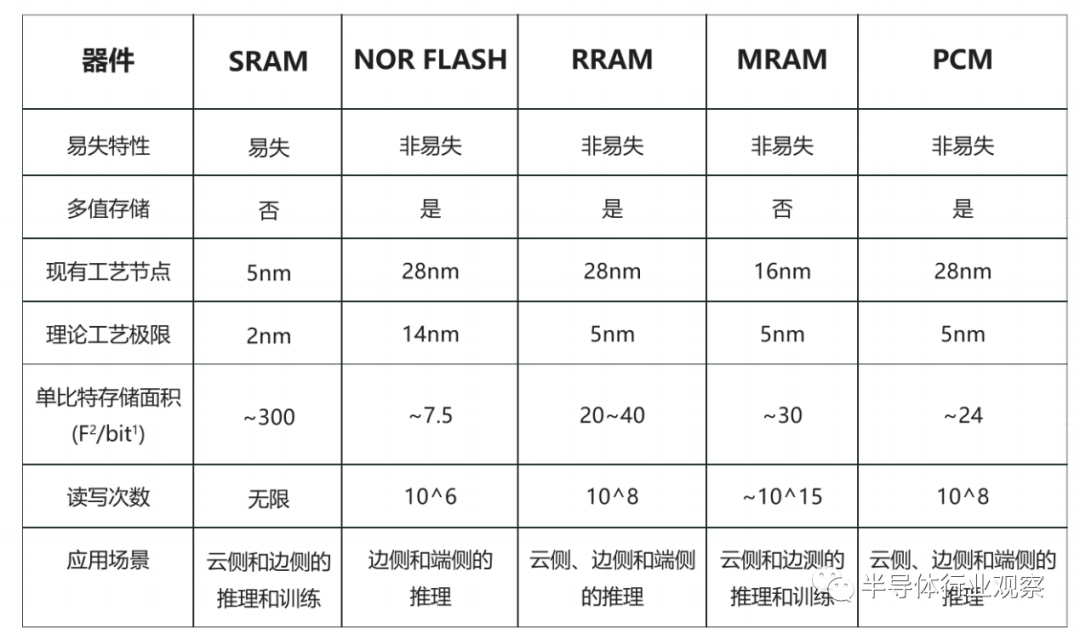

2.存內計算存儲器件分析與建議

存內計算電路可基于易失性存儲器和非易失存儲器件實現。易失性存儲器在設備掉電之后數據丟失,如SRAM等。非易失性存儲器在設備掉電后數據可保持不變,如NOR Flash、陽變隨機存儲器 (Resistive RandomAccess Memory, RRAM)、磁性隨機存儲器 (Magnetoresistive RandomAccess Memory, MRAM)、相變存儲器 (Phase Change Memory.PCM)等。本章主要對五種主流的存儲器件及其存內計算進行描述。

a.靜態隨機存儲器 (SRAM)

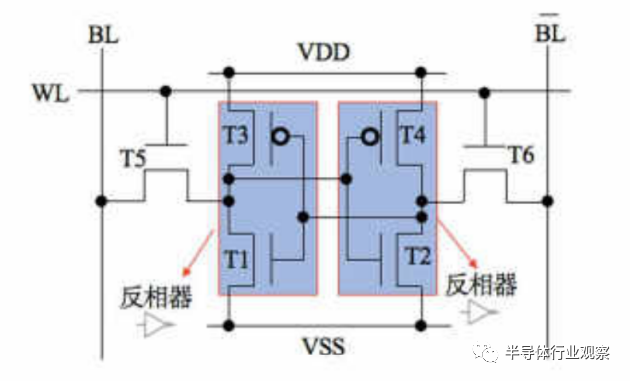

SRAM是應用范圍最廣的易失性存儲器之一,常用于CPU中的緩存,基本存儲單元由晶體管搭建而成,常見有6晶體管 (6T)、8晶體管 (8T)結構形式,圖2-7為6T SRAM基本單元結構。SRAM通過形成互鎖結構的兩個反相器來存儲數據,在設備供電時可保持存儲數據不變,掉電后存儲數據丟失,呈現易失性。

圖2-7:6T SRAM結構

SRAM讀寫速度快、無讀寫次數限制,且其工藝成熟,器件的一致性和穩定性較好,基于SRAM的全數字存內計算可以做到較高的計算精度,并且可以較快地實現技術落地與量產。但SRAM價格相對昂貴、多晶體管單元結構下存儲密度較低、需要通電以保持數據,因此芯片面積較大,功耗較高,不適用于對成本和功耗敏感的場景。

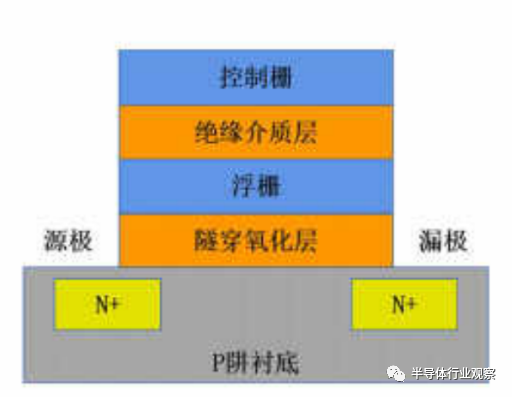

b.NOR FLASH

NOR Flash是一種非易失閃存器件,基本存儲單元為浮柵晶體管(如圖2-8所示),NOR Flash通過熱電子注入/隧穿效應控制浮柵中的電荷數量,每個單元可以存儲多比特信息。NOR Flash中浮柵被絕緣層分離以避免電荷泄露,供電消失后浮柵層仍能保持電荷數量不變,存儲信息不丟失,呈現非易失性。

圖2-8:Nor Flash浮柵晶體管

基于NOR Flash的存內計算芯片具有存儲密度大、工藝成熟、成本低等優點,業界主要利用其多比特存儲特性進行模擬存內計算,相關產品已在智能終端與邊緣場景實現小批量商用,帶來數十倍的計算能效提升。

然而,NOR Flash工藝微縮存在一定挑戰,為保證其性能與擴展性,需展開NOR Flash與先進工藝的3D/2.5D集成技術研究。

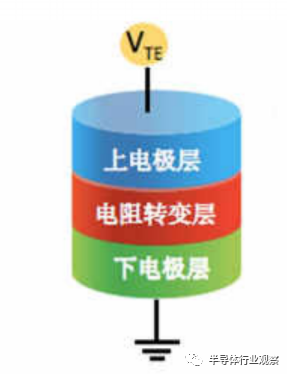

c.阻變隨機存儲器 (RRAM)

RRAM又被稱為憶阻器,是一種極具潛力的新型非易失存儲器件,基本存儲單元為金屬-絕緣體-金屬或者金屬-絕緣體-半導體的三明治結構。

圖2-9:RRAM結構示意圖

如圖2-9所示,上下為電極層,中間為絕緣的電阻轉變層。通過在電極層施加電壓/電流,電陽轉變層的電阻值可以實現高阻態和低阻態的切換,且電阻轉變層可以實現多級電阻狀態,使其可存儲多比特信息。

基于RRAM的存內計算芯片具有制備簡單、工藝成本低、時延低、支持多比特存儲、兼容先進工藝、支持了3D堆疊等諸多優點,被普遍認為擁有廣闊的發展前景。當前業界主要利用RRAM的模擬多比特特性進行模擬存內計算,可以達到較高的計算能效。

然而,RRAM目前在器件一致性和準確性等指標方面還有繼續提高的空間。

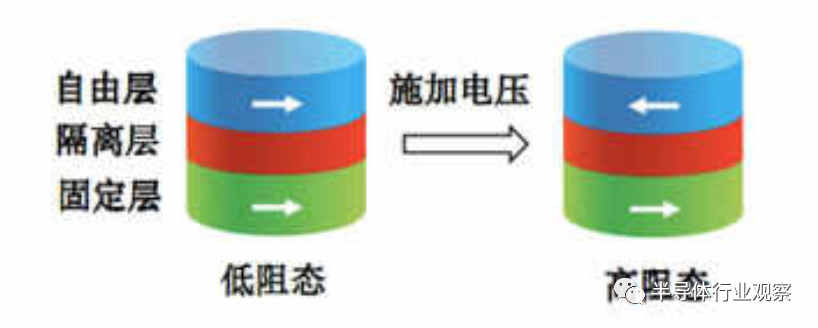

d.磁性隨機存儲器(MRAM)

MRAM是一種基于自旋電子學的新型非易失存儲器件,以磁隧道結(Magnetic Tunneling Junction, MTJ)為核心結構,利用隧道磁阻效應實現電阻狀態改變,達到存儲信息的目的。

2-10:磁隧道結結構

如圖2-10所示,MTJ是自由層-隔離層-固定層三明治結構。固定層的磁場方向保持不變,施加電壓可改變自由層的磁場方向,當白由層和固定層磁場方向一致時,器件呈現低阻態,代表邏輯“0”;當自由層和固定層磁場方向相反則為高阻態,代表邏輯“1”。

基于MRAM的存內計算芯片具有非易失、訪問速度快、讀/寫次數高等優點,目具備較高的可靠性和穩定性,但MRAM器件成熟度較低,功耗、速度和耐久性等指標離理論預期尚有一定差距。當前業界基于MRAM的存內計算研究較少,需要推動器件成熟,同步挖掘其在存算一體領域的潛在場景。

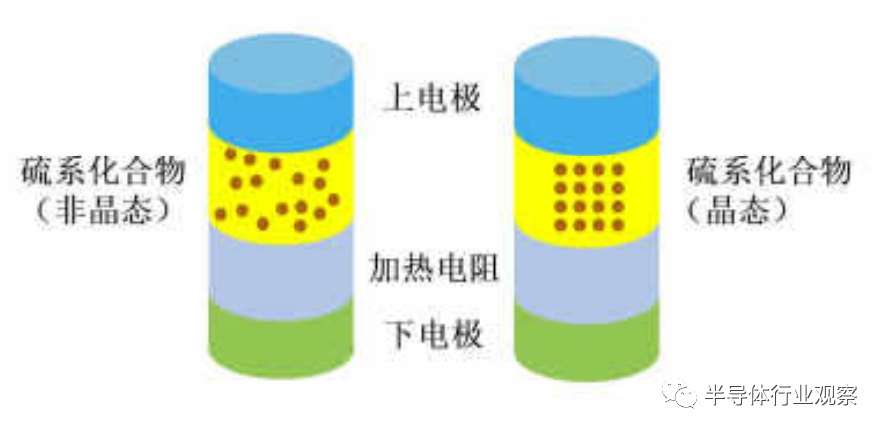

e.相變存儲器 (PCM)

PCM是一種由硫族化合物材料構成的非易失存儲器件。如圖2-11所示,PCM器件的典型結構為上電極、硫族化合物、電阻加熱器、下電極,通過在兩電極間施加不同形式的脈沖,對硫族化合物加熱使其在晶態和非晶態之間轉變,來表征高低阻特性,從而實現數據的存儲和控制。

2-11:PCM結構及阻態結構原理

PCM的狀態可以是介于完全多晶態和完全非晶態之問的多種狀態,并以此實現多值存儲。PCM斷電后狀態可保持不變,呈現非易失性。

PCM有非易失、存儲密度高、多比特存儲、支持了D堆疊等優點,但PCM存在寫入功耗較大、擦寫次數較少等問題尚需攻關,因此當前PCM主要還是作為大容量存儲器發展,基于PCM的存內計算研究相對較少,待產業進一步發展。

表1:存內計算結構對比分析

結合當前研究情況,表1對五種主流存儲器件的主要參數特征以及其存內計算適用場景進行了對比分析。整體來看,五種主流存儲器件各有優缺點,產品化選擇時需綜合考慮器件的成熟度、存儲密度、壽命、讀寫性能、能耗等多方面指標。當前NOR Flash、SRAM等傳統器件相對成熟,可率先開展存內計算產品化落地推動。新型器件中RRAM各指標綜合表現較好,MRAM壽命和讀寫性能較好,均有各自獨特優勢與發展潛力,可持續推動器件成熟,同步進行存內計算探索。PCM新器件成熟度相對較高,當前已可應用于近存計算研究,不過其壽命、能耗指標較RRAM無優勢,預計存內計算潛力稍弱,未來可能更多作為存儲器輔助存算一體整體技術發展。建議產業未來展開多路徑探索,實現各方案優勢互補,推動整體產業發展。

存內計算五大技術桃戰

廣義存算一體技術正由學術研究逐步走向商業應用,其中近存計算和存內處理在產品實現階段面臨制造和封裝技術門檻高的挑戰,在落地階段需要解決近、遠端處理器協同引起的軟件重構問題,但整體技術成熟。存內計算技術成熟度較弱,從器件研發及制造、電路設計、芯片架構、EDA工具鏈到軟件算法生態等諸多方面均需加強,對產業鏈各環節提出了更密切的協作需求。

一、新器件成熟度低,制造工藝難升級

存內計算在新器件成熟度方面問題突出。采用傳統及新型器件是實現存內計算的兩種重要方式。其中,NOR Flash、SRAM等傳統器件相對成熟,但RRAM、PCM、 MRAM等新型器件在器件一致性、擦寫次數、功耗、可靠性等方面存在差異化問題,影響存內計算產品在計算精度、壽命、能耗等方面的表現。

針對新器件引入,現有制造產線無法實現無縫切換,且現有工藝水平尚有提升空間。在芯片制造階段,需要制造商在已有產線流程基礎上進行改造,如在掩膜、設備調參等環節進行持續優化。此外,面向新器件的制程微縮無法完全沿用現有晶體管工藝路線經驗,新器件工藝兼容先進制程時,難以全面兼顧高可靠性、高精度等要求。

二、電路設計影響芯片算效提升

電路設計是存內計算芯片能效優勢的核心決定因素,整體技術尚未成熟。電路設計主要分為存算計算核(Macro)以及周邊電路兩大部分。

不同計算核的存算單元、電路連接設計存在不同,諸多前沿研發成果能效水平不一,尚未完成技術沉淀。周邊電路提供輸入輸出街接處理、計算核處理結果累加計算等能力,幫助芯片實現完整計算能力,該部分需要結合計算核進行適配設計,并保證較低的能耗和面積消耗。此外,模擬存內計算還涉及復雜的模數轉換器 (ADC)、數模轉專換器 (DAC)、跨阻放大器(TA) 等模塊,也為電路面積和能耗帶來技術挑戰。

三、芯片架構場景通用性及規模擴展能力較差

當前少量商用存內計算芯片產品的芯片算力較小,且主要面向端側特定領域實現,尚無成熟大算力芯片架構,無法為存內計算產品向云邊場景推動提供有效支撐。一方面,當前存內計算芯片支持的算子種類有限,難以滿足諸多神經網絡算法豐富的計算需求,缺三場景通用性。

另一方面,缺三成熟多核協同機制以及統一的片上互聯、片間互聯協議及標準,難以實現大算力芯片。

四、EDA工具鏈尚未健全

存內計算芯片設計與常規芯片有較大差異,當前EDA工具輔助設計與仿真驗證尚未成熟。具體表現在:

缺乏標準單元庫與快速組裝工具。不同存儲器件的存內計算芯片使用不同的存算單元結構,現有的EDA工具無法全面提供標準單元庫以供芯片設計 者使用,只能依賴手工繪制完成。此外,當前存內計算芯片產品化效率低,缺之自動化工具實現大規模存算陣列的快速組裝。

缺乏功能與性能仿真驗證工具。當前沒有面向存內計算場景進行仿真效率優化的工具,需要花費大量時問對存內計算的功能與性能進行仿真驗證,實現大規模存算陣列仿真時難度更高。

缺乏建模與誤差評估工具。建模與誤差評估的不準確會導致實際計算結果與理想結果產生偏差,如對器件的電路噪聲的模擬可以幫助開發者在設計階段進行方案評估并及時進行調整。

當前存內計算研究缺三相關工具來模擬器件ADC/DAC/TIA相關電路噪聲,給芯片設計方案評估和芯片可用性帶來挑戰。

五、軟件及算法生態不完善

缺乏通用開發環境和編譯器支持。為有效發揮存內計算芯片算力,編譯器需要將神經網絡模型算子映射到底層存算單元上,當前存內計算編譯器多為針對專用領域產品的個性化實現,缺少面向存內計算的通用開發環境和編譯器,以便達到向上對接不同算法,向下屏蔽底層存內計算硬件差異的目標。

神經網絡算法匹配問題存在桃戰。業界存在多種主流神經網絡模型量化方案,因模型特性而異,而當前存內計算所支持的量化方案較為單一,需要運用更多的訓練樣本,更多的迭代次數,更復雜的模型等途徑來彌補量化帶來的精度損失。

此外,存內計算適合高并行處理場景,但部分神經網絡應用將矩陣下的乘累加計算變得碎片化,其算法和芯片的計算特性不匹配,會導致硬件利用率低等問題。

存內計算五大發展建議

結合算力網絡業務發展訴求,我們提出存內計算發展建議,與業界共進,加速產業化進程。

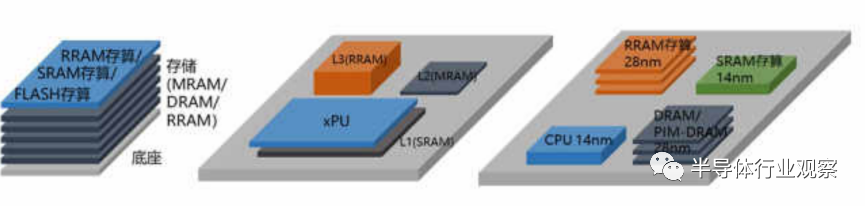

建議一:協同先進封裝技術,實現不同方案相結合

各種存儲器件的存內計算方案各有優勢,旦可與近存計算、存內處理方案結合,如協同2-5D/3D/Chiplet等先進封裝技術,將不同工藝、器件的存內計算芯片高度集成,實現優勢互補,兼顧成本、能效、性能、精度和通用性等方面指標,如圖所示。在此過程中,需推動RRAM、PCMMRAM等新型器件成熟并向先進工藝兼容,以充分發揮其能耗低、密度大等優勢。

建議二:優化電路與芯片架構,保障能效優勢和演進能力

電路設計和芯片架構對存算一體芯片實現高能效和通用性至關重要。

一方面,需加強存算陣列以及周邊模塊的電路設計能力,保障芯片整體的高并行度、低功耗優勢,另一方面,應構建可持續演進的通用存內計算芯片架構,來支持更大規模算力需求、更多算法及應用場景。

建議三:加速EDA工具孵化,縮短芯片研發周期

存內計算工業化進程需要EDA等產業鏈上游企業的廣泛支持。為保證芯片規模量產,需要芯片設計、EDA、制造商通力協作,打造涵蓋單元仿真、可靠性設計、低功耗設計、計算模塊設計等諸多環節的配套EDA工具,為存內計算芯片設計和仿真驗證提供有力輔助。此外,以存算一體為契機,可反哺推動國產EDA產業發展。

建議四:構建開發生態與編程框架,加速應用規模發展

為推動存內計算規模應用,相應開發環境與編譯平臺的建立成為必然訴求,需要業界共同發力,推進開源及標準生態,搭建面向存內計算的編程框架,健全自動化算法開發、仿真和編譯工具,構建針對存內計算并行計算特性的算法設計與開發生態。

建議五:產學研緊密協同,推動端側到云側演進

隨著存內計算應用范圍由邊側向云側逐步演進,需要推動產學研緊密協同,建立端到端技術棧。存內計算適用于音頻、 視頻、自動駕駛 決策分析等諸多應用場景,目前商用的NOR Flash、SRAM存內計算芯片主要用于中小算力需求的端側語音和視頻場景,未來可進一步實現通用大算力芯片,為云邊提供通信、自然語言理解、自動駕駛等場景高效算力服務。因此需要產學研緊密協同工作,構建鏈式合作平臺,拉通器件與芯片研發、工具鏈構建、軟件生態構建、產業發展、方案測試與應用的全鏈接。

產業發展倡議

針對狹義存算—體發展面臨的挑戰和問題,中國移動作為算力網絡新發發展理念的引領者和實踐者,希望與合作伙伴通力合作,圍繞技術、產業、生態三個方面開展工作,打通存算一體各環節產業鏈條,推動生態發展,加速產業化進程,真正釋放存算一體技術在性能與成本方面的巨大潛力,助力國家實現計算領域的原創科技創新和引領。

共同玫關存算一體核心技術。共同攻關新型材料、芯片架構、編譯器等領域的關鍵技術,共同挖掘存算一體應用場景,支撐國家新型算力基礎設施全新發展路徑,助力網絡強國、數宇中國、智慧社會發展戰略落地。

共同加快存算一體產業成熟。協同攻關存算一體產業鏈共性問題,推動產業鏈上下游、產供銷有效街接,提升產業鏈韌性,加強新技術對產業滲透的深度和廣度,探索存算一體試驗示范,協同推動加強產業鏈創新、健康發展。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論