EEPROM(Electrically Erasable Programmable read only memory)即電可擦可編程只讀存儲器,是一種掉電后數據不丟失(不揮發)存儲芯片。

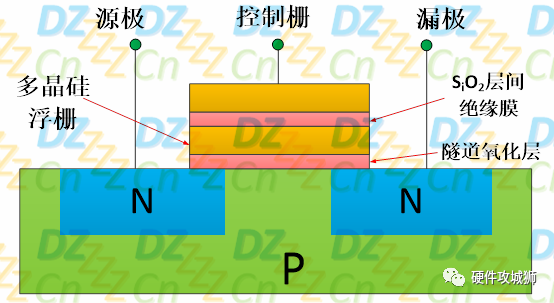

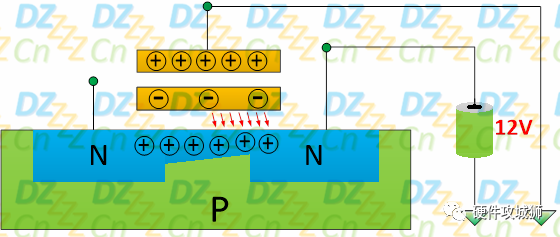

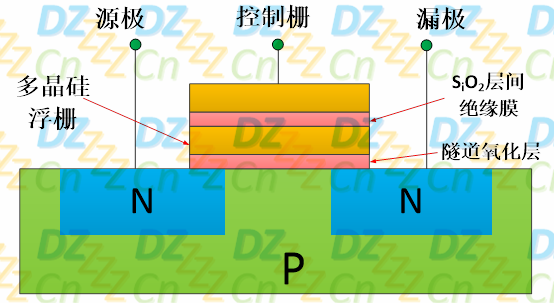

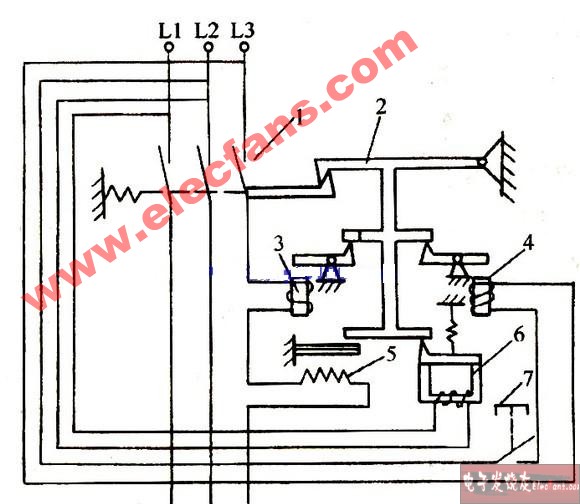

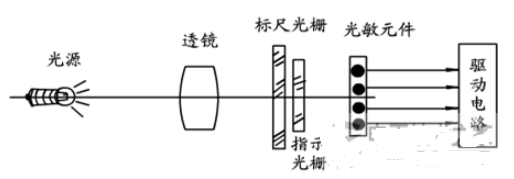

EERPOM的基本結構有幾種,這里講解比較常用的FLOTOX管結構,如下圖所示:

FLOTOX(Floating Gate Tunneling Oxide)MOS管即浮柵隧道氧化層晶體管,它是在標準CMOS工藝的基礎上衍生的技術。

如上圖所示,在傳統的MOS管控制柵下插入一層多晶硅浮柵,浮柵周圍的氧化層與絕緣層將其與各電極相互隔離,這些氧化物的電阻非常高,而且電子從浮柵的導帶向周圍氧化物導帶的移動需要克服較高的勢疊,因此,浮柵中的電子泄漏速度很慢,在非熱平衡的亞穩態下可保持數十年。

浮柵延長區的下方有個薄氧區小窗口,在外加強電場的作用下漏極與浮柵之間可以進行雙向電子流動,繼而達到對存儲單元的“擦除”與“寫入”操作。

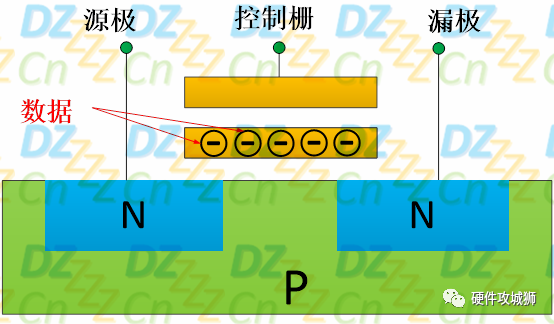

為強調浮柵周圍氧化物的絕緣效果,我們把絕緣層去掉,如下圖所示,其中的“電子”就是我們需要存儲的數據:

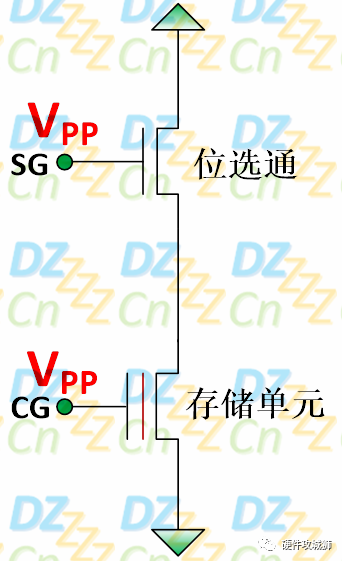

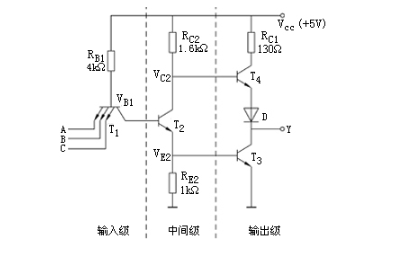

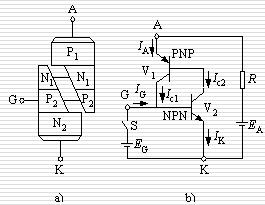

其原理圖符號如下所示:

我們通常利用F-N隧道效應(Fowler-Nordheim tunneling)對EEPROM存儲單元進行“擦除”或“寫入”操作,簡單地說,即FLOTOX管的控制柵極與漏極在強電場的作用下(正向或負向),浮柵中的電子獲得足夠的能量后,穿過二氧化硅層的禁帶到達導帶,這樣電子可自由向襯底移動(具體細節可自行參考相關資料,此處不贅述)。

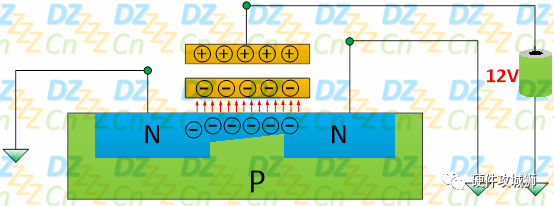

對EEPROM存儲單元進行“擦除”操作,就是將電子注入到浮柵中的過程(不要將此處的“擦除”操作與FLASH存儲單元中的“擦除”操作弄反了,具體參考FLASH對應文章),如下圖所示:

如上圖所示,將FLOTOX管的源極與漏極接地,而控制柵極接高壓(不小于12V),浮柵與漏極之間形成正向強電場,電子從漏極通過隧道氧化層進入浮柵。

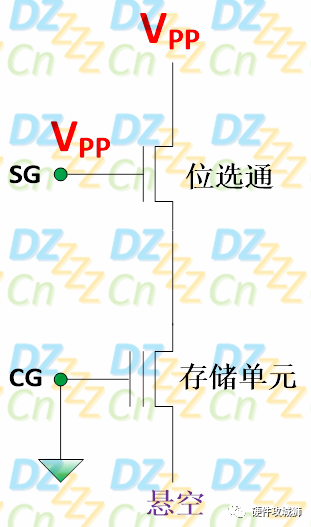

為防止存儲單元“擦除”(或“寫入”操作)對其它單元產生影響,每個FLOTOX管均與一個選通管配對(按照制造工藝可分為N管與P管,這里我們以N管為例進行講解,P管是類似的),前者就是存儲電子的單元,而后者用來選擇相應的存儲單元的控制位,這種結構導致單位存儲面積比較大,因此,EEPROM存儲芯片的容量通常都不會很大。

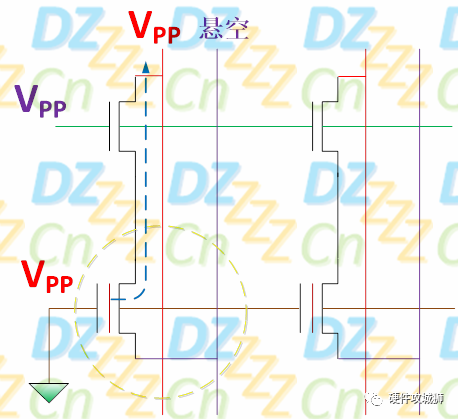

一個bit位的存儲單元電路狀態如下圖所示:

其中,SG表示選通管的選通柵(Select Gate),CG表示FLOTOX管的控制柵(Control Gate),VPP表示外接高壓,此處以12V為例

對EEPROM存儲單元進行“寫入”操作,就是將浮柵中電子釋放的過程(不要把“寫入”與“擦除”操作弄反了),如下圖所示:

如上圖所示,將FLOTOX管的源極懸空,漏極接高壓(不小于12V),而控制柵極接地,則浮柵與漏極之間形成負向強電場,電子從浮柵通過隧道氧化層回到漏極放電。

配合對應的選通管,則一個bit位的存儲單元電路狀態如下圖所示:

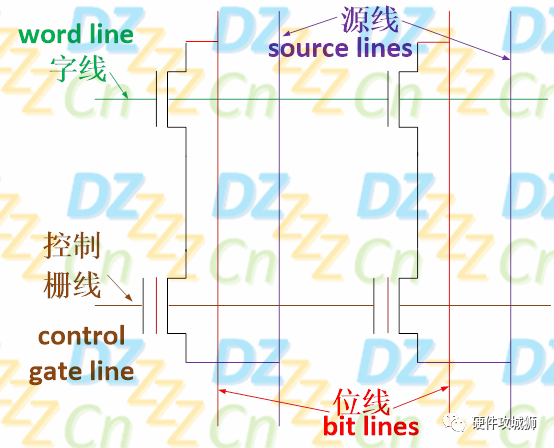

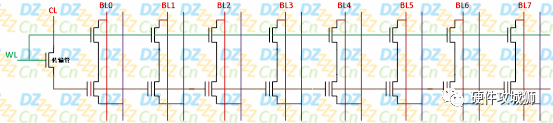

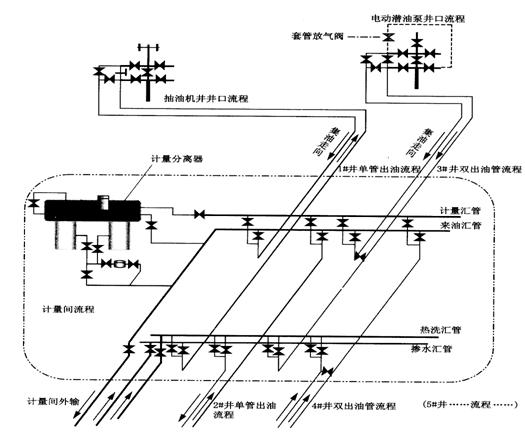

多個bit位組成的存儲單元陣列如下圖所示:

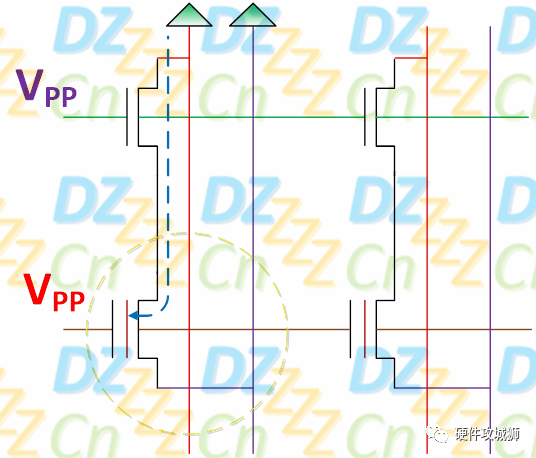

當進行存儲單元的“擦除”操作時,源線(Sources Lines,?SL)與位線(Bit Lines,?BL)均為低電平,而控制柵線(CL)為高電平(不小于12V),當對應存儲單元的選通管打開時(Word Line,?WL=VPP),如下圖所示:

當進行存儲單元的“寫”操作時,位線為高電平(不小于12V),而源線懸空且比Program Gate Line為低電平,當對應存儲單元的選通管打開時(SG=VPP),如下圖所示:

每8個存儲單元配置一個高壓傳輸管,則一個字節的存儲陣列如下圖所示:

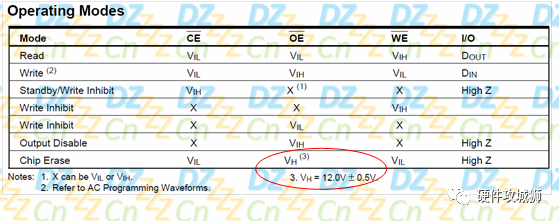

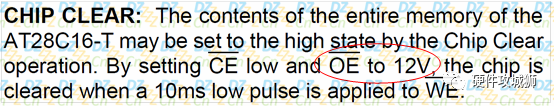

很明顯,EEPROM的“擦除”與“寫入”操作均需要高壓(強電場)進行浮柵電子的注入或釋放,而一般的EEPROM芯片為5V供電,那么這些高壓從何而來?對于并行EEPROM芯片,有專用的引腳可作為擦除功能的高壓供電端,下圖來自ATMEL并行EEPROM型號AT28C16數據手冊:

可以看到,在進行“擦除”操作時,需要在OE(Output Enable)引腳接入12V的高壓。

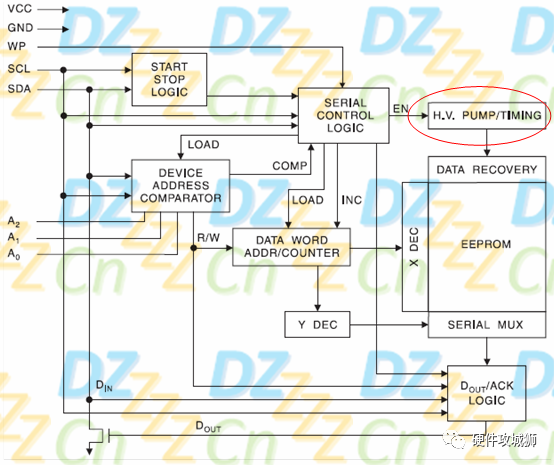

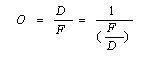

但是串行EEPROM就沒這么幸運了,比如我們最常用的AT24CXX系列EEPROM芯片,通常是3.3V或5V供電的,而且對外的接口通常是I2C串行總線那樣的兩根線,那高壓從何而來?有人想到了升壓電路,沒錯,下圖來自ATMEL串行EEPROM型號AT24C02數據手冊:

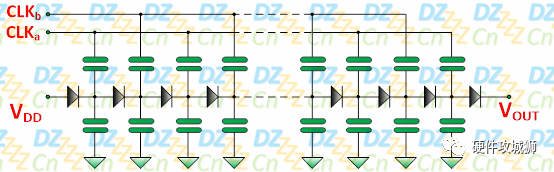

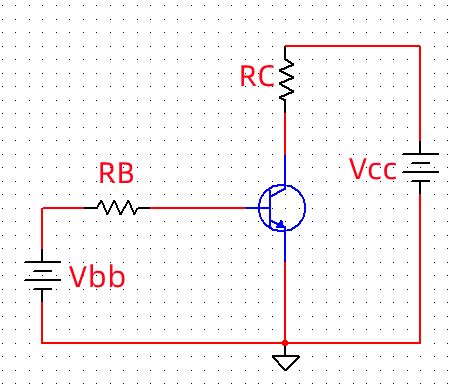

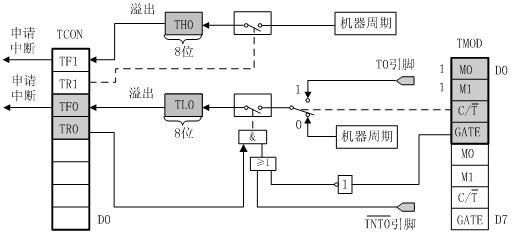

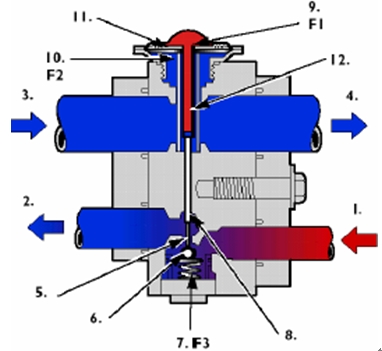

其中,H.V. PUMP(High Voltage Pump)就是高壓泵(升壓)電路,升壓電路有很多種,比如整流倍壓、變壓器升壓、BOOST升壓、電荷泵等,但是,在集成電路設計中無法做成大容量電容與電感,因此,只有電荷泵電路比較適合片內升壓,它的基本電路如下圖所示:

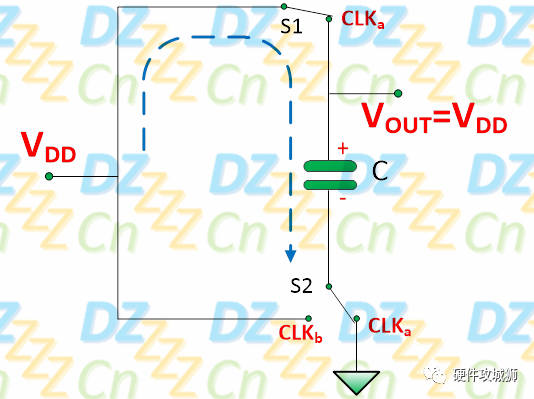

我們分析其中一級就明白其升壓原理了,如下圖所示(原理與“整流倍壓電路”類似,可參考《整流電路》文章):

在時鐘周期CLKa期間,開關S1閉合,S2與地相連接,此時電容充電至VDD。

在時鐘周期CLKb期間,開關S1打開,S2與電源VDD連接,此時電源VDD與電容C的電壓串聯起來對外供電,此時VOUT=為時源VDD的兩倍,即2×VDD。

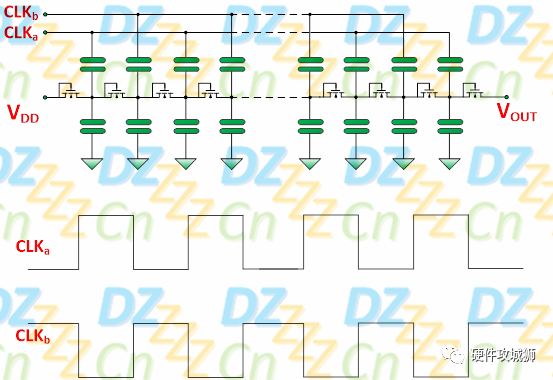

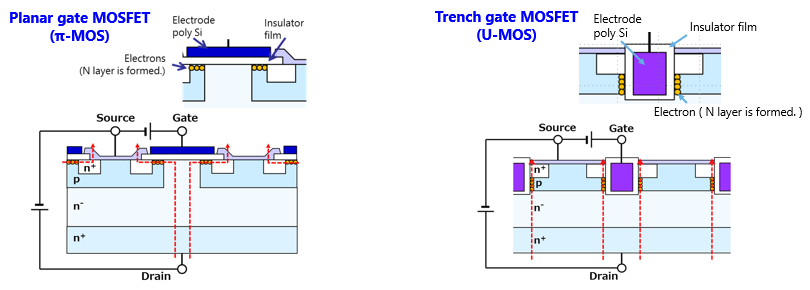

在集成電路設計中,可以使用NMOS或PMOS實現開關功能,電容則可使用MOS電容(即柵極作為一個極,而源極與漏極連接作為另一個極板),而二極管則用MOS管代替,如下圖所示:

實際的電荷泵電路有很多種結構,如多相時鐘電荷泵、CTS電荷泵、柵交叉耦合襯底偏置電荷泵等等,讀者可自行參考相關文檔,此處不再贅述。

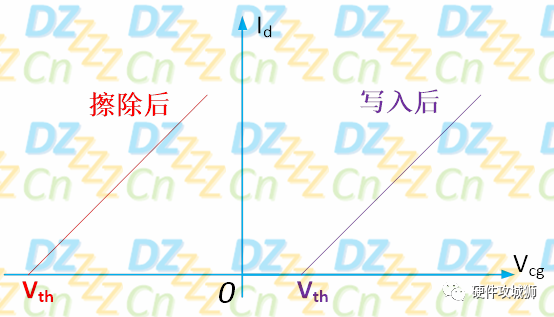

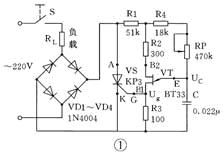

那怎么樣實現數據的“讀取”操作呢?當浮柵中注入(充電狀態)或釋放電子(放電狀態)時,存儲單元的閥值電壓會發生改變,如下圖所示:

在讀取存儲單元時,我們可以在控制柵上加一個中間電平,其值介于兩個閥值Vth之間,這樣浮柵有電子的高開啟管不能導通,而浮柵放電后的低開啟管能正常導通,由此分辨出單元存儲的數據是“1”還是“0”。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論