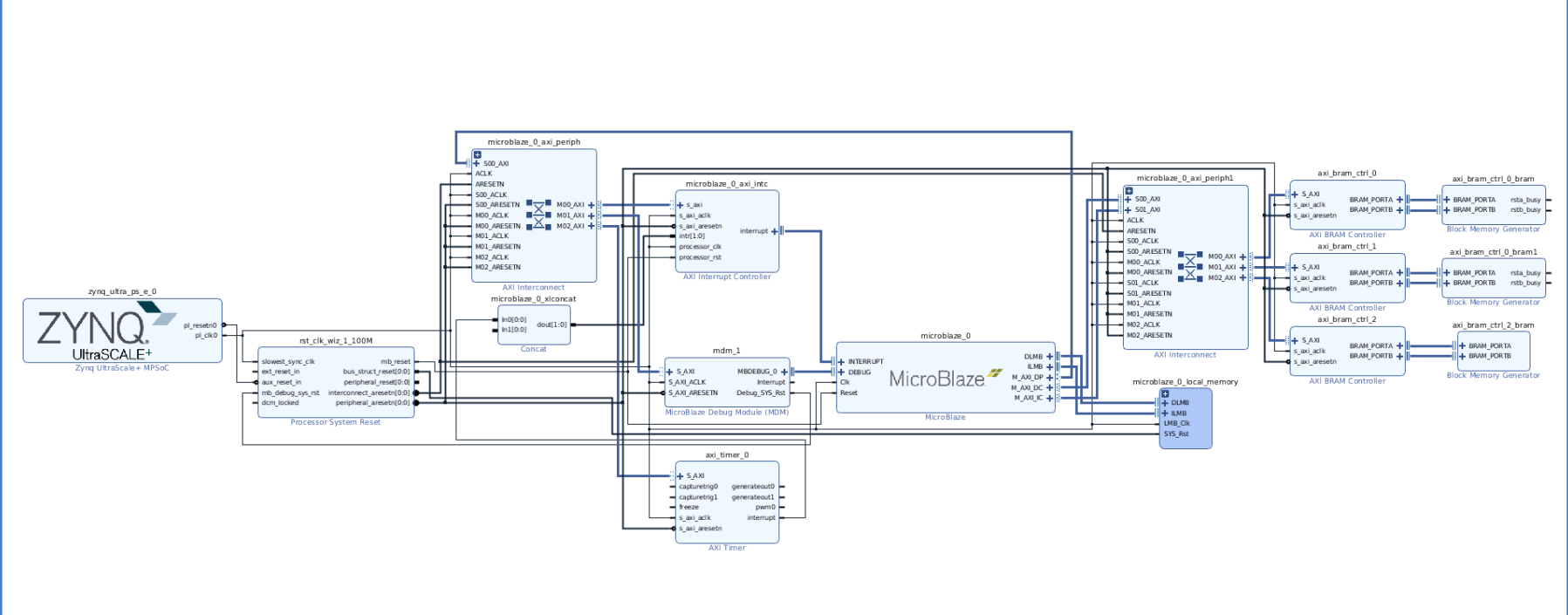

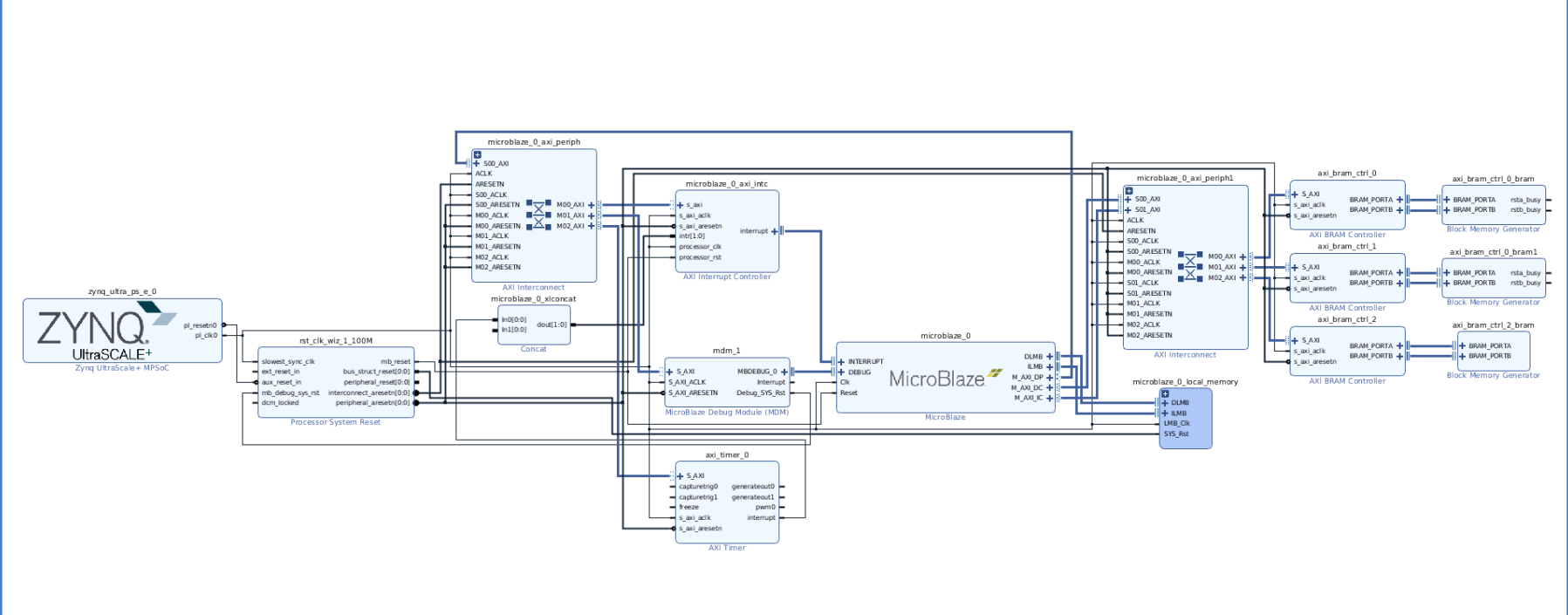

有時CPU需要與PL進行小批量的數據交換,可以通過BRAM模塊,也就是Block RAM實現此要求。本章通過Zynq的GP Master接口讀寫PL端的BRAM,實現與PL的交互。在本實驗中加入了自定義的FPGA程序,并利用AXI4總線進行配置,通知其何時讀寫BRAM。

2021-02-22 13:51:00 7359

7359

FPGA內嵌的存儲器單元包括塊RAM(BRAM)和分布式RAM。

2023-08-15 16:11:05 567

567

BRAM IP核包括哪幾種類型?Vivado中xilinx_BRAM IP核怎么使用?

2021-03-08 07:11:54

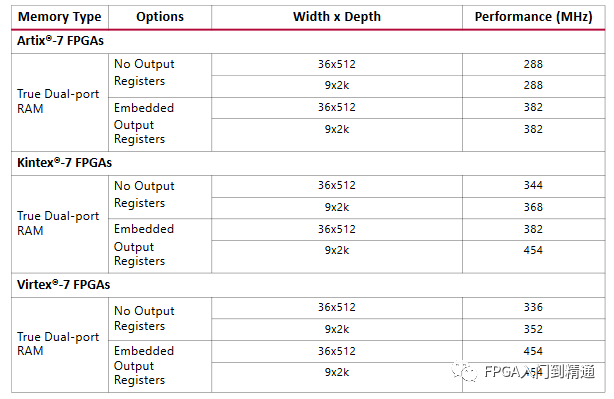

嗨,考慮到所有因素,設備BRAM的最高速度是多少,它是FPGA速度的25/50 / 75%?是的我知道外部延遲和路由將最終控制最大值,但有任何技術考慮因素表明BRAM只能以設備速度的百分比計時。C。

2020-06-02 11:57:26

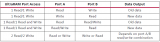

我正在使用具有真正雙端口的BRAM控制器來將FPGA邏輯與微型接口連接起來。我可以在UART上讀取這些內存位置。但是,BRAM的讀訪問似乎存在一些問題。如圖所示,當我寫入多個位置(WEA

2020-04-24 09:05:01

嗨,大家好,最近,在我的設計中,我正在努力解決BRAM阻塞RAMB16BWE引起的問題。給出的警告示例如下:PhysDesignRules:812- 塊上的懸空引腳:: 16BWE>。組件

2019-05-27 08:35:05

親愛的FPGA專家,美好的一天!有人可以告訴我BRAM,DRAM和DMA之間的區別嗎?在什么特定情況下,每個適合使用?我們正在使用xilinx zedboard設備。非常感謝你。最好的祝福,格倫以上

2019-04-29 10:24:38

FPGA入門知識介紹近幾年來,由于現場可編程門陣列(FPGA)的使用非常靈活,又可以無限次的編程,已受到越來越多的電子編程者的喜愛,很多朋友都想學習一些FPGA入門知識準備進行這個行業,現在關于

2014-08-16 10:32:45

重要組成部分,所以我們將重點介紹Vitis HLS。LUT 或 SICELUT 或 SICE是構成了 FPGA 的區域。它的數量有限,當它用完時,意味著您的設計太大了!BRAM 或 Block

2022-09-07 15:21:54

可控進程難以阻擋,國產當自強。產業鏈角度來看,硬件產業鏈中目前自主可控程度較低,尤其在高端半導體設備和材料領域,未來產業鏈上下游國產替代進程的推進也將助力國產 FPGA 加速發展。

硬件部分上游

2024-03-08 14:57:22

本文轉載自IT之家,IT之家 3 月 17 日消息 中國科學技術協會官方微信公眾號 “科普中國”昨天發文為大家科普了正確的手機充電 “姿勢”,并建議給手機充電時先用充電器插電源,然后插手機。文章首先科普

2021-09-14 07:23:54

在NGDBUILD期間發現了錯誤ERROR :: 90 - 在網表中找不到BRAM實例'A_digital_top / A_core_12 / A_cpu_top / A_rom_wrapper / A_ram1kx32m32_wrapper_0 / A_RAMB36E1_IROM0'。讓我知道如何解決這個問題。謝謝,肖恩

2020-04-23 08:53:52

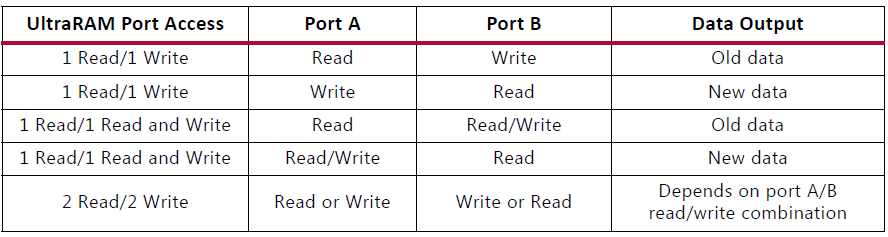

URAM和BRAM有什么區別

2021-02-23 07:52:47

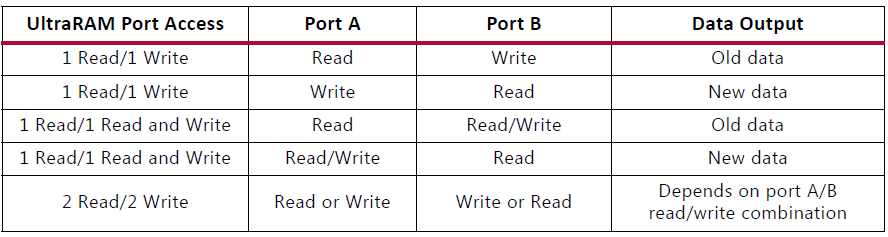

無論是7系列FPGA、UltraScale還是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就

2020-12-23 16:57:28

嗨,我對FPGA設計很陌生,更多的是學習如何使用所有工具。無論如何,我的論文的大部分時間都在我的論文中運作良好,這就是BRAM的最后一個難題。我使用ISE模板創建了1kx16(雙端口)BRAM,并將

2019-11-01 10:12:40

VR防艾教育模擬系統里,體驗者站在半開放式的模擬血管內,學習與艾滋病相關的常見科普知識問答。 科普體驗完以后,我們設置了一個“VR抗艾小游戲”互動環節,寓教于樂,讓學習印象更深刻。? 適用群體

2018-10-15 15:04:54

在虛擬的普法教室內,有警官、老師、學生等元素,將現實中的教學場景通過三維建模技術,逼真還原,讓體驗者彷如置身于現場。為了讓參與者能更好地體驗我司的科普內容,我們還貼心地設置了“站著體驗”和“坐著

2018-10-13 15:22:21

模擬系統里,體驗者站在半開放式的模擬血管內,學習與艾滋病相關的常見科普知識問答。科普體驗完以后,我們設置了一個“VR抗艾小游戲”互動環節,寓教于樂,讓學習印象更深刻。適用群體:***相關衛生職能機構

2018-10-25 17:06:46

嗨,我對Virtex-4中BRAM的工作頻率有疑問。如果有人知道BRAM的最大工作頻率是多少?提前致謝以上來自于谷歌翻譯以下為原文hi, I have a question about

2018-10-10 11:53:12

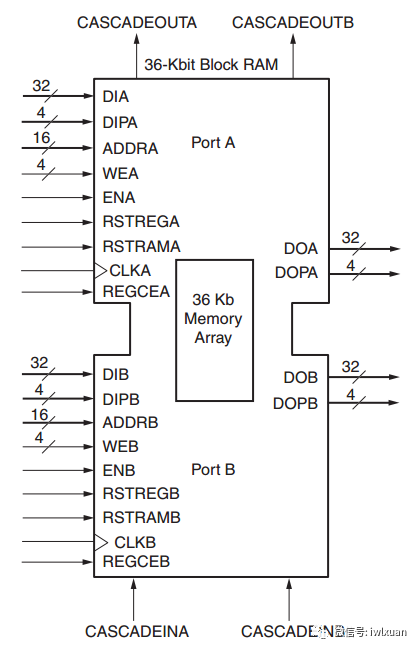

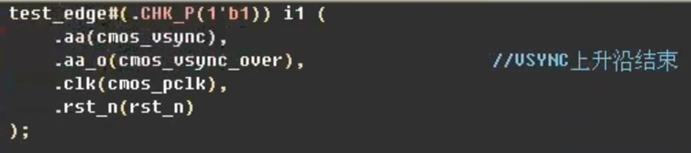

原子公眾號,獲取最新資料第十四章基于BRAM的PS和PL的數據交互在ZYNQ SOC開發過程中,PL和PS之間經常需要做數據交互。對于傳輸速度要求較高、數據量大、地址連續的場合,可以通過AXI DMA來

2020-09-04 11:08:46

我有一個針對spartan-6(LX45)的項目,該項目在ISE 12.2中沒有出現任何問題。最近升級到ISE 14.7項目不再正確構建。問題是BRAM沒有正確初始化。此項目中BRAM使用的方法

2019-07-12 15:10:57

我在我的設計中使用Bram,而源和目標的clk是相同的。但我在數據路徑中得到保持違規-0.068,我嘗試過雙同步,但它對時間沒有任何影響。鋤頭來解決這個問題我附上了bram的道路。謝謝

2020-05-25 13:59:33

FPGA的硬核和軟核有什么區別呢,有沒有使用硬核的開發板,想學習關于FPGA硬核的知識,各位大神有什么建議呢?真心求教

2013-03-05 11:51:54

大家好,我搜索了幾個關于初始化BRAM的線程,但我找不到答案。我使用的是Vivado 2015.4。我寫了一個coe文件,想把coe文件加載到BRAM中。首先,我添加一個BRAM IP,然后加載

2019-04-17 09:47:17

如題哪位大神能給科普一下產品加密保護方面的知識?

2016-12-08 10:46:50

我目前正在使用Spartan 6板。我初衷了BRAM。我現在想通過UART將數據從BRAM發送到計算機。我還設法讓UART與PC連接運行(我使用了兩者的預先存在的代碼)。如何將數據從BRAM發送到

2020-05-04 17:27:37

Spartan 6 BRAM顯然有一個涉及雙端口模式和異步時鐘的錯誤。這個部分記錄在BRAM用戶指南中。我通常使用以下模板暗示在Verilog中阻止rams: reg [7:0] mem [255

2019-05-27 12:16:37

嗨,我正在開發一個項目,我們正在使用Virtex-5 FPGA從ADC捕獲信號,樣本存儲在128K x 256 SRAM上,數據樣本由PC采集。我相信Virtex-5為BRAM提供了一個選項,雖然我

2020-06-17 11:31:47

在vivado中bram加載coe文件數據僅在instatntiation中生成datain,但沒有datain

2020-04-15 10:12:41

你好,我在FPGA(ISE14)中有一個部分重配置設計,它包含一個由coregen生成的BRAM存儲器塊。在整個設計布線后,我需要能夠改變這些存儲器的內容。我知道data2mem程序可以完成類似

2018-10-16 06:40:10

嗨朋友們,我正在嘗試使用塊內存生成器訪問存儲在ROM中的.coe文件。我想為此編寫一個verilog代碼。如何以verilog代碼訪問存儲在BRAM中的像素值?提前致謝。以上來自于谷歌翻譯以下為原文

2019-02-26 09:48:33

嗨,我能夠在我們的定制板上連接到virtex 7 fpga。我的塊級設計具有用于pcie的軸橋作為終點和axi bram。但我無法使用pcie鏈接從外部處理器訪問bram。任何人都可以幫忙解決這個問題嗎?大多數情況下,我猜這與地址翻譯有關,我無法弄清楚。謝謝

2020-04-22 09:31:47

,DDR在設計中,但它沒有被積極使用。它有趣的工作。可能是什么問題呢?有用的建議將是一件非常愉快的事情。謝謝。以上來自于谷歌翻譯以下為原文Hello How can I design FPGA BRAM

2019-04-04 15:10:55

我的Vertex 4設計在將其寫入外部DRAM之前使用BRAM作為累積數據的緩沖區。 BRAM在RTL代碼中手動實例化。用戶指南似乎表明只能在配置fpga設備期間初始化BRAM內容。在某些情況下,我的控制器希望在正常操作期間將BRAM內容返回到其初始值,而無需重置整個設計。這可能嗎?我該怎么做?

2020-05-28 08:53:15

嗨,我為CMOD A7設置了一個微型燈,uart,sram和bram的方框圖。我無法寫信給BRAM。我寫入地址并嘗試從地址讀取,值始終為零。有沒有人遇到過CMOD A7的這個問題?我為ARTY板使用了相同的協議,它運行良好。謝謝,維多利亞

2020-08-13 09:19:38

我正在使用ISE 14.7。我有一個測試項目。在XPS中,它有一個bram_block,其中兩個端口用于dlmb_port,ilmb_port用于micrlaze處理器。最初,使用XPS中的“系統

2018-10-25 15:24:01

小編科普D類音頻功率放大器的熱耗散知識

2021-06-03 06:57:17

我有一個帶有64kb BRAM的Microblaze,帶有指令和數據空間(一個端口上的標準I和另一個端口上的D)。我有另一個64kb只在一個端口上連接到Microblaze并且只包含數據。第二個端口

2019-03-04 12:09:00

大家好請任何人告訴我。是否有任何方法可以從Virtex 6的FPGA中取出BRAM轉儲。提前致謝問候Vir_1602以上來自于谷歌翻譯以下為原文Hi all would anyone please

2019-03-20 15:37:12

可以從Zynq上運行的Linux控制的額外IP。我要做的就是將一些配置數據寫入PL中的BRAM。要做到這一點,根據我在其他地方得到的建議,我提出了一個axi_cdma。所以CDMA有一個

2019-04-19 07:50:52

我有一個程序文件,在模擬開始時必須存儲在BRAM中。要加載BRAM,我無法重復使用我的傳統測試平臺任務,因為內存組織不同,因為這些任務是為ASIC RAM IP編寫的。我們正在嘗試使用Xilinx

2019-04-22 07:41:01

嗨,我想將數據存儲到由axi_bram_controller控制的bram中。那么如何確認我傳輸的十進制數據而不是十六進制數據呢?問候,索菲亞

2020-05-11 09:21:52

嗨,我想在我的VHDL代碼中使用fsm_style屬性來在SpartanXC3S200AN設備中的BRAM中實現我的狀態機。我在綜合后得到的代碼和警告如下:HDL代碼arcihtecture bla

2019-04-01 12:36:46

嗨,我正在嘗試使用自定義IP寫入vhdl中的雙端口BRAM,該IP生成地址并啟用所有信號,但我無法正確寫入雙端口BRAM。 BRAM的另一個端口就是從PS Zynq讀取值并且不寫入。這是我寫入

2019-04-17 08:15:09

,設計無法滿足時序要求。 550MHz是Virtex 5數據表中規定的最大允許頻率。當我使用BRAM或FIFO_BRAM實現FIFO時,設計失敗。我使用了一個選項,因此未連接的元素不會被修剪(地圖階段的-u

2020-06-13 15:49:32

大家好,我們正在回讀我們架構的一些BRAM(配置為雙端口RAM)。為避免數據損壞,我們禁用時鐘并在回讀之前將啟用引腳設置為“0”(在兩個端口中)。我們只是在我們要回讀的BRAM中這樣做。但是,我們在

2020-06-11 15:29:20

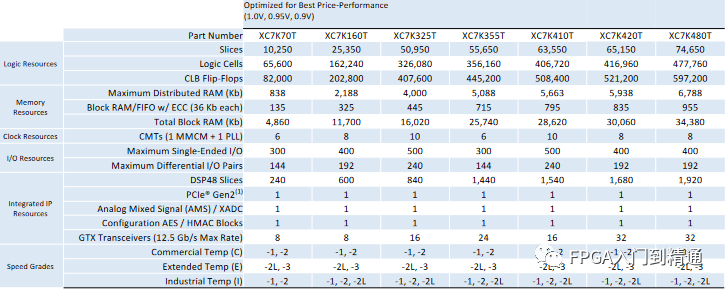

,這是新型xilinx產品的基礎架構,因此DSP-Slices和CLB的寬度可能相等,但我找不到確認的信息。如果有人能夠提供有關7系列FPGA中CLB,DSP48E1和BRAM36K / BRAM18K之間水平關系的信息,將會非常有幫助。

2020-07-25 11:04:42

。其中存儲器是功耗大戶,如xilinx FPGA中的存儲器單元Block RAM,因此在這邊主要介紹對BRAM的一些功耗優化方法。如圖5中實例,雖然BRAM只使用了7%,但是其功耗0.601W占了總

2014-08-21 15:31:23

嗨,我的設計在合成中使用141.5 BRAM瓦片。但是,在Zynq中可以使用140 BRAM瓦片。實施后,這個數量下降到133瓦。我的問題是vivado如何減少這一數量?實施?這點可以導致未來

2018-10-31 16:17:40

嗨,大家好,我想用coe文件初始化BRAM,但有兩個問題。首先,當我加載coe文件時,存在文件不存在的錯誤。見下圖:有人可以幫我解決問題嗎?其次,我刪除了錯誤文件,因為“文件組”下有兩個coe文件

2019-04-18 11:27:07

嗨,大家好,我正在研究Vivado 2014.4,Xilinx KC705。我需要通過Microblaze讀取存儲在BRAM(coe文件)中的數據進行計算。我是微博閱讀部分的新手。有人可以建議我

2020-05-20 08:38:21

我想在Virtex-5 LX50T中實現尺寸為338 KB的BRAM。我覺得V5 FPGA內沒有足夠的BRAM容量。除了36K和18K塊之外,是否有可能使用更小容量的BRAM。是否有任何設置/選項可供設置。請幫助我這方面。JVK yadav

2020-05-27 08:05:46

數字化氣象綜合服務平臺。通過氣象科普實物,傳播氣象科學知識,增強青少年學生的公眾氣象意識,培養和提高他們防災抗災的技能與能力。特別是在于開拓、延伸、補充同學們的課外

2021-03-26 17:17:04

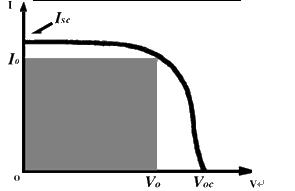

科普知識: 太陽能光伏知識1、 1、 太陽能電池發電原理: 太陽電池是一種對光有響應并能將光能轉換成電力的器

2009-02-23 21:35:15 3882

3882

The PLB BRAM Interface Controller is a module thatattaches to the PLB (Processor Local Bus

2012-02-10 16:59:50 31

31 本文檔詳細介紹的是FPGA教程之CPLD與FPGA的基礎知識說明主要內容包括了:一、復雜可編程邏輯器件簡介二、CPLD的組成與特點三、FPGA的組成與特點四、CPLD與FPGA的異同五、主要的PLD廠商

2019-02-27 17:09:32 32

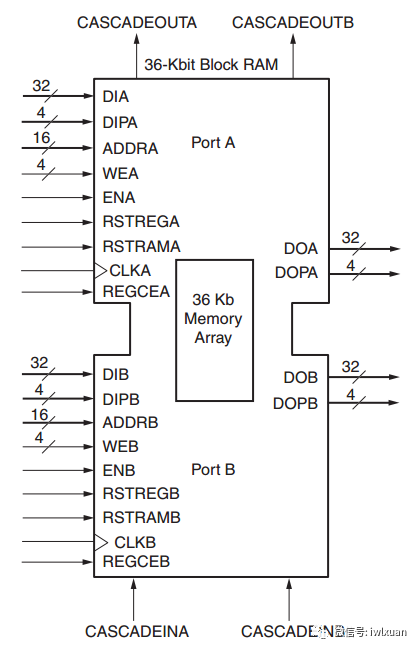

32 BRAM和URAM都可級聯,只是級聯方式不同。在使用BRAM時,我們只需要設定寬度和深度,并根據時鐘頻率合理選擇Latency,也就是選擇是否需要使用BRAM自帶的輸出寄存器或Slice中的寄存器

2019-03-06 15:44:41 27036

27036

本文檔的主要人詳細介紹的是FPGA基礎知識培訓教程免費下載包括了:1.什么是FPGA ,2.Actel FPGA整體概述 3.Actel FPGA的性能,4.Actel FPGA的優勢

2019-04-23 08:00:00 7

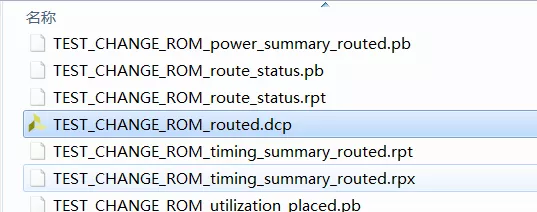

7 1、引言 以交換機設計為例。在交換機設計前期,轉發表項是固化在交換機內部的(給FPGA片內BRAM初始值),但是在測試過程中,往往需要對表項進行修改,如果直接修改BRAM的coe文件,則需要重新綜合

2020-11-30 15:37:43 2196

2196

? Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM ?IP

2020-12-29 15:59:39 9496

9496 FPGA可以調用分布式RAM和塊RAM兩種RAM,當我們編寫verilog代碼的時候如果合理的編寫就可以使我們想要的RAM被綜合成BRAM(Block RAM)或者DRAM(Distributed

2020-12-30 16:27:52 9

9 無論是7系列FPGA、UltraScale還是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就是我們所說的URAM。BRAM和URAM都是重要的片上存儲資源,但兩者還是有些顯著的區別。

2022-07-25 17:54:14 4534

4534

無論是7系列FPGA、UltraScale還是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就是我們所說的URAM。BRAM和URAM都是重要的片上存儲資源,但兩者還是有些顯著的區別。

2021-01-27 06:55:09 12

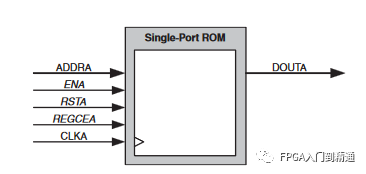

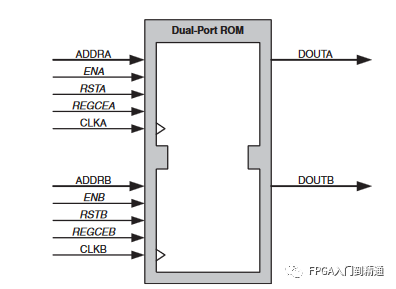

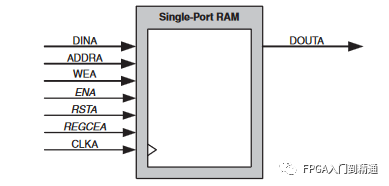

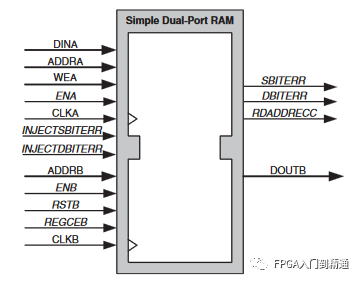

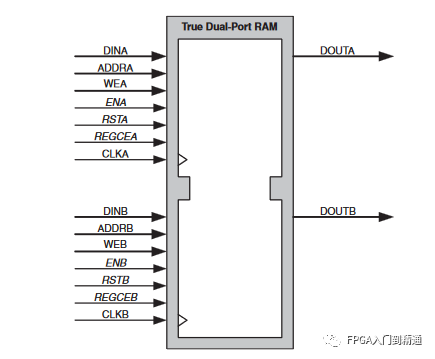

12 Vivado2017.2 中BRAM版本為 Block Memory Generator Specific Features 8.3。BRAM IP核包括有5種類型:Single-port RAM 單端口RAM,Simple Dual-port RAM 簡單雙端口RAM(A寫數據B讀數據)

2021-03-10 06:15:56 19

19 CPLD/FPGA的基本知識講解。

2021-03-30 09:55:18 27

27 電子發燒友網為你提供5G知識科普:什么是SSB?資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-29 08:50:24 636

636 FPGA 是可以先購買再設計的“萬能”芯片。FPGA (Field Programmable Gate Array)現場可編程門陣列,是在硅片上預先設計實現的具有可編程特性的集成電路,它能夠按照

2021-04-30 11:13:54 6339

6339

學習FPGA,筆者推崇的學習方法是先整體再局部。先對FPGA 有一個整體的認識,包括知道有哪些知識點,這些知識點所處的位置和作用。然后在此基礎上再逐個突破。

2022-03-22 14:47:21 597

597

今天安泰小編為大家科普渦流的有關知識,如果感興趣的話,就繼續往下看吧!

2022-05-19 15:22:36 5955

5955

MicroBlaze可以使用AXI BRAM存放數據和指令。有些客戶軟件很大,需要把AXI BRAM的空間做到最大。AXI BRAM底層是Block RAM或者Ultra RAM。器件的Block RAM或者Ultra RAM個數,決定了AXI BRAM的大小。

2022-08-02 10:09:05 2423

2423

內容來源:美麗株所 END 原文標題:知識科普 | 沙子變“芯”計 文章出處:【微信公眾號:機智云物聯網】歡迎添加關注!文章轉載請注明出處。

2022-11-10 11:20:03 310

310 FPGA端實現SDIO Slave功能 a.FPGA將SDIO Master發送的2KByte數據保存至BRAM。 b.SDIO Master發起讀數據時,FPGA從BRAM讀取2KByte通過SDIO總線傳輸給SDIO Master。

2022-11-10 12:22:18 1912

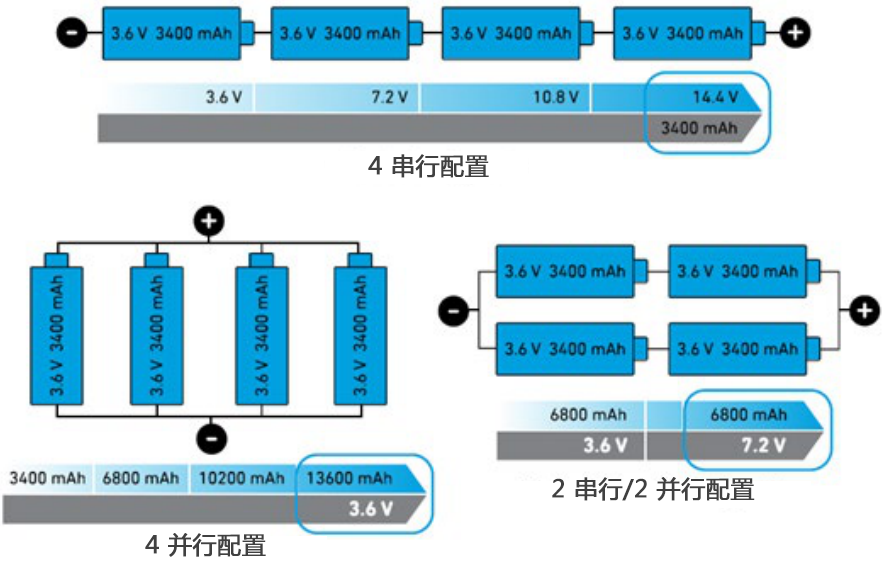

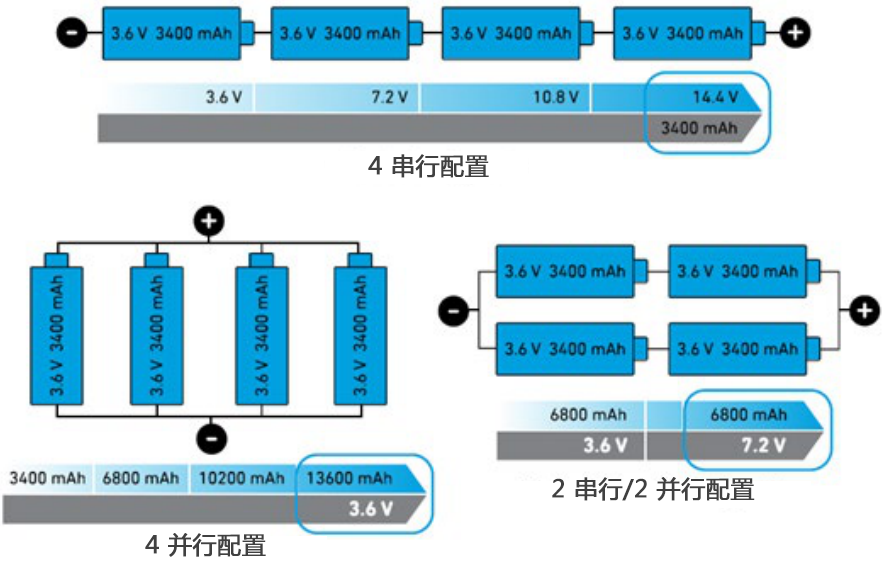

1912 成長計劃 電池知識科普與DIY指南 工程師成長計劃第十七期,深入電池原理、電路設計及DIY指南。 電池涉及到材料及電化學,往往在工程設計的時候,十分考驗工程師的學科交叉知識儲備。 電池

2022-11-17 08:25:11 1022

1022 以交換機設計為例。在交換機設計前期,轉發表項是固化在交換機內部的(給FPGA片內BRAM初始值),但是在測試過程中,往往需要對表項進行修改,如果直接修改BRAM的coe文件,則需要重新綜合、實現、生成bit文件

2023-02-02 14:03:22 676

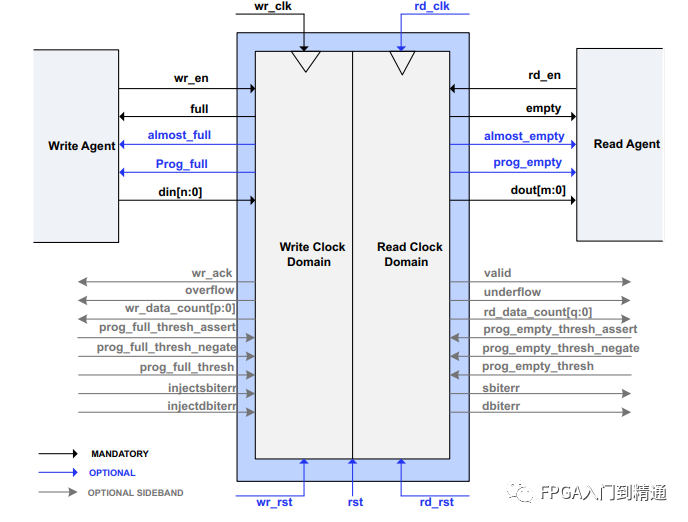

676 FPGA開發中使用頻率非常高的兩個IP就是FIFO和BRAM,上一篇文章中已經詳細介紹了Vivado FIFO IP,今天我們來聊一聊BRAM IP。

2023-08-29 16:41:49 2605

2605

FPGA的BRAM和LUT等資源都是有限的,在FPGA開發過程中,可能經常遇到BRAM或者LUT資源不夠用的情況。

2023-08-30 16:12:04 949

949

電氣基本知識科普

2023-09-09 10:23:27 3814

3814

PCB高速信號在當今的一個pcb設計中顯然已成為主流,一名優秀的PCB工程師,除了在實戰項目慢慢積累設計PCB高速信號的經驗外,還需通過不斷學習來提升自己的知識儲存和專業技能。本文捷多邦小編就給大家科普一下PCB高速信號的一些相關布線知識。

2023-09-15 10:19:18 722

722 電子發燒友網站提供《基于FPGA的加速基礎知識.pdf》資料免費下載

2023-09-18 10:12:20 0

0 科普|電源管理知識

2023-10-17 16:31:55 305

305

Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 317

317 電子發燒友網站提供《FPGA基礎知識介紹.pdf》資料免費下載

2024-02-23 09:45:52 1

1

電子發燒友App

電子發燒友App

評論