處理器,無(wú)論是CPU、GPU、FPGA,還是NPU,要想正常運(yùn)行,都離不開(kāi)RAM,特別是DRAM(動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器),它已經(jīng)成為各種系統(tǒng)(PC,手機(jī),數(shù)據(jù)中心等)中內(nèi)存的代名詞。根據(jù)應(yīng)用不同,系統(tǒng)對(duì)芯片面積和功耗有不同要求,因此,DRAM被分成標(biāo)準(zhǔn)DDR(雙倍數(shù)據(jù)速率)、LPDDR、GDDR等,當(dāng)然,主要就是這三類(lèi)。其中,DDR是相對(duì)于SDR(單數(shù)據(jù)速率)而言的,將I/O時(shí)鐘加倍了,主要為PC和數(shù)據(jù)中心的CPU服務(wù),目前已經(jīng)發(fā)展到DDR5;LPDDR是低功耗的DDR,主要用于手機(jī)等便攜式設(shè)備;GDDR則是GPU專(zhuān)用DRAM。

在高性能計(jì)算(HPC)和AI發(fā)展如火如荼的當(dāng)下,一個(gè)很大的瓶頸就是處理器與DRAM之間的通信速度,越來(lái)越跟不上應(yīng)用需求的前進(jìn)腳步。對(duì)此,人們想出了多種方法,以提升通信帶寬,如不斷提升DRAM本身的接口性能,以及存算一體等,但從實(shí)際應(yīng)用情況來(lái)看,只提升接口性能是不夠用的,而存算一體短期內(nèi)還無(wú)法實(shí)現(xiàn)。在這種情況下,推出更好的DRAM與CPU、GPU等處理器的結(jié)合形式,也就是不斷讓封裝技術(shù)進(jìn)步,成為了業(yè)界提升通信帶寬的普遍共識(shí)。

01DRAM的常用封裝技術(shù)

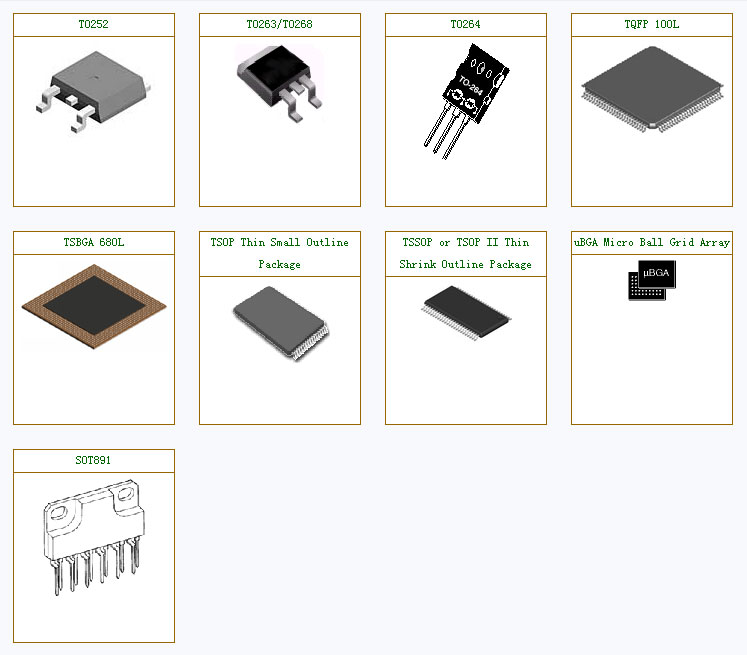

DRAM封裝技術(shù)幾經(jīng)變遷,從雙列直插封裝DIP、J型引腳小外形封裝SOJ、薄型小尺寸封裝TSOP、底部引線塑料封裝BLP、焊球陣列封裝BGA(F-BGA、W-BGA),發(fā)展到芯片級(jí)封裝CSP、堆疊封裝等高性能封裝方式。在成本允許的條件下,可盡量采用先進(jìn)的封裝技術(shù),以提升DRAM性能。目前,堆疊封裝技術(shù),特別是系統(tǒng)級(jí)封裝(SiP),可以在有限的空間內(nèi)成倍提高存儲(chǔ)器容量,或?qū)崿F(xiàn)電子設(shè)計(jì)功能,解決空間、互連受限等問(wèn)題。此外,由于封裝設(shè)計(jì)的變化,引線鍵合封裝因具有靈活性、可靠性和低成本的優(yōu)點(diǎn)而備受青睞。倒裝(Flip Chip,F(xiàn)C)芯片于2016年開(kāi)始進(jìn)軍DRAM封裝,由于高帶寬需求的推動(dòng),倒裝芯片在PC、服務(wù)器中的采用率不斷增加。

目前,系統(tǒng)對(duì)高帶寬、高性能、低延遲的綜合要求很高,硅通孔(TSV)很適合高帶寬內(nèi)存封裝需求。在便攜式電子設(shè)備應(yīng)用中(如手機(jī)),DRAM的封裝尺寸會(huì)直接影響到產(chǎn)品的體積大小,所以,封裝技術(shù)要向輕、薄、短、小方向發(fā)展。不同應(yīng)用的產(chǎn)品尺寸、性能、形態(tài)等存在差異,采用的封裝形式也不同。其中,移動(dòng)終端DRAM(LPDDR)多以WB-FBGA為主,PC和服務(wù)器用的標(biāo)準(zhǔn)型DDR則以FBGA、FC為主。以DDR為例,F(xiàn)BGA線長(zhǎng)較短,信號(hào)傳輸好且成本較低,曾經(jīng)被三星、SK海力士和美光等主流廠商廣泛采用,隨著內(nèi)存條產(chǎn)品發(fā)展到DDR4,三星、SK海力士的很多產(chǎn)品開(kāi)始轉(zhuǎn)向FC封裝,其傳輸路徑更短,電性能表現(xiàn)更好。

盡管FC的成本比FBGA高,但得益于規(guī)模效應(yīng),兩者成本基本持平。現(xiàn)在的高端產(chǎn)品,如DDR5,性能要求很高,目前多采用TSV堆疊封裝。TSV采用縱向穿越結(jié)構(gòu),通過(guò)導(dǎo)線將不同層的芯片相互連接起來(lái),這種連接方式不僅提供了更高的信號(hào)帶寬,還減少了電阻和電感,提高了芯片的整體性能。通過(guò)TSV把多芯片的I/O連接,同時(shí)實(shí)現(xiàn)多芯片堆疊來(lái)擴(kuò)容并實(shí)現(xiàn)更小的信號(hào)損失。LPDDR與處理器緊密集成在一起,或者焊接在主板上,靠近CPU,或者直接在處理器(在這種情況下,通常是SoC)的頂部以 package-on-package封裝的形式出現(xiàn),這種形式越來(lái)越常見(jiàn)。緊密的集成可減少將內(nèi)存連接到處理器的長(zhǎng)導(dǎo)線中的電阻,從而降低功耗。總體來(lái)看,引線鍵合是主要的封裝方法,廣泛應(yīng)用于移動(dòng)存儲(chǔ)器,其次是倒裝芯片封裝,其在DRAM市場(chǎng)不斷拓展。

02HBM帶動(dòng)封裝技術(shù)再創(chuàng)新

目前,AI服務(wù)器對(duì)HBM(高帶寬內(nèi)存)的需求量越來(lái)越大,因?yàn)镠BM大大縮短了走線距離,從而大幅提升了AI處理器運(yùn)算速度。HBM經(jīng)歷了幾代產(chǎn)品,包括HBM、HBM2、HBM2e和HMB3,最新的HBM3e剛出樣品。HBM是一種應(yīng)用于CPU和GPU的新型內(nèi)存,它將多個(gè)DDR芯片堆疊在一起后和GPU封裝在一起,主要通過(guò)TSV技術(shù)進(jìn)行芯片堆疊,通過(guò)貫通所有芯片層的柱狀通道傳輸信號(hào)、指令和電流,以增加吞吐量并克服單一封裝內(nèi)帶寬的限制,實(shí)現(xiàn)了大容量、高帶寬的DDR組合陣列。HBM3帶寬可以達(dá)到819GB/s。

目前,全球三大存儲(chǔ)芯片廠商都在開(kāi)發(fā)HBM技術(shù)和產(chǎn)品,其中,三星和SK海力士已經(jīng)量產(chǎn)了HBM3,主要用于英偉達(dá)的H100、H800和AMD的MI300系列GPU,三星預(yù)計(jì)于2024年第一季度送樣HBM3e,下半年量產(chǎn),SK海力士則于近期給英偉達(dá)送去了HBM3e樣品,其最新的GPU芯片H200已經(jīng)標(biāo)配了HBM3e。美光(Micron)則相對(duì)落后,該公司選擇跳過(guò)HBM3,直接開(kāi)發(fā)HBM3e。傳統(tǒng)封裝技術(shù)已經(jīng)難以滿(mǎn)足HBM的需求,而臺(tái)積電的CoWoS(chip-on-wafer-on-substrate)封裝則是較為理想的方案。

CoWoS是一種集成邏輯和HBM芯片的2.5D封裝技術(shù),在這種封裝中,處理器和HBM在硅中介層上并排鍵合,以形成具有細(xì)間距和器件之間高密度互連布線的晶圓上芯片(CoW)。每個(gè)HBM都由帶有微凸塊的DRAM和一個(gè)帶有TSV的邏輯基座組成,然后完成在基板上具有較大凸塊的TSV中介層的組裝。

多年來(lái),CoWoS一直在追求不斷增加硅中介層尺寸,以支持封裝中的處理器和HBM堆棧。目前,CoW是倒裝芯片鍵合最常用的組裝方法,它采用了一種稱(chēng)為混合鍵合方法的無(wú)凹凸技術(shù)。CoWoS產(chǎn)能不足是近期AI芯片出貨量的主要瓶頸,以臺(tái)積電為代表的廠商正在擴(kuò)充相關(guān)產(chǎn)能,以滿(mǎn)足市場(chǎng)需求。

03先進(jìn)封裝大戰(zhàn)

臺(tái)積電在2011年就開(kāi)始布局CoWoS了,并陸續(xù)獲得多個(gè)客戶(hù)訂單,但由于報(bào)價(jià)昂貴,加上相應(yīng)的需求有限,因此,前些年的產(chǎn)能沒(méi)有明顯增加,但是,進(jìn)入2023年以來(lái),特別是AIGC需求爆發(fā),臺(tái)積電開(kāi)始大幅擴(kuò)建CoWoS產(chǎn)線。目前,除了臺(tái)積電,英特爾、三星等芯片制造大廠也在加大先進(jìn)封裝投入力度。英特爾方面,預(yù)計(jì)該公司最新先進(jìn)封裝服務(wù)將在2026年投入量產(chǎn)。不同于其它競(jìng)爭(zhēng)對(duì)手主要采用硅制程的中間層技術(shù),英特爾選擇用玻璃基板,其成本會(huì)相對(duì)較高,業(yè)界采用該方案的廠商較少。對(duì)于趕超臺(tái)積電HBM先進(jìn)封裝技術(shù)最為積極的是三星。2021年,三星推出了2.5D封裝技術(shù)H-Cube。今年9月,據(jù)Etnews報(bào)道,為了追上臺(tái)積電AI芯片的先進(jìn)封裝,三星將推出名為FO-PLP的2.5D封裝技術(shù)。

據(jù)悉,F(xiàn)O-PLP可將處理器和HBM整合到硅中介層。據(jù)悉,F(xiàn)O-PLP的基板是方形,而臺(tái)積電的CoWoS是圓形基板,F(xiàn)O-PLP不會(huì)有邊緣基板損耗問(wèn)題,但由于要將芯片由晶圓移植到方形基板,其作業(yè)較為復(fù)雜。近期,三星還推出了最新的封裝技術(shù)SAINT,包括SAINT S(垂直堆疊內(nèi)存和CPU),SAINT D(用于CPU、GPU和內(nèi)存的垂直封裝),SAINT L(用于堆疊應(yīng)用處理器)。

消息人士稱(chēng),SAINT S已經(jīng)通過(guò)了驗(yàn)證測(cè)試,在與客戶(hù)進(jìn)行進(jìn)一步測(cè)試后,三星將于2024年推出相應(yīng)的商業(yè)服務(wù)。最近,三星HBM3及其封裝服務(wù)通過(guò)了AMD的質(zhì)量測(cè)試,后者計(jì)劃將這些芯片和服務(wù)用于其最新的GPU芯片Instinct MI300X。此前,AMD曾考慮使用臺(tái)積電的封裝服務(wù),但由于后者的CoWoS產(chǎn)能?chē)?yán)重供不應(yīng)求,AMD不得不改變計(jì)劃。據(jù)韓國(guó)消息人士透露,三星還在與英偉達(dá)進(jìn)行HBM3芯片技術(shù)驗(yàn)證,并提供封裝服務(wù)。一旦工作完成,預(yù)計(jì)三星將負(fù)責(zé)英偉達(dá)H100 與HBM3的封裝,據(jù)悉,這兩家公司簽署了一項(xiàng)服務(wù)和供應(yīng)協(xié)議。今年6月,三星成立了多芯片集成聯(lián)盟,目的是與存儲(chǔ)芯片公司、外包半導(dǎo)體封裝和測(cè)試公司(OSAT),以及芯片設(shè)計(jì)公司共同推進(jìn)封裝技術(shù)。

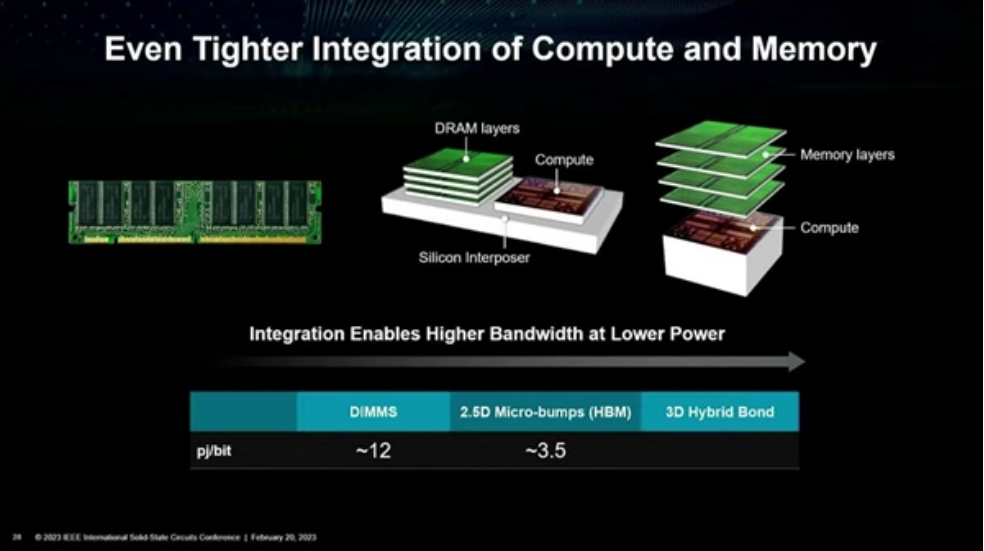

在先進(jìn)封裝技術(shù)研發(fā)方面,沒(méi)有芯片工廠的AMD也是不遺余力,特別是在HBM和GPU、CPU封裝方面。在ISSCC 2023國(guó)際固態(tài)電路大會(huì)上,AMD提出了多種新的封裝設(shè)想,其中之一是在服務(wù)器CPU模塊內(nèi)部,直接堆疊內(nèi)存,而且是多層堆疊。一種方式是將CPU模塊和內(nèi)存模塊并排封裝在硅中介層上,另一種方式是在計(jì)算模塊上方直接堆疊內(nèi)存,有點(diǎn)像手機(jī)SoC。

AMD表示,這種設(shè)計(jì)可以讓計(jì)算核心以更短的距離、更高的帶寬、更低的延遲訪問(wèn)內(nèi)存,還能降低功耗。如果堆疊內(nèi)存容量足夠大,主板上的DIMM插槽都可以省了。AMD甚至考慮在Instinct系列GPU已經(jīng)整合封裝HBM的基礎(chǔ)上,繼續(xù)堆疊DRAM,但只有一層,容量不會(huì)太大。這樣做的最大好處是一些關(guān)鍵算法可以直接在此DRAM內(nèi)執(zhí)行,不必在CPU和獨(dú)立內(nèi)存之間往復(fù)通信,從而提升性能、降低功耗。AMD還設(shè)想在2D/2.5D/3D封裝內(nèi)部,集成更多模塊,包括內(nèi)存、統(tǒng)一封裝光網(wǎng)絡(luò)通道物理層、特定域加速器等,并引入高速標(biāo)準(zhǔn)化的芯片間接口通道(UCIe)。

04結(jié)語(yǔ)

3D封裝是未來(lái)發(fā)展方向,這種多層結(jié)構(gòu)有很多優(yōu)點(diǎn):一、它通過(guò)增加芯片層次和連接方式,實(shí)現(xiàn)了更高的芯片集成度和功能密度;二、多層堆疊結(jié)構(gòu)減小了整個(gè)芯片的體積,使得電子設(shè)備變得更加輕薄便攜;三、多層堆疊提供了更高的性能和效率,可進(jìn)一步優(yōu)化電子設(shè)備的處理速度和能耗。HBM所涉及的封裝已經(jīng)是當(dāng)下最先進(jìn)的內(nèi)存封裝技術(shù)了,不過(guò),技術(shù)進(jìn)步的腳步一直沒(méi)有停歇,在擴(kuò)充現(xiàn)有先進(jìn)技術(shù)產(chǎn)線的基礎(chǔ)上,各大廠商還在研發(fā)更具前瞻性的技術(shù)。

據(jù)悉,三星電子先進(jìn)封裝(AVP)事業(yè)組正在研發(fā)新一代內(nèi)存技術(shù)“Cache DRAM”,目標(biāo)是在2025年開(kāi)始量產(chǎn)。與HBM相比,Cache DRAM功耗效率可改善60%,延遲將減少50%。封裝技術(shù)方面,Cache DRAM與HBM也有很大區(qū)別,HBM是水平連接至GPU,Cache DRAM則是與GPU垂直連接。當(dāng)然,不止三星,英特爾、臺(tái)積電、日月光等大廠都在開(kāi)發(fā)新的內(nèi)存封裝技術(shù),但具體情況還不得而知。在研發(fā)先進(jìn)封裝技術(shù)的道路上,需要解決的難題也很多,例如,隨著堆疊層數(shù)的增加,熱量的管理問(wèn)題越來(lái)越凸出,因?yàn)樵诰o密堆疊的芯片中,熱量散發(fā)變得更加困難。對(duì)此,科學(xué)家們正在不斷尋找解決方案,以保持芯片高性能工作狀態(tài)的穩(wěn)定性和可靠性。

審核編輯:黃飛

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論