在AI服務器中,內存帶寬問題越來越凸出,已經明顯阻礙了系統計算效率的提升。眼下,HBM內存很火,它相對于傳統DRAM,數據傳輸速度有了明顯提升,但是,隨著AI應用需求的發展,HBM的帶寬也有限制,而理論上的存算一體可以徹底解決“存儲墻”問題,但該技術產品的成熟和量產還遙遙無期。在這樣的情況下,3D DRAM成為了一個HBM之后的不錯選擇。

目前,各大內存芯片廠商,以及全球知名半導體科研機構都在進行3D DRAM的研發工作,并且取得了不錯的進展,距離成熟產品量產不遠了。

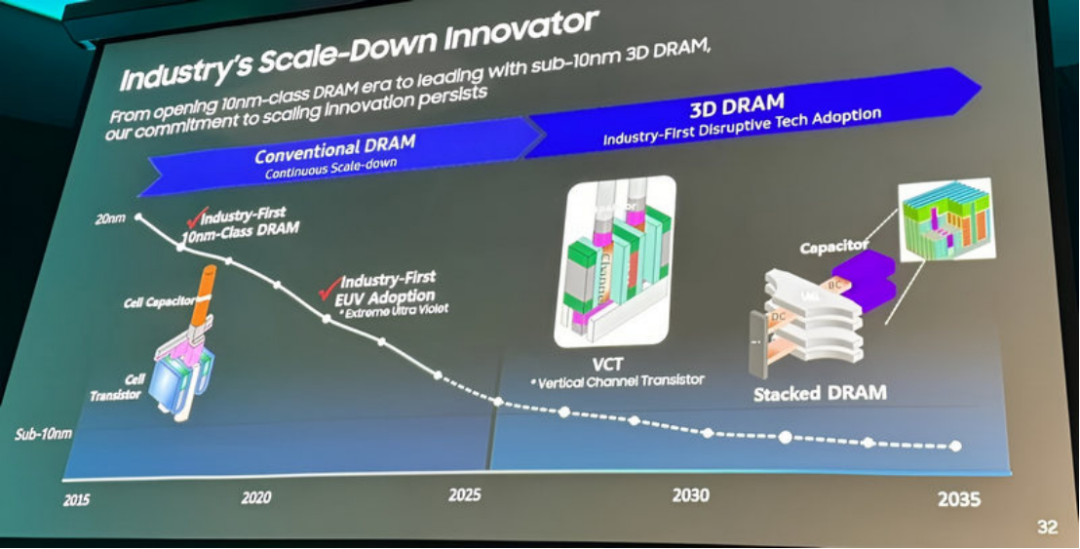

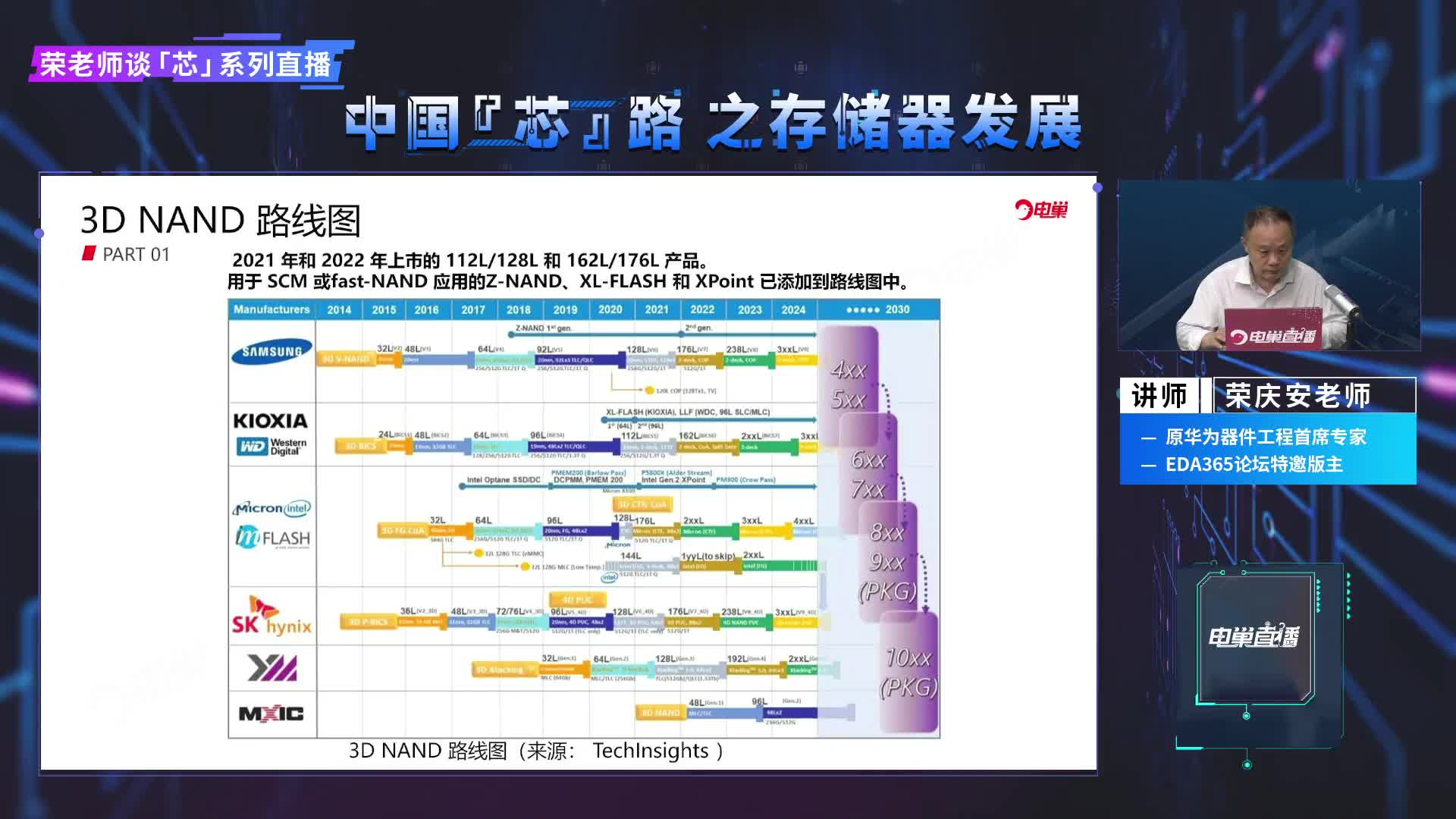

據首爾半導體行業消息人士透露,3月,三星電子在加利福尼亞州圣何塞舉行的全球芯片制造商峰會Memcon 2024上公布了其3D DRAM開發路線圖。

4月初,從三星電子傳來消息,該公司計劃在2025年推出基于其垂直通道晶體管技術的早期版本的3D DRAM,該技術在構成單元的晶體管中垂直設置一個通道,并用一個柵極包裹住它作為開關。該公司還計劃在 2030 年推出更新版本的堆疊式 DRAM,該DRAM可以堆疊包括電容器在內的所有單元。

01、3D DRAM的優勢何在?

AI應用對內存性能(速度和存儲密度等)的要求不斷提升。然而,在大幅度增長的數據量,以及處理器快速提升的算力面前,傳統的平面架構(2D)DRAM在存儲密度和速度方面越來越吃力,與此同時,目前的DRAM制程工藝已經接近極限(最先進的DRAM制程約為12nm),進一步提升越來越難,這是由DRAM的結構導致的,它的基本存儲單元是基于一個晶體管和一個電容器,目前的DRAM制程工藝擴展是在一個平面上進行的,工藝提升主要面臨兩個挑戰:一、電容器的縮放;二、電容到數字線的電荷共享,要考慮用多少時間將電荷轉移到數字線上、數字線有多長。存儲電容的深寬比會隨著制程工藝微縮而呈倍數增加,這就是平面DRAM工藝微縮越來越難的原因。

也就是說,傳統DRAM架構是平面型的,而在一個平面內加入更多存儲單元越來越困難。因此,類似于3D NAND,人們開始考慮將立體的3D架構帶入DRAM。3D DRAM將存儲單元堆疊在邏輯單元上方,以實現在單位面積上產出更多存儲容量,3D DRAM可以有效解決平面DRAM存儲電容高深寬比這一難題。此外,使用3D堆疊技術還能重復使用存儲電容,從而降低DRAM的單位成本。

由于3D DRAM中的晶體管堆疊為多層結構,這種結構可以擴大晶體管之間的間隙,從而減少電流泄漏。

總之,3D DRAM芯片是垂直堆疊存儲單元,而不是像傳統DRAM那樣水平放置所有單元,它將單位面積的容量增加了3倍(3D DRAM的基本容量為100GB,而當前DRAM的最大容量為36GB)。

就發展路線來看,據semiengineering報道,3D DRAM有兩條路,其中,最直接的方法是保留當前的DRAM 技術,并將多個芯片堆疊在彼此之上。這是用于HBM的高級封裝方法,常見的HBM芯片為4和8高,預計很快會達到16高。與傳統DRAM相比,這是一種更昂貴的方案,因為在封裝中堆疊die需要更先進的工藝,但對于需要大量高帶寬內存的應用(如AI)來說,這是值得的。

另外一條路,也是多數廠商追求的最終目標,那就是單片堆疊。這種方案只需少量額外步驟,但是,這些步驟會導致很多困難。為了實現這個目標,有分析人士認為3D DRAM 可以效仿3D NAND Flash,將存儲單元翻轉。因為DRAM 單元具有較小的2D區域,但具有較大的垂直方向電容器,使其很高且難以分層堆疊。而且,隨著 2D 尺寸越來越小,電容器越來越薄,它必須加長以保持足夠的電荷。

這就延申出了另外一個問題,那就是電容器問題。

在傳統DRAM的制造過程中,幾乎都是采用電路和存儲器堆疊在同一平面的方法來生產的,芯片制造商通過減小單元尺寸或間距來提高 DRAM 的性能。然而,他們達到了在有限空間內增加存儲單元數量的物理極限,這里有一個問題,如果電容器變得越來越薄,整個器件可能會崩潰。如果無法解決電容器問題,DRAM的存儲密度和數據傳輸帶寬就難以實現跨越式提升。因此,業界提出了無電容DRAM方案,再加上3D堆疊技術,有望實現3D DRAM的突破。

所謂無電容DRAM,就是在其存儲單元中,僅用一個晶體管來存儲信息,且使用具有不對稱雙柵極結構的多晶金屬氧化物硅半導體FET,通過floating body效應來存儲電荷(不需要外部電容器)。

目前,全球多家知名半導體科研機構都在進行無電容3D DRAM 的研究工作,具體技術包括Dynamic Flash Memory、VLT、Z-RAM和IGZO-FET等。不過,從目前的發展情況來看,包括存儲芯片三巨頭(三星電子、SK海力士和美光)在內的廠商還沒有披露更多關于無電容3D DRAM的細節。

02、各大廠商的研發進展

傳統DRAM需要復雜的讀寫數據操作流程,而3D DRAM可以通過垂直堆疊的存儲單元直接存取和寫入數據,顯著提高了存取速度。3D DRAM的優勢不僅包括高容量和快速數據訪問,還具有低功耗和高可靠性特點,可以滿足各種應用需求。

有機構預測,到2030年,全球3D DRAM市場規模有望增長到1000億美元。

正是看到了這樣的發展前景,以存儲芯片三巨頭為代表的廠商都在發力,進行相關技術和產品的研發。

如前文所述,三星電子計劃在2025年推出3D DRAM的量產產品。在三巨頭中,三星是對該技術最為關注的,投入也最大,3D DRAM可以幫助三星在未來的AI芯片市場占據優勢地位。而就目前來看,在AI內存市場,特別是HBM產品,SK海力士占據著主導地位,占有全球90%的HBM市場份額。三星要想趕超SK海力士,在HBM階段恐怕是難以實現了,只能寄希望于3D DRAM或其它更先進的技術方案。

盡管存儲三巨頭都在研究這項技術,但SK海力士和美光科技尚未公布任何3D DRAM發展路線圖。

下面分別看一下這三大存儲芯片廠商在3D DRAM方面的研發和進展情況。

三星電子想主導3D DRAM市場,一直在開發新技術。

自2019年以來,三星電子一直在進行3D DRAM的研究,并于同年10月宣布了業界首個12層3D-TSV(Through-Silicon Via)技術。

2021年,三星電子正式對外宣布其3D DRAM開發項目,當時,恰逢該公司在其DS部門內設立下一代工藝開發團隊,作為一項關鍵技術,3D DRAM包含其中,三星半導體業務公司總裁兼首席技術官宋齋赫(Song Jaihyuk)領導該團隊。

在2022年的SAFE論壇上,三星表示,準備通過邏輯堆疊芯片SAINT-D解決DRAM堆疊問題,該設計旨在將8個HBM3芯片集成在一起。

據消息人士稱,2023年5月,三星電子在其半導體研究中心內組建了一個開發團隊,大規模生產4F2結構DRAM。由于DRAM單元尺寸已達到極限,三星想將4F2應用于10nm級工藝或更先進制程的DRAM。如果三星的4F2 DRAM存儲單元結構研究成功,在不改變制程的情況下,裸片面積可比現有6F2 DRAM存儲單元減少約30%。

2023年10月,在“內存技術日”活動上,三星電子宣布計劃在下一代10nm級制程DRAM中引入新的3D結構,而不是傳統的2D結構。

2023年,在日本舉行的“VLSI研討會”上,三星電子發表了一篇包含3D DRAM研究成果的論文,并展示了3D DRAM芯片內部結構的圖像。

據報道,三星電子在美國硅谷開設了一個新的研發實驗室,主要進行3D DRAM研發。據悉,該實驗室隸屬于硅谷的Device Solutions America (DSA)部門,負責監督三星電子在美國的半導體生產,并專注于新一代DRAM產品的開發。

除了要在2025年量產,三星電子還要在2027~2028年將相關制程節點縮小到8nm~9nm,目前,最先進的DRAM制程約為12nm。

下面看一下SK海力士和美光。

雖然沒有明確的發展路線圖,但SK海力士在一些行業會議上介紹過該公司對3D DRAM的理解。據BusinessKorea報道,負責SK海力士未來技術研究所的副總裁Cha Seon-yong表示,2024年,SK海力士將會披露3D DRAM電氣特性的相關細節,到時候,該公司將會明確3D DRAM的發展方向。

據外媒報道,SK海力士正在為將來的DRAM開發IGZO通道材料,它可以改善DRAM的刷新特性。據悉,IGZO薄膜晶體管憑借其適中的載流子遷移率、極低的漏電流以及基板尺寸的可擴展性,在顯示面板行業長期得到應用。它可以成為未來 DRAM 可堆疊通道材料的候選方案。

美光在2019年就開始了3D DRAM的研究工作。據TechInsights統計,到2022年8月,美光獲得了30多項3D DRAM專利,三星電子持有的專利數為15項,SK海力士持有約10項專利,可以看出,美光的3D DRAM相關專利數量是這兩家韓國存儲芯片巨頭的2-3倍。

除了大廠,有些創業公司也在進行3D DRAM開發。

例如,美國公司NEO Semiconductor推出了一種名為3D X-DRAM的技術,旨在克服DRAM的容量限制。3D X-DRAM的單元陣列結構類似于3D NAND Flash,采用了FBC技術,它可以通過添加層掩模形成垂直結構,從而實現高良率、低成本和顯著的密度提升。

據NEO介紹,3D X-DRAM 技術可以跨230層實現128Gb的密度,是當前DRAM密度的8倍。NEO提出了每10年容量增加8倍的目標,計劃在2030~2035年實現1Tb的容量,比目前DRAM的容量增加64倍。

由于內存與處理器聯系非常緊密,因此,3D DRAM技術的研究工作并未局限于存儲芯片廠商,CPU等處理器大廠也很關注。

由于在Chiplet(小芯片)技術的商業化上取得了成功,AMD想在HPC用處理器(CPU和GPU)方面更進一步,一種設想是在不久的將來在計算Chiplet上堆疊DRAM。在ISSCC 2023峰會上,AMD在其演示文稿中詳細介紹了如何提高數據中心能效,其中,對用于服務器處理器和HPC加速器的多層堆疊DRAM的介紹十分引人注目,該公司預測這將是未來HPC用內存的一個發展方向。

近些年,華為在CPU、AI等HPC上投下重注,要想在這方面進入產業前沿,同樣躲不開內存技術的改進問題。在VLSI Symposium 2022上,華為發表了一篇關于3D DRAM的論文,詳細介紹了該公司采用的垂直CAA型IGZO FET技術,該研究項目可以推動IGZO晶體管在高密度DRAM領域的應用。

除了企業(特別是大型存儲芯片和處理器廠商),全球多家知名半導體科研機構,包括中國知名的科研院所,也都在進行3D DRAM的研究工作,就不在此一一贅述了。

03、結語

目前,AI正在各行各業滲透,大到數據中心和云計算服務器,小到手機。在可預見的未來,沒有AI能力的設備將很難在市場上競爭。而AI對處理器和內存提出的要求越來越高,眼下,在手機等小型計算系統中,傳統LPDDR還可以滿足應用需求,將來則很有可能被淘汰;而在大型計算系統當中,HBM冉冉升起,但用不了多少年,其存儲密度和數據傳輸帶寬也將難以保障應用升級。此時,3D DRAM是一個更好的方案。

從長遠來看,汽車行業也有望使用3D DRAM,因為智能化的電動汽車和自動駕駛技術需要能夠實時處理從道路上收集的大量數據,此時,如果只有處理器性能提升,而DRAM不能滿足要求,不會有好的效果和駕駛、乘坐體驗,必須保證DRAM不存在存儲密度和帶寬短板,才能充分發揮汽車智能化和自動駕駛系統的性能。

因此,在多個應用市場不斷發展的情況下,3D DRAM擁有廣闊的增長空間。

審核編輯:黃飛

?

電子發燒友App

電子發燒友App

評論