1. 背景 這篇文章主要介紹了DDR3IP核的寫實現。 2. 寫命令和數據總線介紹 DDR3 SDRAM控制器IP核主要預留了兩組總線,一組可以直接綁定到DDR3 SDRAM芯片端口,一組是留給

2020-12-31 11:17:02 5156

5156

2、512Mb-2Gb LP DDR2,以及?LP DDR4x、LP DDR3、LP DDR、SDRAM,適用于需配備4Gb 或以下容量DRAM 的應用,?如人工智能加速器、物聯網、汽車、工業用、電信、

2022-04-20 16:04:03 2594

2594

DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory,雙數據率同步動態隨機存儲器)通常被我們稱為DDR,其中的“同步

2023-03-07 11:29:43 3336

3336

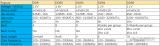

DDR內存1代已經淡出市場,直接學習DDR3 SDRAM感覺有點跳躍;如下是DDR1、DDR2以及DDR3之間的對比。

2023-04-04 17:08:47 3132

3132

DDR SDRAM參考設計VHDL版(有詳細的文檔,仿真綜合文件)File/Directory Description

2012-08-11 09:33:30

引言 很多嵌入式系統,特別是應用于圖像處理與高速數據采集等場合的嵌入式系統,都需要高速緩存大量的數據。DDR(Double DataRate,雙數據速率)SDRAM由于其速度快、容量大,而且價格便宜

2018-12-18 10:17:15

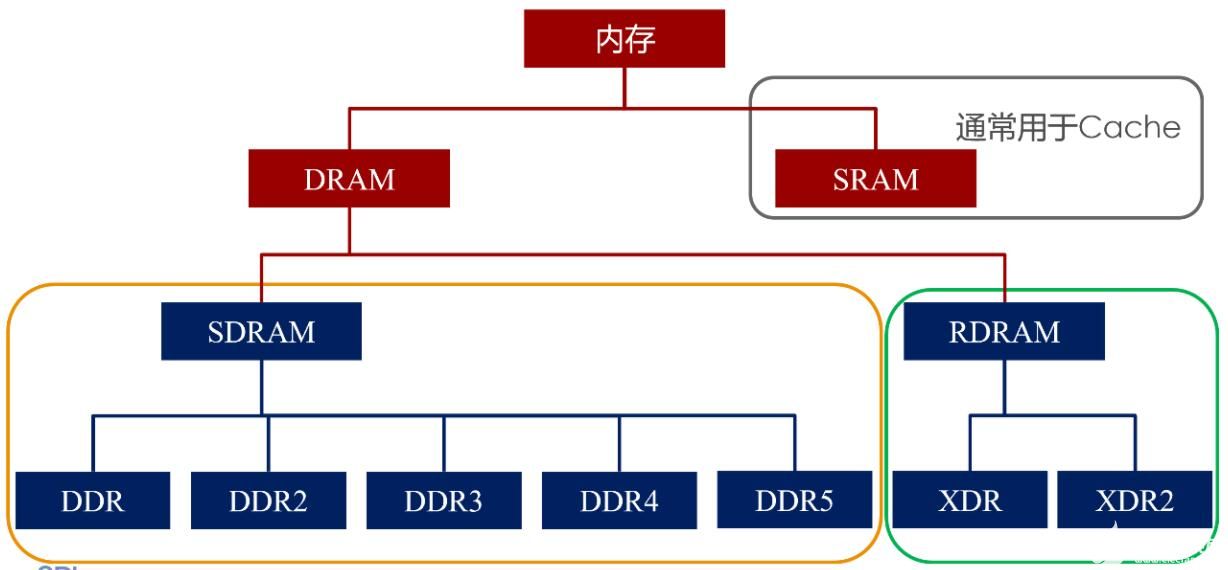

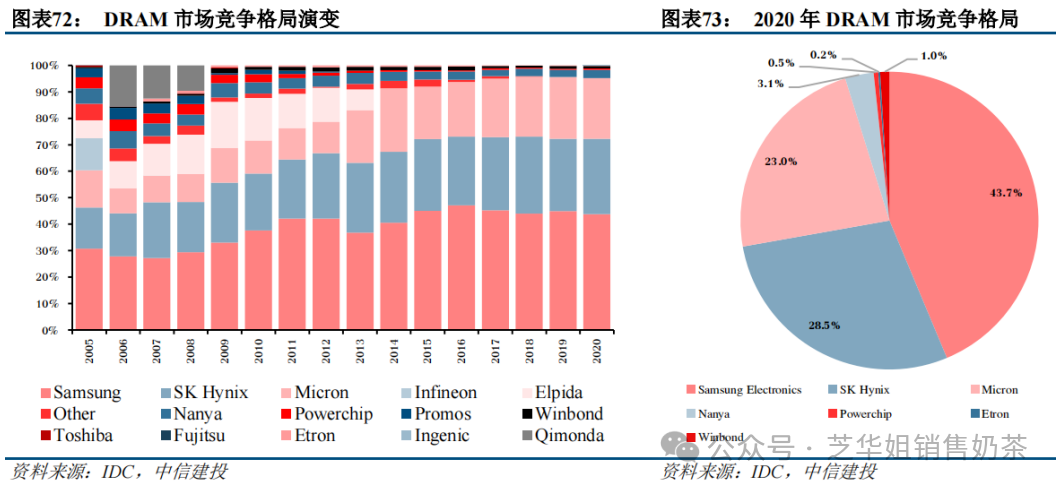

DDR SDRAM內存發展歷程

2021-01-06 06:04:22

DDR SDRAM訪問特性DDR控制器效率對比

2021-02-04 07:14:23

我手上有一張DDR200T的開發板,板載了一塊512M的SDRAM內存,板子燒了一個UX600的demosoc,我是要在這個板子跑RT-Thread。

要是想使用這塊SDRAM應該怎么做呢?應該

2023-08-11 08:05:46

DDR4 SDRAM的尋址方式有哪些?

2021-10-27 06:50:24

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之處?

2021-03-12 06:22:08

DDR_SDRAM控制器的VHDL代碼已經測試

2016-08-24 16:49:35

使用公式分析和理論分析兩種方法,以實例證明公式的局限性和兩種方法的利弊。本文最后還基于這些實例分析,給出了SDRAM和DDR SDRAM等布線的一般性原則。

2021-05-19 06:52:58

SDRAM和DDR布線技巧ecos應用是與硬件平臺無關的,雖然開發板沒有涉及到SDRAM和DDR,不過,在某些高端平臺上使用ecos可能會遇到內存布線問題,為了完整敘述,這里一并給出說明。&

2010-03-18 15:33:07

SDRAM和DDR的具體區別是什么?

2021-06-18 07:58:51

;如果上一次執行了寫操作,則此次執行讀操作。如果不是同時出現讀寫請求,則是什么請求就執行什么操作。2)采用全頁模式的讀寫操作,該模式在讀、寫完成時,需要給出預充電命令才能結束。3)刷新請求始終優于讀、寫請求。DDR的時序與SDRAM是相似的,學好SDRAM后,理解DDR2和DDR3就非常容易了。

2017-11-23 11:02:27

XILINX 關于FPGA 對DDR SDRAM 的設計文檔

2012-08-17 09:20:26

最近在設計一個需要連接DDR2 SDRAM的FPGA小系統,由于是第一次在使用SDRAM,在硬件連接時就遇到一個很糾結的問題——引腳的連接。看了幾種參考設計,發現有兩種說法:1、DDR2的數據(DQ

2017-09-25 17:51:50

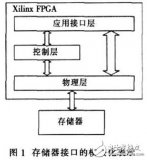

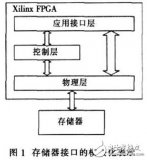

基于Xilinx FPGA的DDR2 SDRAM存儲器接口

2012-08-20 18:55:15

嗨!我正在尋找Spartan-3A / 3ANFPGA入門KitBoard用戶指南(UG334)。具體來說第13章:DDR2 SDRAM和我不明白如何使用DDR2 SDRAM,因為例如這個內存

2019-07-31 06:18:10

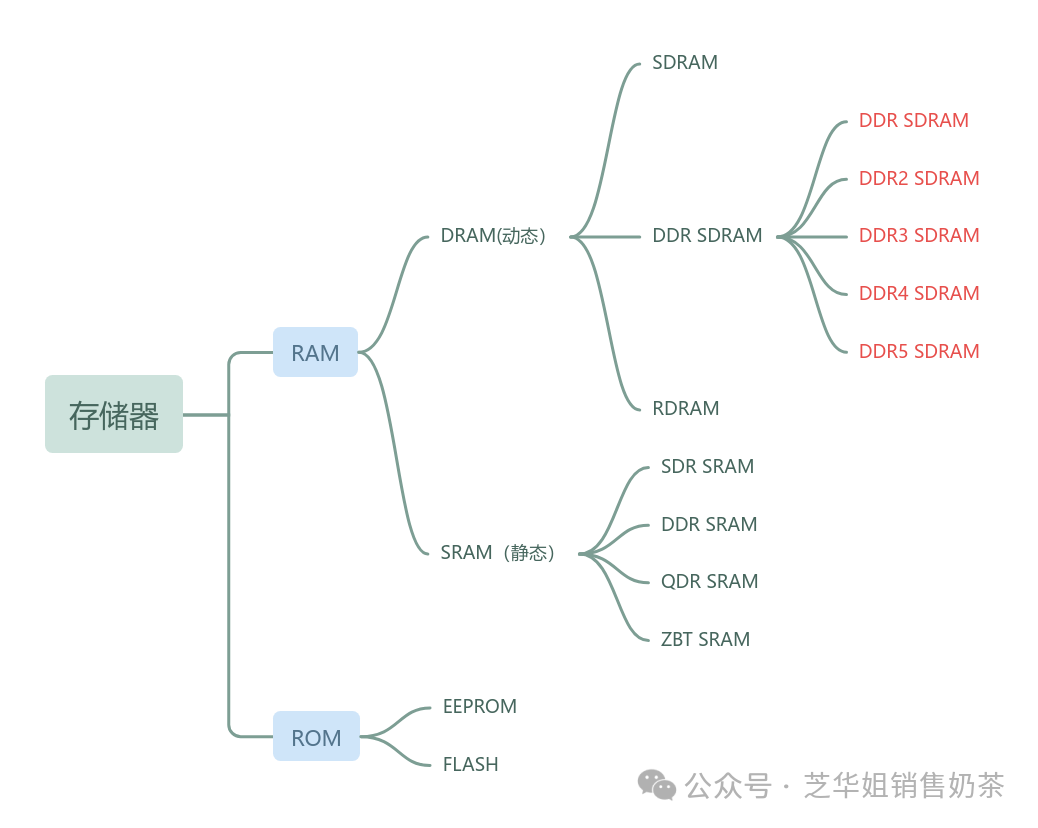

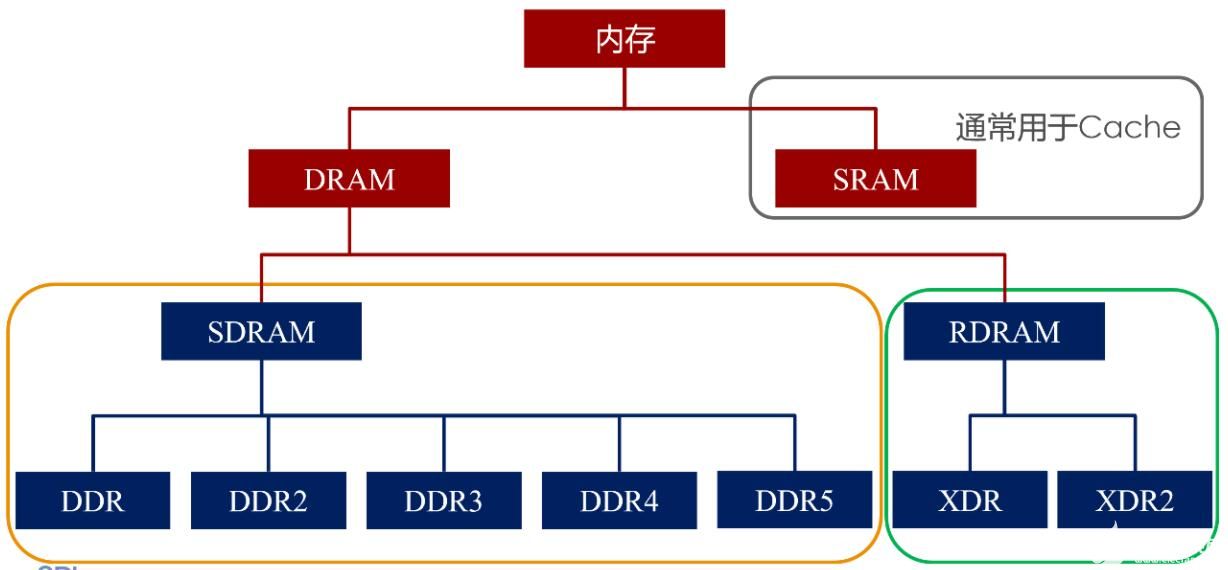

本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2021-04-20 06:30:52

有過深入了解的網友,相信通過比較,對今后快速上手DDR/DDR2的操作就如抬腿再上一個臺階一樣輕便。 這篇文章不談具體的細節,只重點談差異,DDR SDRAM的結構框圖,這重點要來說為何DDR

2014-12-30 15:22:49

DDR SDRAM在嵌入式系統中有哪些應用?DDR SDRAM的工作方式有哪幾種?怎樣去設計DDR SDRAM控制器?

2021-04-30 07:04:04

,F-RAM,MRAM(非易失性存儲器)256Kbit-16Mbit8.Mobile SDRAM/DDR(低功耗SDRAM/DDR)128Mbit-512Mbit9.DDR2/DDR3 SDRAM (動態隨機

2013-08-30 10:31:33

DDR SDRAM is a 2n prefetch architecture with two data transfers perclock cycle. In the 2n prefetch

2009-03-28 14:43:47 56

56 files *top.v* is the source file for DDR SDRAM controller

2009-05-14 10:46:50 37

37 ref ddr sdram verilog源代碼

File/Directory Description

2009-06-14 08:48:01 82

82 =============================================doc DDR SDRAM reference design documentationmodel Contains the vhdl SDRAM model

2009-06-14 08:49:23 51

51 DDR2 SDRAM控制器的設計與實現

本文介紹了&&," -&,+. 的基本特征!并給出了一種&&," -&,+. 控制器的設計方法!詳述了其基本結構和設計思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 SDRAM的原理和時序

SDRAM內存模組與基本結構 我們平時看到的SDRAM都是以模組形式出現,為什么要做成這種形式呢?這首先要接觸到兩個概念:物理Bank與芯片位寬

2010-03-11 14:43:26 167

167 SDRAM與DDR布線指南:ecos應用是與硬件平臺無關的,雖然開發板沒有涉及到SDRAM和DDR,不過,在某些高端平臺上使用ecos可能會遇到內存布線問題,為了完整敘述,這里一并給出說明。 很

2010-03-18 15:29:08 0

0 SDRAM設計詳細說明

完成SDRAM的上層驅動設計,對SDRAM讀寫、管理無誤,與其他模塊的接口正確。

口令:MMCTEAM

SDRAM的工作原理

2010-04-22 14:02:57 0

0 嵌入式測試和測量挑戰目錄引言3-4DRAM發展趨勢 3DRAM4-6SDRAM 6-9DDR SDRAM6DDR2 SDRAM 7DDR3 SDRAM 8DDR4 SDRAM 9GDDR 和LPDDR 9DIMMs 9-13DIMM 物理尺寸 9DIMM

2010-06-30 09:28:08 94

94 本文介紹了DDR3 SDRAM 的基本特點和主要操作時序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設計方法。詳述了控制器基本結構和設計思想,分析了各模塊功能與設計注意事項,并

2010-07-30 17:13:55 30

30 DDR2 SDRAM 和 FB-DIMM的電氣檢驗:

隨著DDR2 SDRAM時鐘頻率和信號邊沿速率不斷提高,檢查電路板結構、電氣系統和信令正變得越來越重要。本應用指南介紹了電路板、電源系統、

2010-08-06 08:29:01 39

39 不只計算機存儲器系統一直需要更大、更快、功率更低、物理尺寸更小的存儲器,嵌入式系統應用也有類似的要求。本應用指南介紹了邏輯分析儀在檢驗DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 80

80 本文將介紹DDR SDRAM的一些概念和難點,主要結合上一篇SDRAM的介紹加以對比。同時著重講解主流DDRII的技術。最后結合硬件設計提出一些參考。

DDR SDRAM全稱為Double Dat

2010-08-30 16:26:16 119

119 什么是SDRAM內存

SDRAM是“Synchronous Dynamic random access memory”的縮寫,意思是“同步動態隨機存儲器”,就是我們平時所說的“同步內存”,這種

2009-12-17 11:14:39 729

729 什么是DDR SDRAM內存

DDR是一種繼SDRAM后產生的內存技術,DDR,英文原意為“DoubleDataRate”,顧名思義,就是雙數據傳輸模式。之所以稱其為“雙”,也

2009-12-17 11:15:53 1670

1670 什么是DDR2 SDRAM

DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設備工程聯合委員會)進行開發的新生代內存技

2009-12-17 11:17:59 627

627 SDRAM內存 SDRAM是Synchronous Dynamic Random Access Memor

2009-12-17 16:15:28 645

645 DDR SDRAM內存

DDR SDRAM是Double Dat

2009-12-17 16:20:33 687

687 文中在介紹DDR2的工作原理的基礎上,給出了一個用VHDL語言設計的DDR2 SDRAM控制器的方法,并且提出了一種在高速圖像處理系統中DDR2 SDRAM的應用方案,同時在Virtex-5系列的FPGA上得到了實現

2011-07-23 10:03:16 5139

5139 定義了時鐘單位階躍信號C(n) 提出了一種利用帶相對時鐘坐標的邏輯方程表示邏輯信號的方法通過對所設計的DDR SDRAM控制器的讀寫時序的分析建立了控制器主要信號的時序表達式并利用

2011-09-26 15:34:12 39

39 雖然目前SDRAM內存條價格已經接底線,內存開始向DDR和Rambus內存過渡。但是由于DDR內存是在SDRAM基礎上發展起來的,所以詳細了解SDRAM內存的接口和主板設計方法對于設計基于DDR內存的主

2012-01-05 16:21:11 247

247 使用功能強大的FPGA來實現一種DDR2 SDRAM存儲器的用戶接口。該用戶接口是基于XILINX公司出產的DDR2 SDRAM的存儲控制器,由于該公司出產的這種存儲控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 237

237 DDR SDRAM 全稱為Double Data Rate SDRAM,中文名為雙倍數據流SDRAM。DDRSDRAM 在原有的SDRAM 的基礎上改進而來。也正因為如此,DDR 能夠憑借著轉產成本優勢來打敗昔日的對手RDRAM,成為當今的主流

2013-09-13 15:17:30 210

210 ddr2_sdram 操作時序,非常好的教程,可以充分了解DDR2

2015-10-28 11:07:39 20

20 DDR_SDRAM介紹和時序圖,DDR_SDRAM介紹和時序圖

2016-02-23 11:58:38 6

6 Xilinx FPGA工程例子源碼:DDR SDRAM控制器參考設計VHDL代碼

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源碼:DDR SDRAM控制器verilog代碼

2016-06-07 14:13:43 38

38 一種面向多核系統的DDR2SDRAM控制單元_章裕

2017-01-03 18:00:37 5

5 作者:Steve Leibson, 賽靈思戰略營銷與業務規劃總監 Adrian Cosoroaba和Terry Magee在本月MemCon上給出了關于DDR4 SDRAM接口的詳細展示,該演示

2017-02-08 14:03:01 638

638 DDR2SDRAM控制器在機載顯控系統中的應用_孫少偉

2017-03-19 11:26:54 1

1 DDR2_DDR3_SDRAM,PCB布線規則指導

2017-10-31 10:06:48 78

78 DDR3 SDRAM(Double Data Rate Three SDRAM):為雙信道三次同步動態隨機存取內存。

DDR4 SDRAM(Double Data Rate Fourth

2017-11-17 13:15:49 25363

25363 為了滿足高速圖像數據采集系統中對高帶寬和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的設計方法,提出了一種基于Verilog-HDL 語言的DDR3 SDRAM

2017-11-17 14:14:02 3334

3334

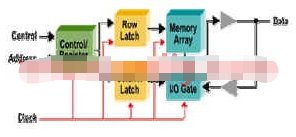

在高速信號處理系統中, 需要緩存高速、大量的數據, 存儲器的選擇與應用已成為系統實現的關鍵所在。DDR SDRAM是一種高速CMOS、動態隨機訪問存儲器, 它采用雙倍數據速率結構來完成高速操作

2018-07-20 18:38:00 12809

12809

邏輯復雜,接口方式與普通的存儲器差異很大。為了解決這個矛盾,需要設計專用的SDRAM控制器,使用戶像使用SRAM -樣方便的使用SDRAM。考慮到控制器的通用性,本文中提出了一種通用的SDRAM控制器的FPGA設計,FPGA內部采用狀態機的方式。該設計采用了AD公

2017-11-28 19:51:26 5

5 DRAM (動態隨機訪問存儲器)對設計人員特別具有吸引力,因為它提供了廣泛的性能,用于各種計算機和嵌入式系統的存儲系統設計中。本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 91807

91807 DDR SDRAM全稱為Double Data Rate SDRAM,中文名為雙倍數據流SDRAM。DDR SDRAM在原有的SDRAM的基礎上改進而來。也正因為如此,DDR能夠憑借著轉產成本優勢

2018-03-16 14:24:01 32

32 本文主要介紹的是ARM里的RAM和SDRAM有什么區別,首先介紹了RAM的類別及特點,其次對SDRAM做了詳細闡述,最后介紹了RAM和SDRAM的區別是什么。

2018-04-27 16:20:52 34218

34218 實現數據的高速大容量存儲是數據采集系統中的一項關鍵技術。本設計采用Altera 公司Cyclone系列的FPGA 完成了對DDR SDRAM 的控制,以狀態機來描述對DDR SDRAM 的各種時序

2019-08-14 08:00:00 3440

3440

本文檔的主要內容詳細介紹的是FPGA讀寫SDRAM的實例和SDRAM的相關文章及一些SDRAM控制器設計論文主要包括了:FPGA讀寫SDRAM的實例,SDRAM控制器核心介紹,系列SDRAM數據手冊

2018-12-25 08:00:00 56

56 SDRAM從發展到現在已經經歷了五代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代,DDR4 SDRAM。

2019-09-12 07:02:00 2057

2057

SDRAM在計算機中被廣泛使用,從起初的SDRAM到之后一代的DDR(或稱DDR1),然后是DDR2和DDR3進入大眾市場,2015年開始DDR4進入消費市場。

2019-09-11 07:09:00 2278

2278

DDR2 設備概述:DDR2 SDRAM接口是源同步、支持雙速率傳輸。比如DDR SDRAM ,使用SSTL 1.8V/IO電氣標準,該電氣標準具有較低的功耗。與TSOP比起來,DDR2 SDRAM的FBGA封裝尺寸小得多。

2019-06-22 10:05:01 1835

1835

本文件定義了DDR3 SDRAM規范,包括特性、功能、交直流特性、封裝和球/信號分配。本文檔的目的是為符合jedec的512 MB到8 GB的x4、x8和x16 ddr3 sdram設備定義一組最低

2019-11-04 08:00:00 75

75 H57V1262GTR SDRAM模塊B型

SDRAM外擴存儲 8Mx16bit

型號 SDRAM Board (B)

2019-12-30 09:01:47 1234

1234

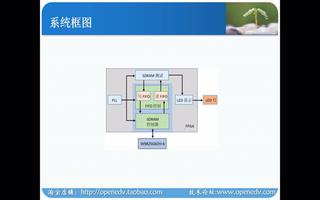

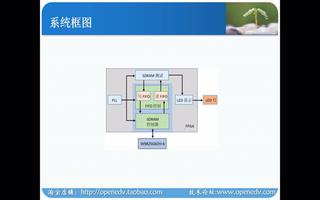

學完SDRAM控制器后,可以感受到SDRAM的控制器的書寫是十分麻煩的,因此在xilinx一些FPGA芯片內已經集成了相應的IP核來控制這些SDRAM,所以熟悉此類IP核的調取和使用是非常必要的。下面我們以A7的DDR3 IP核作為例子進行IP核調取。

2019-11-10 10:28:45 4758

4758

DDR5 是第五代 DDR SDRAM 的簡稱,DDR SDRAM 是英文 Double Data Rate SDRAM 的縮寫,中文譯為雙倍速率 SDRAM,而 SDRAM 又是

2020-02-03 18:30:59 5506

5506 SDRAM從發展到現在已經經歷了五代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代DDR4 SDRAM。第一代SDRAM

2020-04-03 16:04:01 1529

1529 DDR2 SDRAM采用雙數據速率結構實現高速運行。雙數據速率體系結構本質上是4n預取體系結構,其接口設計為在I/O球處每個時鐘周期傳輸兩個數據字。DDR2 SDRAM的單次讀寫操作有效地包括在內部

2020-05-21 08:00:00 1

1 DDR SDRAM是具有雙倍數據傳輸率的SDRAM,其數據傳輸速度為系統時鐘頻率的兩倍,由于速度增加,其傳輸性能優于傳統的SDRAM。DDR SDRAM 在系統時鐘的上升沿和下降沿都可以進行

2020-07-16 15:44:10 1967

1967 SDRAM從發展至今歷經了五代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代DDR4 SDRAM,SDRAM有一個同步

2020-07-24 14:25:27 739

739 DDR SDRAM的原理及特點:DDR SDRAM不需要提高時鐘頻率就能加倍提高SDRAM的速度,因為它允許在時鐘脈沖的上升沿和下降沿讀寫數據。至于地址和控制信號,還是跟傳統的SDRAM一樣,在時鐘的上升沿進行傳輸。

2020-08-10 17:33:21 616

616

SDRAM從SDR到DDR再到DDR2一路走來,又都產生了什么樣的變化,又都在哪些方面進行了改進,帶來了速度性能的進一步提升呢?

2020-09-26 11:47:34 10771

10771 針對SDRAM 操作繁瑣的問題,在對SDRAM 存儲器和全頁突發式操作進行研究的基礎上,提出一種簡易SDRAM 控制器的設計方法。該設計方法充分利用全頁式高效率存取的優點,對SDRAM 進行配置、全頁突發式讀寫時,操作方便。在實現sDRAM 的快速批量存儲方面,具有良好的應用價值。

2020-12-18 16:13:18 6

6 。SDRAM可稱為SDRSDRAM。 DDR其實指的是DDRSDRAM,SDRAM及DDR主要差異有三點整理如下: SDRAM與DDR的主要差異

2021-02-22 15:35:48 3181

3181

本文首先分析了DDR SDRAM的基本特征,并提出了相應的解決方案詳細介紹了基于J EDEC DDR SDRAM規范的DDR SDRAM控制器設計方案。該控制器采用Verilog HDL硬件描述語言實現,并集成到高性能SoC中。

2021-03-28 10:57:24 18

18 基于FPGA的DDR3SDRAM控制器設計及實現簡介(arm嵌入式開發平臺PB)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現簡介資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的DDR3SDRAM控制器設計及實現(嵌入式開發式入門)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 13:07:09 36

36 APM32E103VET6S_SDRAM模塊_SDRAM與IO口沖突問題

2022-11-09 21:03:42 0

0 8Gb DDR4 SDRAM B裸片組織為128Mbit x 4 I/O x16banks或64Mbit x8 I/O x 16banks設備。此同步設備實現高達2666Mb/sec的高速雙數

2022-12-05 11:54:24 13

13 DDR3 SDRAM使用雙倍數據速率架構來實現高速操作。雙倍數據速率結構是一種8n預取架構,其接口經過設計,可在I/O引腳上每個時鐘周期傳輸兩個數據字。DDR3 SDRAM的單個讀或寫操作有效地包括

2023-02-06 10:12:00 8

8 DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory,雙數據率同步動態隨機存儲器)通常被我們稱為DDR

2023-03-07 11:33:57 1760

1760 SDRAM有多種標準,包括DDR(Double Data Rate)、DDR2、DDR3和DDR4。每個標準都具有不同的物理規格和數據傳輸速率。DDR4是現代計算機中使用的最新型號,它具有更高的頻率和更大的容量。

2023-08-26 11:57:42 2307

2307 電子發燒友網站提供《PIC32系列參考手冊之DDR SDRAM控制器.pdf》資料免費下載

2023-09-25 11:39:59 0

0 SDRAM與DDR布線指南

2022-12-30 09:20:50 11

11 JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-25 09:51:55 9

9 在計算機運算速度發展的過程中,需要提高內存的讀寫速率,只能通過提高時鐘頻率來提高SDRAM的讀寫速率。由于溫度等因素的影響,SDRAM的內核時鐘頻率受限,無法進一步提升。

2024-04-06 09:26:00 157

157

電子發燒友App

電子發燒友App

評論