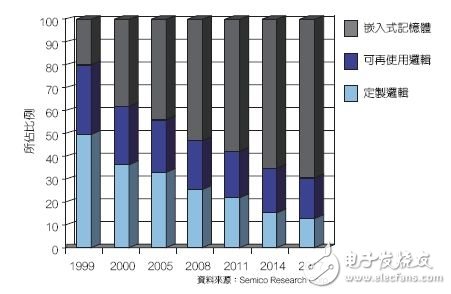

在傳統(tǒng)的大規(guī)模ASIC和SoC設(shè)計(jì)中,晶片的實(shí)體空間大致可分為用于新的定制邏輯、用于可再使用邏輯(第三方IP或傳統(tǒng)的內(nèi)部IP)以及用于嵌入式存儲(chǔ)器三部份。

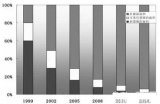

當(dāng)各家廠商為晶片產(chǎn)品的市場(chǎng)差異化(用于802.11n的無(wú)線DSP+RF、藍(lán)牙和其他新興無(wú)線標(biāo)準(zhǔn))持續(xù)開(kāi)發(fā)專(zhuān)有的自定義模組,第三方IP(USB核心、乙太網(wǎng)路核心以及CPU/微控制器核心)占用的晶片空間幾乎一成未變,嵌入式存儲(chǔ)器所占比例卻顯著上升(參見(jiàn)圖1)。

圖1:目前的ASIC和SoC設(shè)計(jì)中,嵌入式存儲(chǔ)器在可用晶片的總空間中所占比例逐漸升高

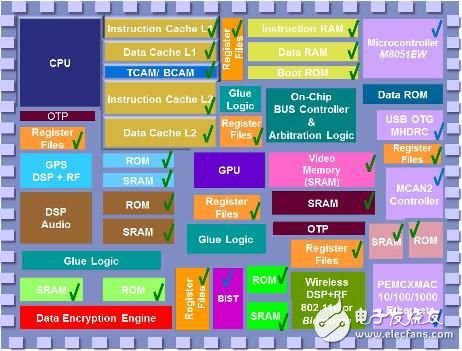

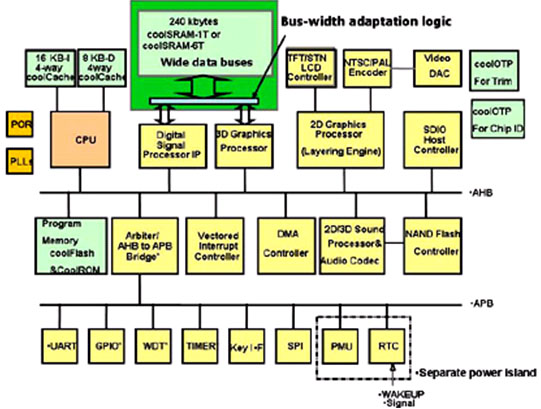

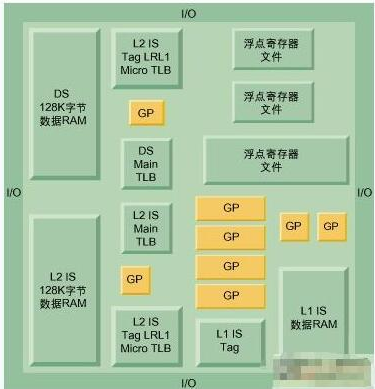

Semico Research 2013年發(fā)布的資料顯示,大多數(shù)SoC和ASIC設(shè)計(jì)中,各式嵌入式存儲(chǔ)器占用的晶片空間已超過(guò)50%。此外,許多大規(guī)模SoC嵌入式存儲(chǔ)器的使用目的和主要性能也各不相同,如圖2所示。

圖2:多核心SoC的各種嵌入式存儲(chǔ)器IP

由于可以根據(jù)設(shè)計(jì)目的,透過(guò)采用正確的SoC存儲(chǔ)器類(lèi)型來(lái)最佳化設(shè)計(jì),因此,對(duì)于設(shè)計(jì)者來(lái)說(shuō),利用各種存儲(chǔ)器IP具有非常重要的意義。設(shè)計(jì)者可透過(guò)恰當(dāng)分配各種存儲(chǔ)器IP所占比例,實(shí)現(xiàn)速度、功耗、空間(密度)以及非揮發(fā)性等各種性能參數(shù)的最佳化。

嵌入式存儲(chǔ)器的主要設(shè)計(jì)標(biāo)準(zhǔn)

各種應(yīng)用設(shè)計(jì)中,最佳存儲(chǔ)器IP的確定主要基于以下5個(gè)驅(qū)動(dòng)因素,如圖3所示,包括功率、速度、可靠性/良率、密度,以及成本。

圖3:確定存儲(chǔ)器IP的主要因素

透過(guò)針對(duì)上述各種性能決定要素進(jìn)行權(quán)衡,可得到最佳化解決方案。許多情況下,存儲(chǔ)器編譯器可根據(jù)輸入存儲(chǔ)器設(shè)計(jì)產(chǎn)生制程中的各種驅(qū)動(dòng)因素,自動(dòng)產(chǎn)生性能經(jīng)最佳化的特定存儲(chǔ)器IP。同樣重要的是,存儲(chǔ)器IP的支持性架構(gòu)應(yīng)適用可靠的驗(yàn)證方法,且產(chǎn)生的IP良率最高。最后,為了實(shí)現(xiàn)產(chǎn)量與品質(zhì)最最佳化,存儲(chǔ)器編譯器還應(yīng)直接產(chǎn)生GDSII,無(wú)需人工干預(yù)或調(diào)整。其他要素還包括良好的設(shè)計(jì)余量控制、對(duì)自動(dòng)化測(cè)試圖形向量產(chǎn)生和內(nèi)建自測(cè)試(BIST)的支持。此外,最好具備通過(guò)BIST的單步執(zhí)行進(jìn)行硅片除錯(cuò)的功能。

功率 強(qiáng)大的編譯器加上先進(jìn)的電路設(shè)計(jì),可大幅降低動(dòng)態(tài)功耗(CV2f),并可透過(guò)利用多晶片組、先進(jìn)的計(jì)時(shí)方法、偏置方法、電晶體Leff特徵控制以及多重供應(yīng)電壓(VT)最佳化等技術(shù)大幅地降低泄漏功率。設(shè)計(jì)者可整合運(yùn)用這些存儲(chǔ)器技術(shù),透過(guò)電壓和頻率的調(diào)整以及多電源域的利用,得到最理想的結(jié)果。

速度 為了實(shí)現(xiàn)最佳化的存儲(chǔ)器性能,充分利用先進(jìn)設(shè)計(jì)技術(shù)至關(guān)重要。設(shè)計(jì)者可利用存儲(chǔ)器編譯器對(duì)速度(例如存取時(shí)間或循環(huán)時(shí)間)、空間、動(dòng)態(tài)功耗以及靜態(tài)功耗(泄漏功率)等因素進(jìn)行權(quán)衡,得到所需要的最佳組合。在透過(guò)多種VT技術(shù)、多晶片組以及多種儲(chǔ)存單元等的合成選用,改進(jìn)存儲(chǔ)器塊的同時(shí),輔以節(jié)能設(shè)計(jì)技術(shù),同樣可以獲得較高速度。

可靠性與良率 電晶體體積和能耗的大幅下降,雖然使噪音容限明顯減少,但也對(duì)極深次微米晶片的可靠性帶來(lái)了影響。因此,為提高良率,改善執(zhí)行的可靠性,需采用ECC和冗余技術(shù)。

由于現(xiàn)在SoC的位元數(shù)已十分龐大,因此,嵌入式存儲(chǔ)器便成為決定SoC良率的最重要因素。在提高存儲(chǔ)器良率方面,由于可減少量產(chǎn)時(shí)間,控制測(cè)試與修復(fù)成本,因此專(zhuān)有測(cè)試與修復(fù)資源具有重要作用。采用一次可程式儲(chǔ)存技術(shù)制造的存儲(chǔ)器IP,在晶片制造完成后,產(chǎn)生儲(chǔ)存資訊失效時(shí),其內(nèi)建自修復(fù)功能便可對(duì)存儲(chǔ)器陣列進(jìn)行修復(fù)。理想情況下,為在生產(chǎn)測(cè)試過(guò)程中,快速進(jìn)行修復(fù)編程,存儲(chǔ)器編譯器的修復(fù)功能必須與晶片測(cè)試工具緊密整合。

對(duì)于設(shè)計(jì)者來(lái)說(shuō)極其重要的是,可根據(jù)需要選擇由晶圓代工企業(yè)制造位單元,或者進(jìn)行自我設(shè)計(jì)。當(dāng)需要進(jìn)行客制設(shè)計(jì)時(shí),與理解客制設(shè)計(jì)且可為各制程節(jié)點(diǎn)提供硅片數(shù)據(jù)的嵌入式存儲(chǔ)器供應(yīng)商進(jìn)行合作,具有極大的幫助作用。有了先進(jìn)的設(shè)計(jì)技術(shù),即使不需要額外的光罩和制程修正,亦可大幅地提高良率和可靠性。

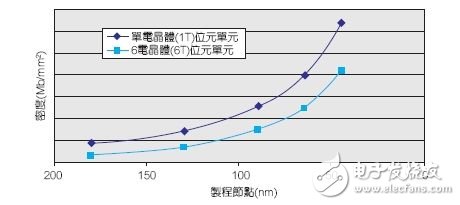

密度 在存儲(chǔ)器IP的選擇上一個(gè)重要的考慮因素是,能否為各制程節(jié)點(diǎn)選擇不同的存儲(chǔ)器密度。先進(jìn)的存儲(chǔ)器編譯器允許設(shè)計(jì)者在密度與速度之間進(jìn)行權(quán)衡,比如,是選擇高密度(HD)位單元還是選擇高電流位單元。

設(shè)計(jì)者還可借助靈活的列多工等功能,通過(guò)控制存儲(chǔ)器占用形狀(可變寬度、可變高度,或正方形),最佳化SoC布局規(guī)劃,進(jìn)而大幅地減少存儲(chǔ)器對(duì)晶片整體大小的影響。部份存儲(chǔ)器編譯器還支持sub-words(位和位元組可寫(xiě))、功率網(wǎng)格產(chǎn)生等功能,可大幅地最佳化功率輸出。此外,靈活的埠分配(一個(gè)埠用于讀或?qū)懀诙€(gè)埠用于讀和寫(xiě))亦可節(jié)省SRAM、CAM和暫存器文件的占用空間。

兩種嵌入式存儲(chǔ)器IP架構(gòu)的密度關(guān)系如圖4所示。與6電晶體(6T)位單元相較,位容量一定時(shí),單電晶體(1T)位單元最多可減少50%的晶片空間。在設(shè)計(jì)中,對(duì)速度要求較低而密度要求較高時(shí),1T 式架構(gòu)是較為理想的選擇。由于可采用批量CMOS制程,省卻了額外的光罩環(huán)節(jié),因而有益于成本壓縮。在高速應(yīng)用方面,設(shè)計(jì)者可采用6T甚至8T位單元來(lái)滿足其速度要求。

圖4:存儲(chǔ)器密度與不同嵌入式存儲(chǔ)器IP架構(gòu)的關(guān)系

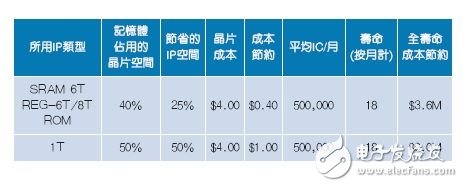

成本 對(duì)于SoC/ASIC來(lái)說(shuō),為了大幅壓縮成本,與次優(yōu)IP(常是免費(fèi)IP)相較,設(shè)計(jì)者更喜歡選擇‘節(jié)省空間’的IP參數(shù)。盡管有許多存儲(chǔ)器IP參數(shù)可供設(shè)計(jì)者免費(fèi)選用,但在產(chǎn)品的整體收益性上,卻并不見(jiàn)得是最經(jīng)濟(jì)的解決方案。在很多情況下,與‘免費(fèi)’存儲(chǔ)器IP相較,透過(guò)改善的嵌入式存儲(chǔ)器IP密度與性能來(lái)壓縮制造成本,效果更為顯著。

在產(chǎn)品的整個(gè)生命周期中,存儲(chǔ)器體積最佳化對(duì)量產(chǎn)成本的影響如表1所示。在表1中,存儲(chǔ)器IP占用的晶片空間以百分比表示。可透過(guò)晶片成本、量產(chǎn)效率以及產(chǎn)品壽命,計(jì)算高密度存儲(chǔ)器的成本壓縮效果。節(jié)省的IP空間根據(jù)圖4可看出,1T和6T 存儲(chǔ)器的密度增量比值約為2:1。

表1:高密度IP與成本節(jié)約

嵌入式存儲(chǔ)器IP選用指南

為了了解存儲(chǔ)器設(shè)計(jì)中的選擇要件,可針對(duì)具有最先進(jìn)功能的付費(fèi)嵌入式存儲(chǔ)器類(lèi)型加以歸納:

單埠(6T)和雙埠(8T)SRAM IP 由于這類(lèi)存儲(chǔ)器架構(gòu)大多適用于主流CMOS制造制程,無(wú)需額外的制程,因此基于傳統(tǒng)6T儲(chǔ)存單元的靜態(tài)RAM存儲(chǔ)器模組正成為ASIC/SoC制造中的主流。6T儲(chǔ)存單元采用經(jīng)驗(yàn)證適用于晶圓代工廠生產(chǎn)的高速、低功耗設(shè)計(jì)6T/8T位單元,是大規(guī)模編程或數(shù)據(jù)存儲(chǔ)器模組的理想元件。6T儲(chǔ)存單元適用于儲(chǔ)存能力從幾位元到幾兆位元的儲(chǔ)存陣列。

根據(jù)設(shè)計(jì)者采用針對(duì)高性能還是針對(duì)低功耗最佳化的CMOS制程,采用此種結(jié)構(gòu)的儲(chǔ)存陣列經(jīng)過(guò)設(shè)計(jì)后,可滿足多種不同的性能需求。經(jīng)高性能CMOS制程制造的SRAM,在功耗降低的同時(shí),可讓40nm和28nm等先進(jìn)制程節(jié)點(diǎn)的存取時(shí)間可降低到1ns以下。隨著制程節(jié)點(diǎn)的進(jìn)展,外形尺寸的微縮,采用傳統(tǒng)6T儲(chǔ)存單元建構(gòu)的靜態(tài)RAM單元尺寸更小,存取時(shí)也間更短。

SRAM存儲(chǔ)器單元的靜態(tài)特性使其可保留最小數(shù)目的支持電路,只需要對(duì)位址進(jìn)行解碼,并為解碼器、感測(cè)和計(jì)時(shí)電路的設(shè)計(jì)提供訊號(hào)即可。

單埠(6T)和雙埠(8T)暫存器IP 對(duì)于快速處理器緩沖存儲(chǔ)器和較小的存儲(chǔ)器緩沖(最高約每個(gè)巨集72Kbit)來(lái)說(shuō),這類(lèi)暫存器存儲(chǔ)器組合IP是個(gè)不錯(cuò)的選擇。暫存器同時(shí)具備占用空間最小、性能最快等特點(diǎn)。

單層可編程ROM IP 這種結(jié)構(gòu)功耗和速度均相對(duì)較低,特別適用于空間有限的儲(chǔ)存、固定數(shù)據(jù)的儲(chǔ)存或體積穩(wěn)步遞增的應(yīng)用程式儲(chǔ)存。這類(lèi)IP可支持多晶片組和不同長(zhǎng)寬比,既縮小了晶片體積,又獲得了最佳速度。為加速設(shè)計(jì)周期,部份IP還提供用以驅(qū)動(dòng)存儲(chǔ)器編譯器的編程腳本語(yǔ)言。

內(nèi)容尋址存儲(chǔ)器IP 由于速度更快、能耗更低,以及較執(zhí)行大量搜尋任務(wù)的應(yīng)用程式演算法占用晶片空間更小,這類(lèi)IP大多作為T(mén)CAM(三進(jìn)制)或BCAM(二進(jìn)制)IP,用于搜尋引擎類(lèi)應(yīng)用程式。在一般情況下,搜尋可在單一時(shí)脈周期內(nèi)完成。TCAM和BCAM常用于封包轉(zhuǎn)發(fā)、乙太網(wǎng)路位址過(guò)濾、路由查詢、韌體搜尋、主機(jī)ID搜尋、存儲(chǔ)器去耦合、目錄壓縮、封包分類(lèi)以及多工高速緩沖存儲(chǔ)器控制器等。

單電晶體SRAM 這種結(jié)構(gòu)雖然速度有所降低,但密度極高,適用于180nm、160nm、152nm、130nm、110nm、90nm以及65nm制程。尤其適用于需要大量晶片儲(chǔ)存空間、但不需要極高的存取速度的ASIC/SoC程式,以及空間有限且存儲(chǔ)器模組存在泄漏電流的設(shè)計(jì)。該結(jié)構(gòu)可產(chǎn)生與SRAM工作塬理相似的存儲(chǔ)器陣列,但其基礎(chǔ)為單電晶體/單電容器(1T)儲(chǔ)存單元(如動(dòng)態(tài)RAM所用)。

由于采用了6T儲(chǔ)存陣列,因此在相同的晶片空間上,單電晶體SRAM陣列的儲(chǔ)存能力更強(qiáng),但必須在系統(tǒng)控制器和邏輯層面了解存儲(chǔ)器的動(dòng)態(tài)特性,并在刷新控制方面發(fā)揮積極作用。在某些情況下,為了使其看起來(lái)像簡(jiǎn)單易用的SRAM陣列,也可能對(duì)DRAM及其自身控制器進(jìn)行整合。透過(guò)高密度1T巨集模組與某些提供刷新訊號(hào)的支持邏輯整合,可使存儲(chǔ)器單元的動(dòng)態(tài)特性透明化,設(shè)計(jì)者可在實(shí)施ASIC和SoC解決方案時(shí),將存儲(chǔ)器模組視為靜態(tài)RAM。

1T SRAM是一種可授權(quán)IP,能從晶圓代工廠獲得。但是,由于某些此類(lèi)IP需要額外光罩層(除標(biāo)準(zhǔn)CMOS層外),增加了晶圓成本,因而限制晶圓代工廠的可選制造空間。為了使額外的晶圓加工成本物有所值,晶片上采用的總DRAM陣列大小,通常必須大于50%的晶片空間。大部份可用DRAM巨集均為硬巨集單元,大小、長(zhǎng)寬比以及介面的可選空間有限。

有一種單電晶體SRAM的特殊變體,采用了可通過(guò)標(biāo)準(zhǔn)CMOS制程的架構(gòu),因此,它不但不必需修改光罩,也無(wú)需額外的制程步驟。此類(lèi)IP巨集模組具有更高的成本效益(制程成本可節(jié)省15-20%),而且可在任何晶圓廠進(jìn)行加工,也可出于成本或生產(chǎn)能力等塬因,改變制造廠。這種解決方案提供了多種尺寸、長(zhǎng)寬比和介面,可逐一指定相應(yīng)的存儲(chǔ)器編譯器。對(duì)于系統(tǒng)的其余部份來(lái)說(shuō),產(chǎn)生的存儲(chǔ)器模組介面看起來(lái)就像靜態(tài)RAM,但其密度(位元/單元空間)是基于6T儲(chǔ)存單元的存儲(chǔ)器陣列的2倍(經(jīng)過(guò)對(duì)作為空間運(yùn)算一部份的全部支持電路的平均)。對(duì)于大型存儲(chǔ)器陣列來(lái)說(shuō),支持電路所需的空間占百分比較小,存儲(chǔ)器模組的空間利用率也更高。

存儲(chǔ)器編譯器工具 嵌入式存儲(chǔ)器編譯器的職責(zé)在于因應(yīng)特定存儲(chǔ)器應(yīng)用程式的確切需求,量身定做基本的IP存儲(chǔ)器巨集單元。若適用範(fàn)圍足夠廣,編譯器可讓設(shè)計(jì)者選擇最優(yōu)架構(gòu),自動(dòng)產(chǎn)生存儲(chǔ)器陣列,并精確確定最佳化程式所需的速度、密度、功率、成本、可靠性與大小等因素。透過(guò)編譯器的自動(dòng)化作業(yè),可降低非經(jīng)常性工程成本,并可減少手動(dòng)陣列最佳化相關(guān)的潛在錯(cuò)誤。編譯器不但可使客戶的核心大小、介面以及長(zhǎng)寬比均達(dá)到最理想數(shù)值,而且還可幫助他們大幅地縮短上市時(shí)間。作為編譯制程的一部份,編譯器還可為設(shè)計(jì)者提供存儲(chǔ)器陣列的電氣、實(shí)體、模擬(Verilog)、BIST/DFT模型以及合成視圖。

表2:嵌入式存儲(chǔ)器IP的商業(yè)案例

結(jié)論

為新的ASIC/SOC選擇最佳嵌入式存儲(chǔ)器IP是設(shè)計(jì)決策的關(guān)鍵。設(shè)計(jì)者應(yīng)了解適用于其特定應(yīng)用程式的最佳存儲(chǔ)器特性及其所有關(guān)鍵參數(shù),所尋找的存儲(chǔ)器 IP應(yīng)具有足夠的適應(yīng)性,可滿足目標(biāo)SoC的各種需求。盡管有現(xiàn)成的免費(fèi)存儲(chǔ)器IP可供使用,但與可為特定應(yīng)用程式提供更好特性的付費(fèi)IP相較,它并不見(jiàn)得總能提供最佳解決方案。

經(jīng)過(guò)充分除錯(cuò)的存儲(chǔ)器IP具有體積小、泄漏功率低、動(dòng)態(tài)能耗低、速度快等特點(diǎn),可為設(shè)計(jì)者的解決方案進(jìn)一步最佳化,不但可在產(chǎn)品的整個(gè)壽命周期內(nèi),帶來(lái)上百萬(wàn)美元的營(yíng)收,同時(shí)也使其晶片在競(jìng)爭(zhēng)激烈的ASIC/SOC市場(chǎng)上,得到更好的差異化。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論