UltraRAM 是 UltraScale +? 系列中最新的存儲器模塊,能實現高達 500Mb 的總片上存儲容量,相當于賽靈思 28nm FPGA 片上存儲器容量的 6 倍。

傳統的 FPGA 和 SoC 包含的片上存儲器以 block RAM 和分布式 RAM 的形式存在。由于器件能以更高數據速率處理更多數據,因此越發需要將數據緩沖或存儲在靠近處理器的位置。

UltraScale+ 系列中的新產品是一款容量更大的稱為 UltraRAM 的靈活存儲器模塊。

UltraRAM 模塊可級聯在一起構成更大的片上存儲器。在設計中使用 UltraRAM 很簡單,因為賽靈思提供了所有必要工具,利用這些工具可以在設計中集成功能強大的最新模塊。

?

緩沖與存儲的需求增加

UltraScale+ ? FPGA 和 MPSoC 能夠傳輸和處理的數據比前一代器件多得多。最大的 Virtex?UltraScale+ FPGA(即 VU13P)包含 128 個數據速率高達 32.75Gb/s 的 GTY 收發器,以及超過 11,000個 工作頻率接近 900MHz 的 DSP Slice。這樣可得到 8.4Tb/s 串行帶寬和 21 TMAC/s 的信號處理速度,因此,片上存儲器也需要實現同樣的增長,以使系統能夠有效地緩沖處理前進入的數據和處理后流出的數據。

到達(進入)UltraScale ? FPGA 器件, block RAM 和分布式 RAM 可作為快速和高效的片上存儲器。為了成功處理數百兆位的數據,通常需要使用外部存儲器,例如 DDR4、DDR3 或 RLDRAM3。

UltraScale+ 系列產品則采用一種新的存儲方法。UltraRAM 是一種大容量、重量輕的存儲器模塊,使UltraScale+ 器件具備 500Mb 以上的高能效、低成本片上數據存儲器,相當于賽靈思 28nm FPGA 片上存儲器的 6 倍。

靈活的級聯功能使得 UltraRAM 模塊能夠采用多種配置——既可單獨使用,也可在器件中將所有模塊連接在一起使用。這使得用戶能夠構建大小適合應用需求的存儲器陣列,并省去一些 PCB 上的外部存儲器組件,例如 QDR SRAM。

UltraRAM 細節與特性

賽靈思很多代的 FPGA 和 SoC 都采用分列架構,將不同資源列并排布置在一起。列的數量和高度直接決定 FPGA 或 SoC 的尺寸和容量。

大多數 Kintex? UltraScale+ 和 Zynq? UltraScale+ 器件都包含一列 UltraRAM ;高端 Virtex UltraScale+FPGA 則包含多達 5 列 UltraRAM。UltraRAM 可在設計中作為單個 288Kb 存儲器,或者連接在一起構成更大的 RAM 陣列。相同列中的所有 UltraRAM 都可連接在一起,通過專用的級聯路由傳送地址、數據和控制信號。在 Kintex UltraScale+ 和 Zynq UltraScale+ 器件中,級聯得到的 RAM 陣列可高達36Mb,在 Virtex UltraScale+ 器件中可達到 22.5Mb。Virtex UltraScale+ 系列中,所有 UltraRAM 列都可通過光纖路由連接在一起,在最大器件中可構成容量達 360Mb 的存儲器陣列。

每個 UltraRAM 模塊都是一個雙端口同步 288Kb RAM,采用深度為 4,096、寬度為 72 位的固定配置。端口 A 和端口 B 共享相同時鐘信號。在外部時鐘的單個周期內,端口 A 操作總是在端口 B 操作之前完成。每個端口在每個時鐘周期都可獨立執行一個讀操作或一個寫操作。當兩個端口在相同時鐘周期內以相同地址(即地址沖突)執行寫操作時,端口 B 的寫操作有效,因為端口 A 上的寫操作被覆蓋。當端口 A 執行讀操作,而端口 B 以相同地址執行寫操作時,端口 A 獲得存儲器陣列中的舊數據,然后端口 B 上的新數據被寫到存儲器陣列。當端口 A 執行寫操作,端口 B 執行讀操作時,端口 A 上的新數據被寫入存儲器陣列,新數據也被讀到端口 B。對于每個端口,當執行寫操作時,該端口的讀輸出不變,保持之前的值。

每個 UltraRAM 存儲器陣列的內容都被每個端口上的漢明碼單誤差校正雙誤差檢測 (SECDED) ECC碼保護,以確保數據完整性。啟動 ECC 后,UltraRAM 提供 64 位寬的被保護數據字。UltraRAM 的SECDED ECC 代碼與 block RAM 的兼容。這樣可實現端到端數據保護方案,即在一個存儲器輸入端進行編碼的數據,在下游存儲器輸出端對其進行解碼之前,可在多個流水線級、存儲器類型和 / 或邏輯上保持受保護狀態。

UltraRAM 每兩個端口包含多達四個流水線級,并可針對 1-4 個時鐘周期的時延進行配置。當通過級聯UltraRAM 搭建較大的 RAM 陣列時,時延取決于所用 UltraRAM 的數量(即陣列的大小以及目標工作頻率)。

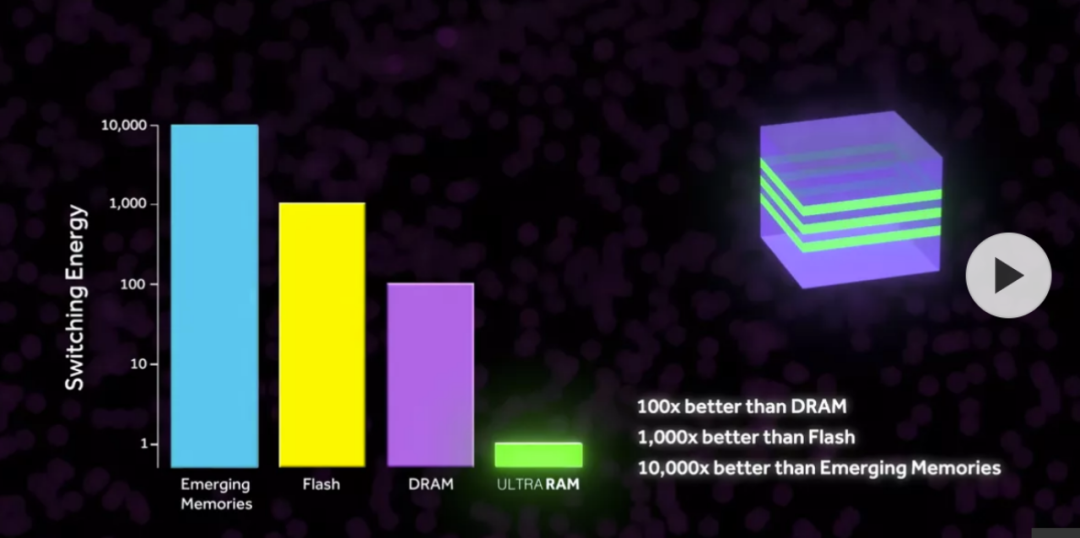

功耗降低

UltraRAM 提供各種內置功能以最大化功率效率,通常無需用戶干預。這些功能包括 :

? 將設計中不用的 UltraRAM 斷電

? 自動對不使用的流水線寄存器進行時鐘門控

? 當 UltraRAM 長時間不使用時,使其進入休眠模式

UltraRAM 可通過手動或自動進入休眠模式。用戶可以訪問 UltraRAM 的 SLEEP 端口。激活 SLEEP時,UltraRAM 從下個時鐘周期開始進入休眠模式。休眠模式下,UltraRAM SRAM 存儲器的外設邏輯斷電,但 SRAM 保持加電并保留其中的內容。

每個 UltraRAM 都包含相應的電路用來預測和識別接下來 N 個周期內模塊是否會被使用,如果不使用,那么在未使用時間足夠長之后,模塊會被送入休眠模式。這種自動休眠模式使用休眠端口,利用內置的控制邏輯來檢查將即將輸入的地址和使能信號的狀態。AUTO_SLEEP_LATENCY 屬性決定地址和使能信號需要比其他輸入信號提前多久到達。該信息用來確定是否有足夠的時間使單個 UltraRAM 進入休眠模式并在下個活動之前將其喚醒。

在設計中使用 UltraRAM

UltraScale+ 產品組合使用賽靈思的 Vivado?Design Suite。設計工具提供一系列代碼模板,可幫助用戶成功鎖定器件內的可用資源。有三種方法可以在 RTL 設計中使用 UltraRAM :編寫代碼以調用存儲器 ;實例化器件原語 ;使用最近添加的賽靈思參數化宏 (XPM)。大多數用戶都熟悉調用和實例化。VivadoDesign Suite 包含調用模板,所在位置 :

模板 → VHDL/Verilog → 綜合構建 → 編碼實例 → RAM

在 Vivado Design Suite v2016.1. 中,用戶必須指定 ramstyle=“ultra”才能明確指示 Vivado 綜合使用UltraRAM。

如果用戶需要對 UltraRAM 模塊的連接具有最終控制權,應使用以下位置的器件原語 :

模板 > VHDL/Verilog > 器件原語實例化 > Kintex/Virtex UltraScale+ > BLOCKRAM > URAM

盡管能讓用戶對單個組件的連接實現最嚴格的控制,但如果采用很多組件并有很多端口和信號,那么這種方法很快就會變得很費勁。

要在 RTL 設計中采用 UltraRAM,第三種方法是 XPM :

模板 → VHDL/Verilog → 賽靈思參數化宏 (XPM) → 存儲器 (XPM_MEMORY) → RAM

XPM 是一種用來根據用戶指定要求創建 RAM 和 ROM 結構的最新工具。用戶可在 XPM 代碼中指定多個類屬,包括存儲器大小、時鐘模式、ECC 模式等。這些要求隨后被 Vivado 綜合轉化為適當的存儲器陣列尺寸和風格。

在 Vivado Design Suite v2016.1 中,用戶必須在 MEMORY_PRIMITIVE 類屬上指定值 UltraRAM ,以明確指示 Vivado 綜合使用 UltraRAM。

創建存儲器陣列

UltraRAM 架構擴展性非常強,允許很多個 UltraRAM 模塊高效地連接在一起,以構成深邏輯存儲器,僅使用很少甚至無需架構資源,而且訪問時延相對較短。每個 UltraRAM 包含所有必要的邏輯,用以將相同列中相鄰 UltraRAM 模塊之間的全部輸入以及輸出接口進行完全級聯,并有選擇性地進行流水線化。此外,每個 UltraRAM 都包含每端口上的附加邏輯和控制輸入,以獨立確定 UltraRAM 模塊陣列中經過的讀或寫事務處理是否針對本地陣列,還是應該被忽略掉。這種分布式的決策邏輯能實現靈活而且低開銷的擴展性。

當設計中的指定存儲器陣列需要一個以上 UltraRAM 模塊時,必須決定如何將多個 UltraRAM 連接在一起。有兩個選擇分別是 :使用一個列中的所有 UltraRAM,或者使用多列陣列中的 UltraRAM。如果在一個列中構建 UltraRAM 陣列,那么用來級聯 UltraRAM 的所有必要路由都包含在該列中,使工具能夠充分利用所提供的專用資源。見圖 1。

圖 1 :在一個列中級聯的 UltraRAM

如果設計要求決定了多列陣列更加適合,例如,如果所需的陣列大于單個列的容量,那么需要創建多列陣列(見圖 2)。這種情況下,需要用一些架構資源將多個列連接在一起。最大可實現頻率以及多列陣列中的訪問時延取決于陣列尺寸、所用列的數量以及其他設計因素(例如 UltraRAM 列之間有多少架構資源被設計的其他部分使用)。

圖 2 :多列 UltraRAM 陣列

當創建 UltraRAM 陣列時,地址、控制和寫數據信號被提供至陣列的左下角,數據從陣列的右上角讀取。這樣能確保,通過對固定大小的陣列進行恰當流水線化后,從任何地址讀取任何數據所產生的時延總相同。

與每個 UltraRAM 自身可提供的 64 位 ECC 保護或 72 位非 ECC 保護字寬相比,寬數據或控制路徑設計需要更高的總線帶寬。這種情況下,可以并列使用多個相同的 UltraRAM 模塊實例或以上描述的級聯結構來構建非常高效的寬字數據存儲結構。

寄存器和流水線化

每個 UltraRAM 包含多個輸入和輸出寄存器,如圖 3 所示,其中有一些是可選的,取決于配置情況和所需的功能。

圖 3 :UltraRAM 寄存器

IREG、OREG 和 OREG_ECC 寄存器根據用戶所需的存儲器功能進行激活。此外,當把多個 UltraRAM級聯在一起時使用的寄存器為 :IREG_PRE 和 REG_CAS。

當把多個 UltraRAM 連接在一起時需要遵守一些規則,以保持最大工作頻率 :

? 單列陣列中的第一個實例或多列陣列每個列中的第一個實例都必須使用 IREG_PRE 寄存器。

? 如果設計中需要,OREG 和 / 或 OREG_ECC 寄存器應針對陣列中的所有 UltraRAM 一直啟用。

? 必須每經過四個 UltraRAM 模塊激活 REG_CAS 寄存器。

? 單列陣列中的最后一個實例或者多列陣列每列中的最后一個實例必須使用 REG_CAS 寄存器。

? 如果陣列垂直跨越多個時鐘區域,那么需要在時鐘區域邊界兩側提供附加流水線級。每個時鐘區域的每列上有 16 個 UltraRAM。

如需了解 UltraRAM 模塊的更多信息和詳細框圖,請參考 UG573《UltraScale 架構存儲器資源用戶指南》 的第二章。

遷移到 UltraRAM

用戶一定要知道所選目標器件中不同存儲器資源的數量。有些情況下,用戶最開始可以針對只有 blockRAM 的器件,但設計最終將會針對包含 UltraRAM 的器件。這種情況下,用戶需要了解 UltraRAM 的特性,并編寫代碼以利用 block RAM 和 UltraRAM 中的特性。這樣,工具就可使用目標器件中可使用的UltraRAM,而且,當改用不同器件時用戶不必重新設計。

表 1 給出了不同 UltraScale+ 系列中 UltraRAM 的數量。在 Virtex UltraScale+ 器件中,可將所有UltraRAM 連在一起,以構成容量高達 360Mb 的多列陣列 ;不過,也可實現更為常用的 10Mb-144Mb 范圍的多實例使用模型。

表 1 :UltraScale+ 產品組合中的 UltraRAM 資源

所有 UltraScale+ 器件還包含可實現較小存儲器的 block RAM 和分布式 RAM,從而在 VU13P 中實現總容量超過 500Mb 的片上存儲器。

DS890,《UltraScale 架構和產品簡介》給出了器件資源方面的更多詳情。

如果所選的器件中有 UltraRAM,應該將其用作 144Kb 或更大的存儲器。

替代外部存儲器組件

高達 360Mb 的 UltraRAM 幾乎可配置成無數種方式,因此會有很多種使用模式。常見的 UltraRAM 使用模式是如果不實現在外部存儲器(例如 QDR SRAM)中,可以將存儲器整合在 FPGA 或 MPSoC 中。片上存儲器的優勢在于可采用所需要的容量大小,而不是存儲器廠商提供的大小 ;而且存儲器在邏輯上非常接近設計中用來緩沖或存儲數據的位置。此外,為了與外部存儲器進行連接,數據必須通過存儲器接口或控制器,并且通過 FPGA/MPSoC 上的 I/O 引腳,而且外部存儲器組件會給系統增加很多功耗。通過以 UltraRAM 的方式在片上實現大容量存儲,這樣可消除 FPGA/MPSoC 的 I/O 以及外部存儲器的 I/O產生的功耗。

輸入多播

每個 UltraRAM 端口都可確定級聯模式中的事務處理是否屬于局部存儲器陣列。該功能可用來實現動態的事務處理級寫單播、多播和廣播存儲器結構。這種結構可以構成高效輸出緩沖存儲器開關的基礎。

有一個 UltraRAM 存儲器端口專門用來寫,另一個專門用來讀。所有 UltraRAM 模塊的寫端口都采用每模塊唯一的獨熱編碼 SELF_ADDR 和相配的獨冷編碼 SELF_MASK 值配置為連續級聯形式。每個寫事務處理都可以被送到單個、多個或所有 UltraRAM 模塊,方法是設置一個或多個相應的全局 / 高地址位,以匹配所有目標模塊的 SELF_ADDR 屬性的 logical-OR。所有 UltraRAM 模塊的讀端口都是非級聯的,能夠讓單個寫事務處理傳播到多個消費模塊。

每個 UltraRAM 模塊代表一個消費模塊的緩沖要求。要獲得更大的存儲容量,可將每個 UltraRAM 模塊改成 N 個 UltraRAM 模塊級聯成的消費模塊。

假設 C 個消費模塊從 C 個邏輯存儲器(每個深度為 N 個 UltraRAM 模塊)并行讀取,那么寫端口需要一個包含所有 C * N 個 UltraRAM 模塊的連續級聯,而讀端口需要 C 個 獨立的級聯,每個深度為 N 個UltraRAM。

圖 4 給出了這樣一種配置,其中每個消費模塊有四個輸出,每個輸出需要一個 UltraRAM 模塊作為緩沖,并有兩個樣本多播事務處理分別針對 UltraRAM 模塊 0 和 1 以及 1 和 3。

圖 4 :輸入多播

結論

每個設計都需要和使用這樣或那樣的存儲器。將大容量、靈活的 UltraRAM 模塊添加到 UltraScale+ 產品系列后,為用戶提供的片上存儲器容量比以往任何器件或競爭器件都要大。由于模塊可連接在一起構成不同大小的存儲器陣列,這樣用戶就能在設計中在需要的位置構建理想的存儲器解決方案,消除了使用外部 SRAM 組件所帶來的功耗和電路板復雜性。

電子發燒友App

電子發燒友App

評論