1. 背景 這篇文章主要介紹了DDR3IP核的寫實(shí)現(xiàn)。 2. 寫命令和數(shù)據(jù)總線介紹 DDR3 SDRAM控制器IP核主要預(yù)留了兩組總線,一組可以直接綁定到DDR3 SDRAM芯片端口,一組是留給

2020-12-31 11:17:02 5068

5068

本實(shí)驗(yàn)為后續(xù)使用DDR3內(nèi)存的實(shí)驗(yàn)做鋪墊,通過(guò)循環(huán)讀寫DDR3內(nèi)存,了解其工作原理和DDR3控制器的寫法,由于DDR3控制復(fù)雜,控制器的編寫難度高,這里筆者介紹采用第三方的DDR3 IP控制器情況下的應(yīng)用,是后續(xù)音頻、視頻等需要用到DDR3實(shí)驗(yàn)的基礎(chǔ)。

2021-02-05 13:27:00 8224

8224

2、512Mb-2Gb LP DDR2,以及?LP DDR4x、LP DDR3、LP DDR、SDRAM,適用于需配備4Gb 或以下容量DRAM 的應(yīng)用,?如人工智能加速器、物聯(lián)網(wǎng)、汽車、工業(yè)用、電信、

2022-04-20 16:04:03 2554

2554

DDR內(nèi)存1代已經(jīng)淡出市場(chǎng),直接學(xué)習(xí)DDR3 SDRAM感覺(jué)有點(diǎn)跳躍;如下是DDR1、DDR2以及DDR3之間的對(duì)比。

2023-04-04 17:08:47 2871

2871

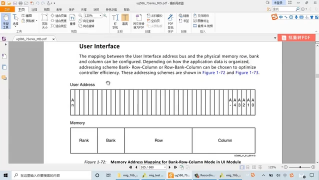

的SDRAMs其結(jié)果如圖6所說(shuō),63位,N=3。圖6 地址映射例子2.5. DDR3內(nèi)存控制器接口為了使得數(shù)據(jù)能夠有效的將數(shù)據(jù)源從DSP搬運(yùn)外部DDR3 SDRAM中,DDR3內(nèi)存控制器使用了一個(gè)命令

2018-01-18 22:04:33

嗨,我是FPGA領(lǐng)域的新手。現(xiàn)在我正在使用Genesys2。我必須控制DDR3內(nèi)存。我在Digilent網(wǎng)站上找到了一些使用micrlaze處理器的DDR3示例。但是,在我的情況下,我不必

2019-05-05 15:29:38

為了實(shí)現(xiàn)更強(qiáng)大的系統(tǒng)操作,DDR3 SDRAM驅(qū)動(dòng)器設(shè)計(jì)通過(guò)降低電容得到了增強(qiáng),動(dòng)態(tài)片上端接(ODT)和新的校準(zhǔn)方案。電容減少來(lái)自于使用新的合并驅(qū)動(dòng)器。使用新驅(qū)動(dòng)程序,組成輸出驅(qū)動(dòng)程序的電路共享用于ODT。DDR2上使用單獨(dú)的結(jié)構(gòu)作為輸出驅(qū)動(dòng)器和終端阻抗。

2019-05-23 08:20:56

我們知道DDR3內(nèi)存條,通常有個(gè)速率DDR3-800,DDR3-1066,DDR3-1333等,這個(gè)說(shuō)明他們的最高工作頻率不能超過(guò)400MHz,533MHz。。。但還有一個(gè)最低工作頻率要求,請(qǐng)問(wèn)在DDR3內(nèi)存條顆粒是那個(gè)指標(biāo)?為什么有這個(gè)要求?

2012-10-23 22:52:34

和安全性大大提高。 2 DDR3介紹 DDR3內(nèi)存與DDR2內(nèi)存相似包含控制器和存儲(chǔ)器2個(gè)部分,都采用源同步時(shí)序,即選通信號(hào)(時(shí)鐘)不是獨(dú)立的時(shí)鐘源發(fā)送,而是由驅(qū)動(dòng)芯片發(fā)送。它比 DR2有更高

2014-12-15 14:17:46

通過(guò)DDR3內(nèi)存名MT41J128M16-16Meg*16*8Banks通過(guò)命名怎樣算出內(nèi)存的大小?

2017-06-15 21:19:11

HI,我的FPGA是Kintex-7的XC7K410T-2FFG900。我的DDR3是2Gb,由128Mb * 16組成。 DDR3數(shù)據(jù)速率為1600Mbps,因此我必須在HP BANK中使用VRN

2020-07-21 14:47:06

DDR3(double-data-rate three synchronous dynamic random accessmemory)是應(yīng)用在計(jì)算機(jī)及電子產(chǎn)品領(lǐng)域的一種高帶寬并行數(shù)據(jù)總線。DDR3 在 DDR2

2019-05-22 08:36:26

為任意或所有DDR3 SDRAM器件提供單獨(dú)的終端阻抗控制,提高了存儲(chǔ)器通道的信號(hào)完整性。圖2:DDR3存儲(chǔ)器控制器IP核框圖DDR3存儲(chǔ)器控制器應(yīng)支持廣泛的存儲(chǔ)器速率和配置,以滿足各種應(yīng)用需求。例如

2019-05-24 05:00:34

DDR3存儲(chǔ)器接口控制器是什么?有什么優(yōu)勢(shì)?

2021-04-30 06:57:16

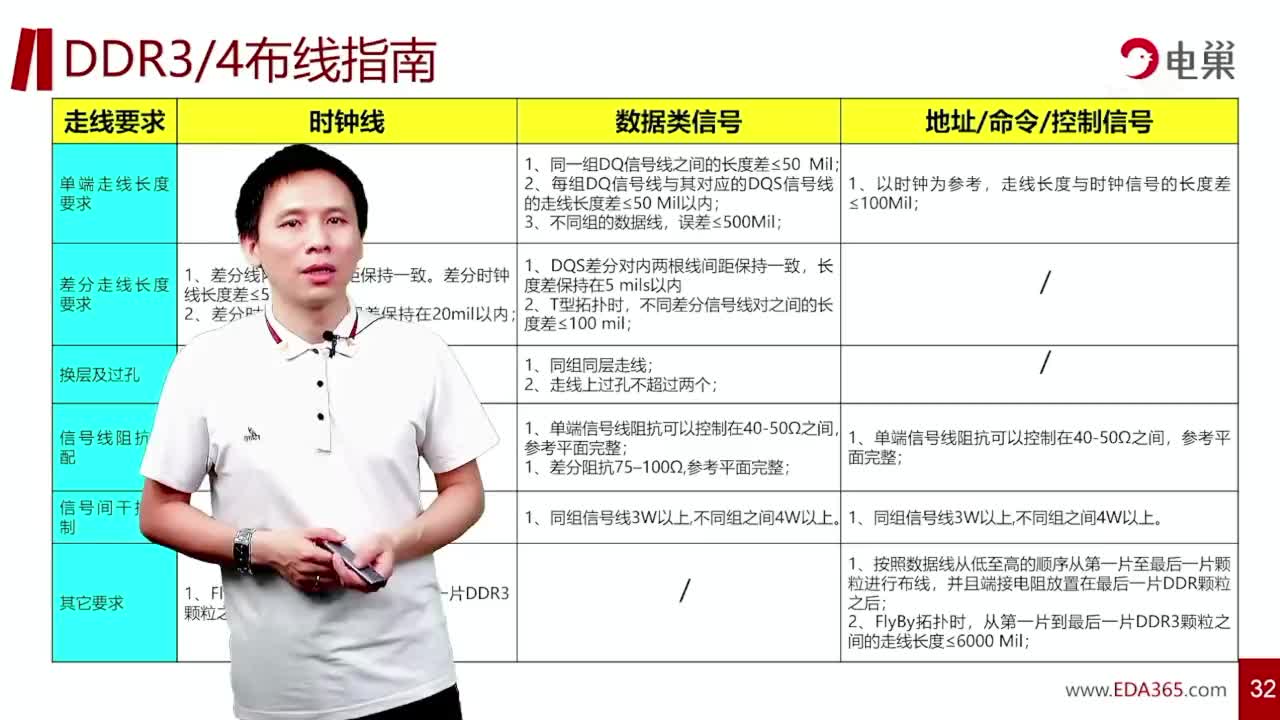

共享交流一下,DDR3布線技巧

2016-01-08 08:17:53

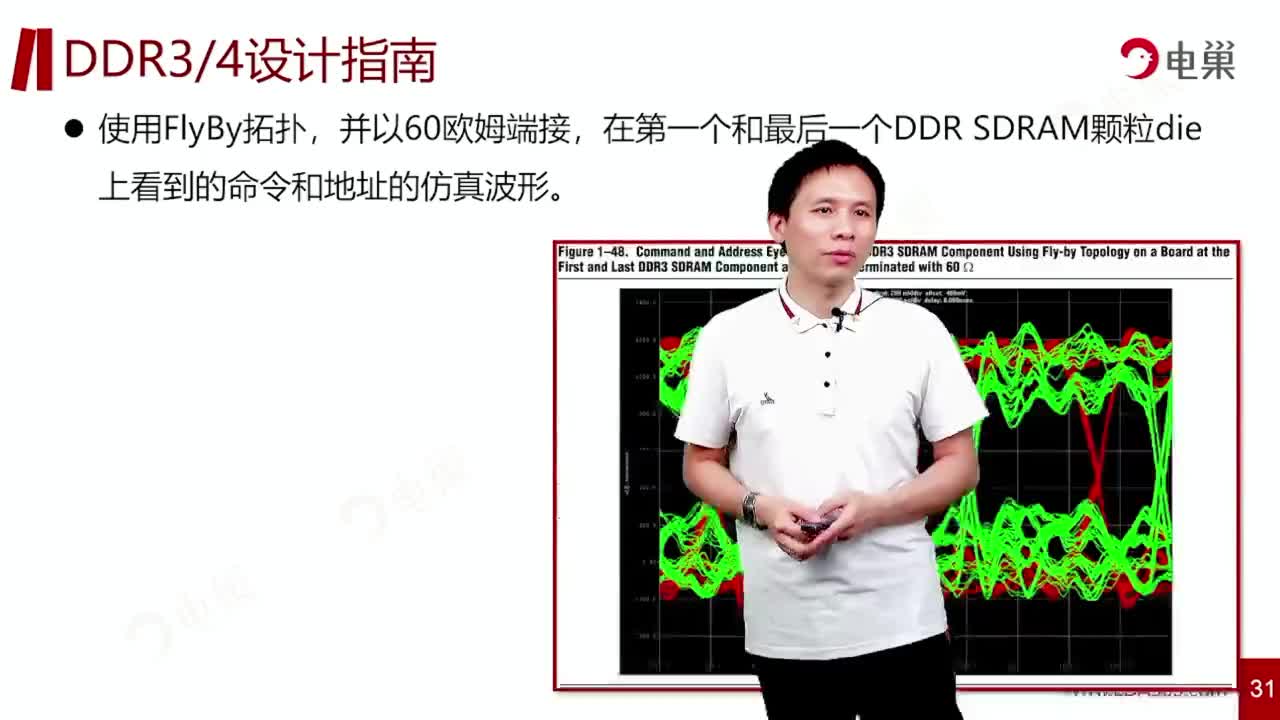

這篇帖子跟大家一起來(lái)討論下DDR3布線的那些事:DDR3的設(shè)計(jì)有著嚴(yán)格等長(zhǎng)要求,歸結(jié)起來(lái)分為兩類(以64位的DDR3為例): 數(shù)據(jù) (DQ,DQS,DQM):組內(nèi)等長(zhǎng),誤差控制在20MIL以內(nèi),組間

2016-10-28 10:25:21

CPU的DDR3總線只連了一片DDR3,也沒(méi)有復(fù)用總線將DDR3的CS直接拉到地的話,DDR3初始化不成功所以說(shuō)DDR3的CS信號(hào)是通過(guò)沿采樣的嗎,電平采樣不行?無(wú)法理解啊還是有其他方面原因

2016-11-25 09:41:36

DDR3芯片讀寫控制及調(diào)試總結(jié),1. 器件選型及原理圖設(shè)計(jì)(1) 由于是直接購(gòu)買現(xiàn)成的開(kāi)發(fā)板作為項(xiàng)目前期開(kāi)發(fā)調(diào)試使用,故DDR3芯片已板載,其型號(hào)為MT41J256M16HA-125,美光公司生產(chǎn)的4Gb容量DDR3芯片。采...

2021-07-22 08:33:54

本帖最后由 一只耳朵怪 于 2018-6-21 15:24 編輯

各位好!關(guān)于DDR3,之前有小結(jié)過(guò)如果進(jìn)行DDR3的SW leveling和進(jìn)行EMIF4寄存器的配置。但是調(diào)試時(shí),如果進(jìn)行DDR3的問(wèn)題定位,現(xiàn)小結(jié)一下,附上相關(guān)文檔。如有相關(guān)問(wèn)題,可在樓下跟帖討論。謝謝!

2018-06-21 04:01:01

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之處?

2021-03-12 06:22:08

在使用DDR3 SDRAM Controller with Uniphy ip(quartus prime 17.1 )核時(shí)卡在如下情況,無(wú)法生成(持續(xù)一晚上), 且軟件沒(méi)有報(bào)錯(cuò)誤及其它提示。再換用

2018-05-14 19:29:26

(flight-time skew)來(lái)降低共同切換噪聲(SSN)。走線擺率可以達(dá)到0.8tCK,這個(gè)寬度導(dǎo)致無(wú)法確定在哪兩個(gè)時(shí)鐘周期獲取數(shù)據(jù),因此,JEDEC為DDR3定義了校準(zhǔn)功能,它可以使控制器

2019-04-22 07:00:08

DDR3的理論帶寬怎么計(jì)算?用xilinx的控制器輸入時(shí)鐘200M。fpga與DDR的接口如下:

2016-02-17 18:17:40

=1.5V;但我看了一篇FPGA的DDR3 IP核例化文章,上面寫FPGA的BANK1,3連接外部存儲(chǔ)控制器(如下圖,且只有四個(gè)BANK),所以要將DDR3連接在BANK3上。所以DDR3如何與FPGA芯片

2021-11-29 16:10:48

如果沒(méi)有將均衡功能直接設(shè)計(jì)到FPGA I/O架構(gòu)中,那么任何設(shè)備連接到DDR3 SDRAM DIMM都將是復(fù)雜的,而且成本還高,需要大量的外部元器件,包括延時(shí)線和相關(guān)的控制。

2019-08-21 07:21:29

本次發(fā)布 Gowin DDR3參考設(shè)計(jì)。Gowin DDR3 參考設(shè)計(jì)可在高云官網(wǎng)下載,參考設(shè)計(jì)可用于仿真,實(shí)例化加插用戶設(shè)計(jì)后的總綜合,總布局布線。

2022-10-08 08:00:34

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3資料。

2016-05-27 16:39:58

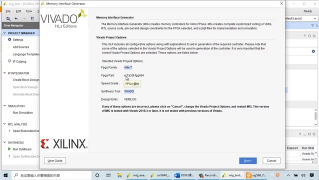

”。13.點(diǎn)擊“Generate”生成MIG控制器。四、生成文檔點(diǎn)擊“Generate”,生成MIG控制器相關(guān)的設(shè)計(jì)文檔。以上就是基于Xilinx 的K7 DDR3 IP核的生成配置過(guò)程。

2019-12-19 14:36:01

DDR3的IP核配置完畢后,產(chǎn)生了好多文件,請(qǐng)問(wèn)如何調(diào)用這些文件實(shí)現(xiàn)DDR3的讀寫呢?看了一些文章,說(shuō)是要等到local_init_done為高電平后,才能進(jìn)行讀寫操作。請(qǐng)問(wèn)DDR3的控制命令如

2016-01-14 18:15:19

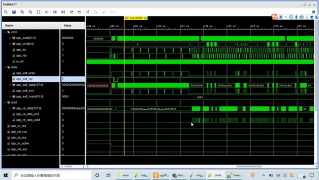

看完保證你會(huì)做DDR3的仿真

2015-09-18 14:33:11

SDRAM 相連的是BANK35 的 IO,DDR3 的硬件設(shè)計(jì)需要嚴(yán)格考慮信號(hào)完整性,我們?cè)陔娐吩O(shè)計(jì)和 PCB設(shè)計(jì)的時(shí)候已經(jīng)充分考慮了匹配電阻/終端電阻,走線阻抗控制,走線等長(zhǎng)控制,保證DDR3 高速

2021-07-30 11:23:45

你好。我最近第一次對(duì)待Vivado。我想使用DDR3內(nèi)存和IDELAYE2。該設(shè)備是Kintex-7。當(dāng)我一起使用DDR3控制器和IDELAYE2時(shí)發(fā)生錯(cuò)誤,并且無(wú)法形成位文件。當(dāng)我丟失

2020-08-20 09:40:23

& 14用于DDR3內(nèi)存接口,但由于我使用的是3.3V的fash存儲(chǔ)器IC,我必須使用bank 14進(jìn)行閃存存儲(chǔ)器接口。原因是需要的資源僅在Bank 14中可用.DDR3存儲(chǔ)器連接的bank應(yīng)該工作在

2020-04-17 07:54:29

的。DDR3控制器調(diào)用Write leveling功能時(shí),需要DDR3 SDRAM顆粒的反饋來(lái)調(diào)整DQS與CK之間的相位關(guān)系,具體方式如下圖一所示。Write leveling 是一個(gè)完全自動(dòng)的過(guò)程。控制器

2022-12-16 17:01:46

、DDR2與DDR3內(nèi)存的特性區(qū)別: 1、邏輯Bank數(shù)量 DDR2 SDRAM中有4Bank和8Bank的設(shè)計(jì),目的就是為了應(yīng)對(duì)未來(lái)大容量芯片的需求。而DDR3很可能將從2Gb容量起步,因此起始

2011-12-13 11:29:47

大家好!

我剛剛買了TMDSEVM6678L開(kāi)發(fā)套件,這款套件應(yīng)該有512MB的DDR3 SDRAM,從圖上看,有5塊芯片組成這512MB的DDR3,但是我的板子上DDR3部分只有4塊芯片,請(qǐng)教一下各位是我的板子少了一塊芯片還是這4塊芯片容量比5塊的要大,所以總量還是512MB呢?

謝謝!

2018-06-24 05:29:03

為任意或所有DDR3 SDRAM器件提供單獨(dú)的終端阻抗控制,提高了存儲(chǔ)器通道的信號(hào)完整性。圖2:DDR3存儲(chǔ)器控制器IP核框圖DDR3存儲(chǔ)器控制器應(yīng)支持廣泛的存儲(chǔ)器速率和配置,以滿足各種應(yīng)用需求。例如

2019-05-27 05:00:02

進(jìn)行了DDR3 SDRAM控制器的編寫,分析并提出了提高帶寬利用率的方法。最終將其進(jìn)行類FIFO接口的封裝,屏蔽掉了DDR3 IP核復(fù)雜的用戶接口,為DDR3數(shù)據(jù)流緩存的實(shí)現(xiàn)提供便利。系統(tǒng)測(cè)試表明,該

2018-08-02 09:34:58

優(yōu)仲裁模塊、讀寫邏輯控制模塊和DDR3存儲(chǔ)器控制模塊。DDR3存儲(chǔ)控制器模塊采用Xilinx公司的MIG核,用戶只需要通過(guò)IP核的GUI選擇內(nèi)存芯片并進(jìn)行相關(guān)參數(shù)設(shè)置,即可完成DDR3的配置工作[6

2018-08-02 09:32:45

作者:吳連慧,周建江,夏偉杰摘要:為了解決視頻圖形顯示系統(tǒng)中多個(gè)端口訪問(wèn)DDR3的數(shù)據(jù)存儲(chǔ)沖突,設(shè)計(jì)并實(shí)現(xiàn)了基于FPGA的DDR3存儲(chǔ)管理系統(tǒng)。DDR3存儲(chǔ)器控制模塊使用MIG生成DDR3控制器

2018-08-02 11:23:24

12位,擴(kuò)展成16位后進(jìn)行存儲(chǔ),DDR3內(nèi)部以1067M處理速度,32位的處理帶寬進(jìn)行存儲(chǔ),寫數(shù)據(jù)時(shí)從地址全0寫到地址全1,讀數(shù)據(jù)時(shí)也從地址全0讀到全1,經(jīng)對(duì)比無(wú)誤,說(shuō)明該控制器能夠較好地進(jìn)行高速讀寫操作。`

2018-08-30 09:59:01

。 本手冊(cè)以一個(gè)經(jīng)過(guò)驗(yàn)證的可穩(wěn)定工作的設(shè)計(jì)為例,來(lái)系統(tǒng)介紹高云FPGA連接DDR3的硬件設(shè)計(jì)方法,F(xiàn)PGA芯片型號(hào)采用GW2A-LV18PG256,存儲(chǔ)芯片采用鎂光(Micron)公司生產(chǎn)的單晶粒封裝

2022-09-29 06:15:25

DDR3存儲(chǔ)器控制器面臨的挑戰(zhàn)有哪些?如何用一個(gè)特定的FPGA系列LatticeECP3實(shí)現(xiàn)DDR3存儲(chǔ)器控制器。

2021-04-30 07:26:55

均衡的定義和重要性是什么如何實(shí)現(xiàn)FPGA和DDR3 SDRAM DIMM條的接口設(shè)計(jì)?

2021-05-07 06:21:53

現(xiàn)在因?yàn)轫?xiàng)目需要,要用DDR3來(lái)實(shí)現(xiàn)一個(gè)4入4出的vedio frame buffer。因?yàn)槠邮褂玫氖莑attice的,參考設(shè)計(jì)什么的非常少。需要自己調(diào)用DDR3控制器來(lái)實(shí)現(xiàn)這個(gè)vedio

2015-08-27 14:47:57

的工作時(shí)鐘頻率。然而,設(shè)計(jì)至DDR3的接口也變得更具挑戰(zhàn)性。在FPGA中實(shí)現(xiàn)高速、高效率的DDR3控制器是一項(xiàng)艱巨的任務(wù)。直到最近,只有少數(shù)高端(昂貴)的FPGA有支持與高速的DDR3存儲(chǔ)器可靠接口的塊

2019-08-09 07:42:01

大家好,我試圖通過(guò)vivado v14.3生成DDR3控制器。我正在選擇DDR3 SODIMM模塊“MT8KSF1G72HZ-1G6”。該工具支持該器件,最高頻率可達(dá)666.66MHz,但該模塊的數(shù)據(jù)表明最高頻率可達(dá)800MHz。請(qǐng)幫我確定問(wèn)題所在。感謝致敬Tarang JIndal

2020-07-31 06:07:43

你好我們計(jì)劃使用XC7Z020 PS部分的DDR3內(nèi)置控制器將其連接到2個(gè)芯片[MT41K128M16] -32位數(shù)據(jù)寬度。我們計(jì)劃再使用一個(gè)DDR3組件來(lái)支持ECC。請(qǐng)告知我們XC7Z020 PS中DDR3控制器引腳的詳細(xì)信息,包括ECC引腳詳細(xì)信息。謝謝Pench

2020-03-24 09:34:32

怎樣對(duì)DDR3芯片進(jìn)行讀寫控制呢?如何對(duì)DDR3芯片進(jìn)行調(diào)試?

2021-08-12 06:26:33

目前有一個(gè)項(xiàng)目需要使用DDR3作為顯示緩存,VGA作為顯示器,F(xiàn)PGA作為主控器,來(lái)刷圖片到VGA上。VGA部分已經(jīng)完成,唯獨(dú)這個(gè)DDR3以前沒(méi)有使用過(guò),時(shí)序又比較復(fù)雜,所以短時(shí)間內(nèi)難以完成,希望做過(guò)DDR3控制器的大神指點(diǎn)一二。急求!!!!

2015-11-16 09:18:59

DDR,DDR2,DDR3,DDR4,LPDDR區(qū)別文所有權(quán)歸作者Aircity所有1什么是DDRDDR是Double Data Rate的縮寫,即“雙比特翻轉(zhuǎn)”。DDR是一種技術(shù),中國(guó)大陸工程師

2021-09-14 09:04:30

數(shù)據(jù)速率 800Mbps

一、實(shí)驗(yàn)要求

生成 DDR3 IP 官方例程,實(shí)現(xiàn) DDR3 的讀寫控制,了解其工作原理和用戶接口。

二、DDR3 控制器簡(jiǎn)介

GL50H 為用戶提供一套完整的 DDR

2023-05-19 14:28:45

請(qǐng)問(wèn)AD9361正常工作需要DDR3嗎,需要外部存儲(chǔ)器嗎?

2018-10-26 09:29:50

本帖最后由 一只耳朵怪 于 2018-6-20 11:34 編輯

各位專家好!剛剛學(xué)習(xí)DSP,還沒(méi)有入門。實(shí)驗(yàn)室購(gòu)買了TMS320C6678開(kāi)發(fā)板。請(qǐng)問(wèn):1、為什么DSP需要外接DDR3?2

2018-06-20 00:40:57

我需要在V7中實(shí)現(xiàn)與DDR3 SDRAM相同的功能和接口。這意味著命令/地址,讀取數(shù)據(jù)和寫入數(shù)據(jù)流的方向與MIG的方向不同。這可以實(shí)現(xiàn)嗎?

2020-07-14 16:18:04

本文介紹了DDR3 SDRAM 的基本特點(diǎn)和主要操作時(shí)序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設(shè)計(jì)方法。詳述了控制器基本結(jié)構(gòu)和設(shè)計(jì)思想,分析了各模塊功能與設(shè)計(jì)注意事項(xiàng),并

2010-07-30 17:13:55 30

30 不只計(jì)算機(jī)存儲(chǔ)器系統(tǒng)一直需要更大、更快、功率更低、物理尺寸更小的存儲(chǔ)器,嵌入式系統(tǒng)應(yīng)用也有類似的要求。本應(yīng)用指南介紹了邏輯分析儀在檢驗(yàn)DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 79

79 基于協(xié)議控制器的DDR3訪存控制器的設(shè)計(jì)及優(yōu)化_陳勝剛

2017-01-07 19:00:39 15

15 雖然新一代電腦/智能手機(jī)用上了DDR4內(nèi)存,但以往的產(chǎn)品大多還是用的DDR3內(nèi)存,因此DDR3依舊是主流,DDR4今后將逐漸取代DDR3,成為新的主流,下面我們?cè)賮?lái)看看DDR4和DDR3內(nèi)存都有哪些區(qū)別。相比上一代DDR3,新一代DDR4內(nèi)存主要有以下幾項(xiàng)核心改變:

2017-11-08 15:42:23 30895

30895 為解決超高速采集系統(tǒng)中的數(shù)據(jù)緩存問(wèn)題,文中基于Xilinx Kintex-7 FPGA MIG_v1.9 IP核進(jìn)行了DDR3 SDRAM控制器的編寫,分析并提出了提高帶寬利用率的方法。最終將其進(jìn)行

2017-11-16 14:36:41 19504

19504

DDR3 SDRAM(Double Data Rate Three SDRAM):為雙信道三次同步動(dòng)態(tài)隨機(jī)存取內(nèi)存。

DDR4 SDRAM(Double Data Rate Fourth

2017-11-17 13:15:49 25152

25152 為了滿足高速圖像數(shù)據(jù)采集系統(tǒng)中對(duì)高帶寬和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的設(shè)計(jì)方法,提出了一種基于Verilog-HDL 語(yǔ)言的DDR3 SDRAM

2017-11-17 14:14:02 3290

3290

DDR3內(nèi)存與DDR2內(nèi)存相似包含控制器和存儲(chǔ)器2個(gè)部分,都采用源同步時(shí)序,即選通信號(hào)(時(shí)鐘)不是獨(dú)立的時(shí)鐘源發(fā)送,而是由驅(qū)動(dòng)芯片發(fā)送。它比DR2有更高的數(shù)據(jù)傳輸率,最高可達(dá)1866Mbps;DDR3還采用8位預(yù)取技術(shù),明顯提高了存儲(chǔ)帶寬;其工作電壓為1.5V,保證相同頻率下功耗更低。

2019-06-25 15:49:23 1736

1736 DDR3 SDRAM是DDR3的全稱,它針對(duì)Intel新型芯片的一代內(nèi)存技術(shù)(但目前主要用于顯卡內(nèi)存),頻率在800M以上。DDR3是在DDR2基礎(chǔ)上采用的新型設(shè)計(jì),與DDR2 SDRAM相比具有功耗和發(fā)熱量較小、工作頻率更高、降低顯卡整體成本、通用性好的優(yōu)勢(shì)。

2019-10-29 08:00:00 0

0 學(xué)完SDRAM控制器后,可以感受到SDRAM的控制器的書寫是十分麻煩的,因此在xilinx一些FPGA芯片內(nèi)已經(jīng)集成了相應(yīng)的IP核來(lái)控制這些SDRAM,所以熟悉此類IP核的調(diào)取和使用是非常必要的。下面我們以A7的DDR3 IP核作為例子進(jìn)行IP核調(diào)取。

2019-11-10 10:28:45 4702

4702

本文檔的主要內(nèi)容詳細(xì)介紹的是DDR和DDR2與DDR3的設(shè)計(jì)資料總結(jié)包括了:一、DDR的布線分析與設(shè)計(jì),二、DDR電路的信號(hào)完整性,三、DDR Layout Guide,四、DDR設(shè)計(jì)建議,六、DDR design checklist,七、DDR信號(hào)完整性

2020-05-29 08:00:00 0

0 從成本的角度來(lái)看,DDR3也許的確要比DDR4低一些,所以從這個(gè)角度可以講通。

2020-09-08 16:28:23 4062

4062 POD模式;? 增加ACT_n控制指令為增強(qiáng)數(shù)據(jù)讀寫可靠性增加的變更點(diǎn)主要有:? DBI;? Error Detection;1 電源變化DDR3與DDR4的96 Ball封裝pin定義...

2021-11-06 20:36:00 28

28 ,以及對(duì)應(yīng)的波形圖和 Verilog HDL 實(shí)現(xiàn)。我們調(diào)取的 DDR3 SDRAM 控制器給用戶端預(yù)留了接口,我們可以通過(guò)這些預(yù)留的接口總線實(shí)現(xiàn)對(duì)該 IP 核的控制,本章節(jié)將會(huì)講解如何根據(jù) Xilinx 官方提供的技術(shù)參數(shù)來(lái)實(shí)現(xiàn)對(duì) IP 核的寫控制。寫命令和寫數(shù)據(jù)總線介紹DDR3 SDRAM控制器I

2021-12-04 19:21:05 4

4 一、DDR3簡(jiǎn)介 ? ? ? ? DDR3全稱double-data-rate 3 synchronous dynamic RAM,即第三代雙倍速率同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器。所謂同步,是指DDR3數(shù)據(jù)

2022-12-21 18:30:05 1915

1915 DDR3 SDRAM使用雙倍數(shù)據(jù)速率架構(gòu)來(lái)實(shí)現(xiàn)高速操作。雙倍數(shù)據(jù)速率結(jié)構(gòu)是一種8n預(yù)取架構(gòu),其接口經(jīng)過(guò)設(shè)計(jì),可在I/O引腳上每個(gè)時(shí)鐘周期傳輸兩個(gè)數(shù)據(jù)字。

DDR3 SDRAM的單個(gè)讀或?qū)懖僮饔行У匕?/div>

2023-02-06 10:12:00 3

3 本文介紹一個(gè)FPGA開(kāi)源項(xiàng)目:DDR3讀寫。該工程基于MIG控制器IP核對(duì)FPGA DDR3實(shí)現(xiàn)讀寫操作。

2023-09-01 16:23:19 743

743

DDR3是2007年推出的,預(yù)計(jì)2022年DDR3的市場(chǎng)份額將降至8%或以下。但原理都是一樣的,DDR3的讀寫分離作為DDR最基本也是最常用的部分,本文主要闡述DDR3讀寫分離的方法。

2023-10-18 16:03:56 518

518

是目前使用最為廣泛的計(jì)算機(jī)內(nèi)存標(biāo)準(zhǔn),它已經(jīng)服務(wù)了計(jì)算機(jī)用戶多年。但是,DDR4內(nèi)存隨著技術(shù)的進(jìn)步,成為了更好的內(nèi)存選擇。本文將詳細(xì)介紹DDR4和DDR3內(nèi)存的各種區(qū)別。 1. 工作頻率 DDR3內(nèi)存的標(biāo)準(zhǔn)工作頻率為1600MHz,而DDR4內(nèi)存標(biāo)準(zhǔn)則為2133MHz。這意味著DDR4內(nèi)存的傳輸速度

2023-10-30 09:22:00 3905

3905 電子發(fā)燒友網(wǎng)站提供《完整的DDR、DDR2和DDR3內(nèi)存電源解決方案同步降壓控制器數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-03-13 10:16:45 0

0 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論