OFweek垂直分層閘流體(Vertical Layered Thyristor;VLT),是Kilopass研發出的新型內存單元,能夠顯著降低動態隨機存取內存(DRAM)的成本和復雜性。這是一種靜態的內存單元,無需刷新操作;兼容于現有晶圓廠的制造設備,也無需任何新的材料或工藝。

相較于一般的DRAM,VLT內存數組能節約高達45%的成本;這是因為它具有更小的VLT內存單元,以及驅動更長行與列的能力,使其得以大幅提升內存數組效率。然而,想要發揮VLT的優勢,就必須在依據產業標準發展的成熟DRAM市場展開設計與制造,才能確保兼容于不同供應商的內存產品。

目前,基于VLT技術的內存已經具備與現有“第四代低功耗雙倍數據速率”(LPDDR4)規格完全兼容的能力。VLT內存組(bank)可以模擬傳統DRAM的bank,并兼容于其頻率;在設計VLT電路時,設計者可以選擇連接標準DDR控制器,或是成本較低的簡化版控制器。如果使用標準控制器,由于不需要刷新,VLT內存將會忽略刷新序列。系統的其他部份則會將VLT DRAM視為通用DRAM,因而無需任何改變。

傳統DRAM內存單元

為了顯示如何使用VLT內存單元構造LPDDR4內存,首先回顧一下傳統DRAM以及LPDDR4的工作方式。熟悉DRAM者或許對其有所了解,但實際運用上還是有些微差異,在此先定義一些準則與術語以便于理解。

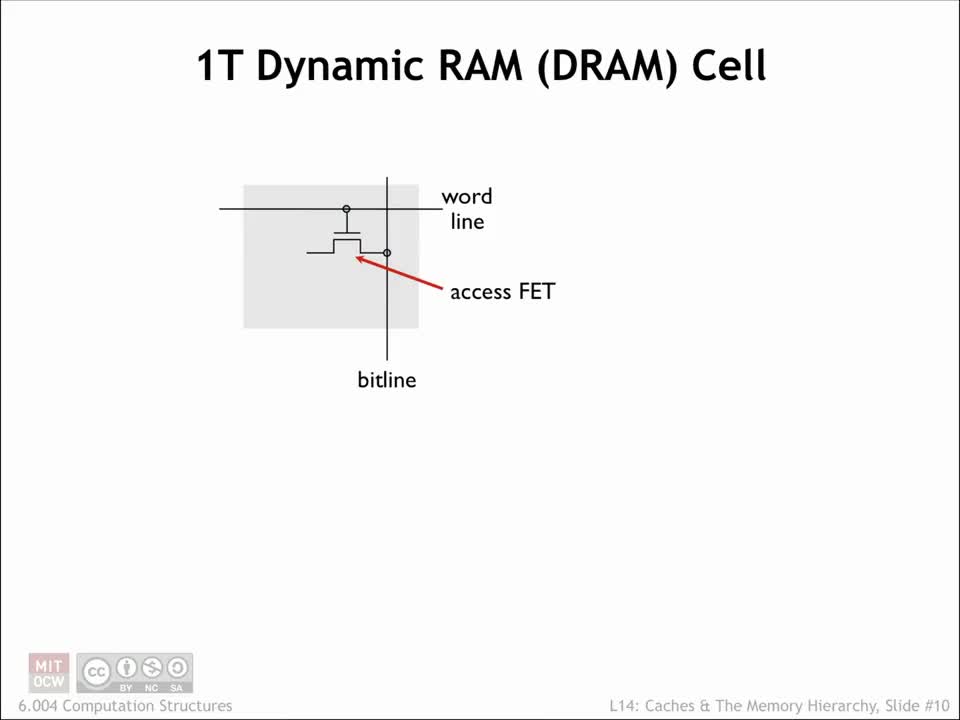

DRAM作業的許多方面取決于其電容儲存單元。首先,電容的漏電特性導致了刷新的必要性;其次,儲存單元的基本作業方式之一是讀取,它會影響如何組織內存的其他方面。

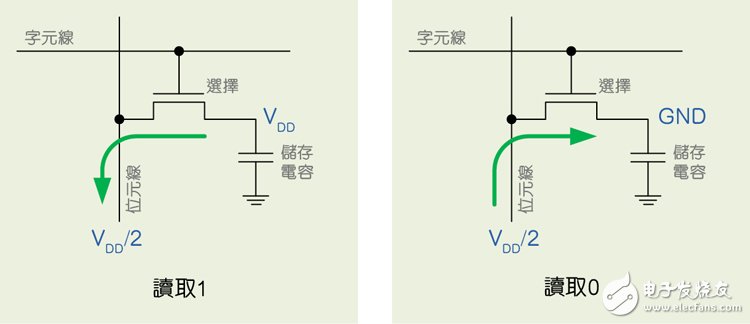

圖1顯示電容儲存單元的原理圖,左右圖分別代表了讀取1和讀取0時。電路透過“電荷分配”(charge sharing)偵測內存位值。位線(bitline)首先被預充電到一個在0和1之間的電壓值,然后透過打開讀數晶體管來選擇一個內存單元,使電荷可以在位線與內存單元間流動。如果位線電壓高于內存單元,那么負電荷就會從內存單元流出到位在線;而如果位線的電壓低于內存,那么負電荷就會從位線流進內存單元。

圖1:傳統電容式DRAM內存單元的電荷分配原理 (圖中綠色箭頭所示為電流,與負電荷流動的方向相反)

這種電荷轉移改變了位在線的電壓,透過感測與鎖存得到最終讀取數值。然而,在儲存電容中失去或取得的電荷,改變了節點上原有的電荷,這意味著讀取的過程是破壞性的。因此,在每一次讀取之后,都必須透過回寫操作恢復內存單元中的電荷。

LPDDR4

LPDDR4標準是第四代雙倍數據速率(DDR) DRAM的低功耗版本標準,透過整體架構定義了個別內存芯片的高層級結構,以及如何安排雙列直插式內存模塊(DIMM)。

分析DRAM的方式一般有兩種:理論上,剖析其實體細節;實際上,則著眼于其芯片數組特性。本文首先探討第一種邏輯觀點,因為所有的實體布局都必須分解為相同的邏輯結構,因而能夠從中了解傳統DRAM和LVT途徑如何實現邏輯功能。

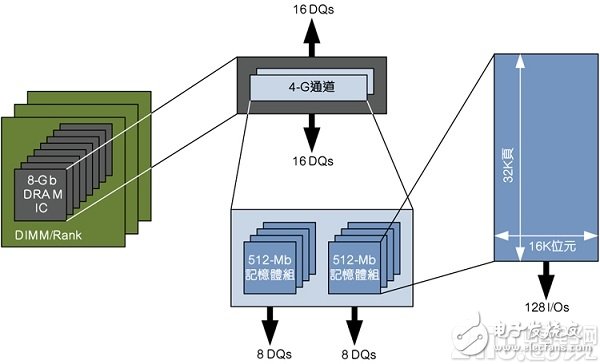

LPDDR4內存芯片擁有8Gb的儲存容量,通常由兩個4Gb的獨立通道共同組成。每信道擁有8個內存組,每一內存組包括32K儲存頁(page),每頁有16K位,而使內存組的總容量達到512Mb。

圖2:典型的DRAM架構和層級

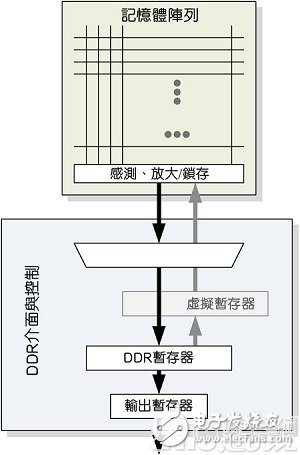

一個完整的LPDDR4內存芯片包括兩個高層級單元:內存數組和DDR接口。有些部份的操作會影響到內存數組;另一部份則會影響接口。DDR接口可以同時與內存數組以及外部系統進行通訊。

圖3:LPDDR4的邏輯組織架構,圖中將儲存數組和DDR接口分開。(箭頭代表一次讀取操作以及回寫)

圖3說明了這種關系,即DDR緩存器作為外部系統和內存數組之間的主接口。而在讀取數據時,數組數據會先被加載DDR緩存器中;進行寫入作業時,所需的數據會先從外部寫入緩存器中。

由于讀取傳統DRAM數組內容可能破壞原有數據,每一次讀取后都必須進行回寫作業,以恢復原有值。在進行讀取后,DDR緩存器的內容被復制到“隱藏緩存器”(Shadow Register)中。當外部系統讀取DDR緩存器中的數據時,隱藏緩存器負責將數據回寫到所選頁,以恢復原有數值。同樣地,當寫入數據時,DDR緩存器的數據會被傳輸到隱藏緩存器中等待寫入;而在執行寫入作業時,DDR緩存器就可以加載新的數據。

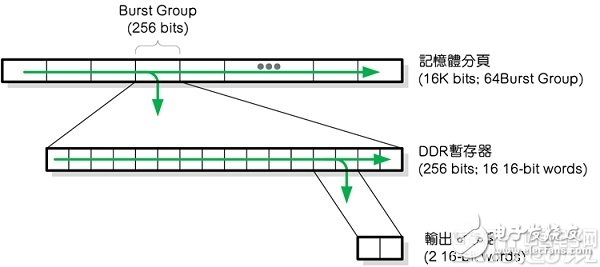

讀取內存分頁數據涉及一連串的活動,類似于兩個巢式的軟件DO回路(Do loop)。每一分頁內存被分成由許多256字節成、成批(burst)讀取的內存群組,因此,一組16K位分頁就有64個burst內存群組,依序讀取完整的內存頁,這類似于外部DO回路。

圖4:內存分頁由分批依序讀取的內存群組構成;每一批burst群組均依據16個連續的16位傳送到I/O。

每個突發傳輸組被加載256位的DDR緩存器中,該緩存器被分為16個16位字,并依序讀取其內容,為每一個頻率邊緣提供每一個16位字。這種操作方式則如同內部DO回路。

每一行的地址(RAS)負責選擇分頁。同時,每一列的地址(CAS)選擇突發傳輸組,并設置從DDR緩存器中開始讀取的字符,因而不必從DDR緩存器的左側開始讀取。

值得注意的是,在隱藏緩存器執行回寫、讀取或寫入DDR緩存器中原先加載數據的同時,DDR緩存器已經開始從儲存數組中讀取數據或從外部加載所寫數據了。

電子發燒友App

電子發燒友App

評論