昨天,有一則關(guān)于臺(tái)積電自研芯片的文章刷爆了筆者的朋友圈。行業(yè)內(nèi)的媒體的報(bào)道尚算中肯,也就是談了臺(tái)積電做了一個(gè)什么樣的芯片,提供了怎么樣的一個(gè)Demo,但有些標(biāo)題黨的作者甚至用“臺(tái)積電要搶高通生意”這樣的字眼來吸引讀者。無論如何,這都與筆者所了解的臺(tái)積電不一樣。

隨著基于小芯片(chiplet)的設(shè)計(jì)從研究轉(zhuǎn)向生產(chǎn),我們看到了來自工業(yè)界的小芯片論文的新流入。本月早些時(shí)候在日本京都舉行的VLSI 2019上,臺(tái)積電展示了自己的“小芯片”設(shè)計(jì)。

據(jù)雷鋒網(wǎng)的報(bào)道,所謂“chiplet”是一種芯片,封裝了一個(gè)IP(知識(shí)產(chǎn)權(quán))子系統(tǒng)。它通常是通過高級(jí)封裝集成,或者是通過標(biāo)準(zhǔn)化接口使用。至于它們?yōu)槭裁磿?huì)變得如此重要,這是因?yàn)槲覀兊挠?jì)算和工作類型呈爆炸式增長,目前沒有一種全能的辦法來應(yīng)對(duì)這些問題。從根本上說,對(duì)一流技術(shù)的異構(gòu)集成是延續(xù)摩爾定律的一種方式。

使用基于小芯片的設(shè)計(jì)具有一些顯著優(yōu)點(diǎn),例如更快的開發(fā)周期和更高的產(chǎn)量來降低成本。但它也帶來了一系列新的挑戰(zhàn),這些挑戰(zhàn)源于在基于小芯片的設(shè)計(jì)中追求類似單片產(chǎn)品(monolithic-like)的功耗和性能特性。因此,當(dāng)中的主要挑戰(zhàn)是互連和封裝技術(shù)。雖然這些挑戰(zhàn)仍然懸而未決,但已經(jīng)有多種具有不同性質(zhì)的解決方案被提出。在超大規(guī)模集成電路研討會(huì)上,臺(tái)積電展示了他們的一些技術(shù),試圖解決這些挑戰(zhàn)。

臺(tái)積電試圖驗(yàn)證的三個(gè)主要特性是:

ARM核心在4 GHz以上工作

Bidir互連網(wǎng)狀總線(Interconnect Mesh)在4 GHz以上

CoWoS和LIPINCON的速度為8 GT / s且<1 pJ / bit

值得注意的是,此研究和技術(shù)驗(yàn)證旨在用于高性能計(jì)算。因此,這些內(nèi)核擁有非常高的時(shí)鐘,高速率的內(nèi)部互聯(lián)速率,以及高密度線路和每比特傳輸極低功率的芯片間鏈路(inter-chip links with high-density wires and very low power per bit transfer)。

首先看芯片方面;

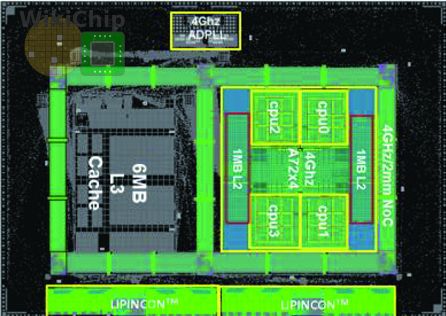

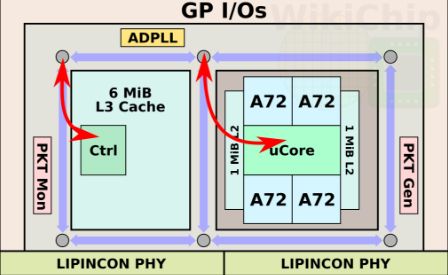

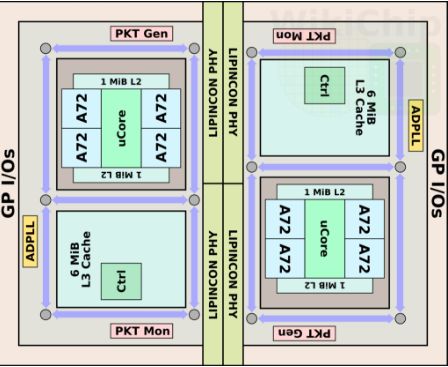

該芯片本身是一種雙小芯片設(shè)計(jì),但該技術(shù)本身可以通過額外的物理層(PHYS)相對(duì)容易地?cái)U(kuò)展到容納更大數(shù)量的小芯片。每個(gè)小芯片都是在臺(tái)積電7納米節(jié)點(diǎn)上制造,擁有15個(gè)金屬層。裸片本身只有4.4 mm×6.2 mm(27.28 mm2)。臺(tái)積電采用了四個(gè)ARM Cortex-A72核。針對(duì)turbo頻率大于4GHz電壓操作,配備了高性能的cell(7.5T,3p + 3n)并定制設(shè)計(jì)1級(jí)高速緩存單元。還有兩個(gè)2級(jí)緩存塊。每個(gè)是1 MiB。這些是使用它們的高電流位單元(bitcells)并以半速運(yùn)行來實(shí)現(xiàn)的。此外還有一個(gè)大型的6 MiB 3級(jí)緩存,使用高密度位單元實(shí)現(xiàn),并以四分之一速度運(yùn)行。

臺(tái)積電采用了在高性能芯片中常見增強(qiáng)功能。典型的h-tree被用來將時(shí)鐘分布的偏差從22ps減少到8ps。高性能時(shí)鐘偏差以及via towers被廣泛用于進(jìn)一步改善關(guān)鍵路徑上的時(shí)序。統(tǒng)計(jì)顯示,整個(gè)設(shè)計(jì)共有五個(gè)電壓域(voltage domains):0.8V SOC、0.8V ADPLL、0.3-0.8V Lipincon、0.8V L3和0.3-1.2V CPU。該芯片采用全數(shù)字鎖相環(huán),其抖動(dòng)小于10ps,用于為CPU、互連和內(nèi)存生成三個(gè)時(shí)鐘域(clock domains )。

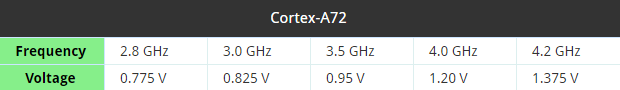

在1.20的電壓下,Cortex核可以達(dá)到4GHz (signoff).。這個(gè)數(shù)字是基于運(yùn)行Dhrystone模式工作負(fù)載的核心測(cè)量得到的。

其次來看一下網(wǎng)狀互連(Mesh Interconnect);

該裸片包括網(wǎng)狀互連。互連測(cè)試可通過片上分組生成單元(on-die packet generation unit )和分組監(jiān)控單元(packet monitoring unit)完成。有六個(gè)雙向觸發(fā)器(bi-directional flip-flop)網(wǎng)格站(mesh stations)——每個(gè)邊緣一個(gè),中間兩個(gè)。這些工作站圍繞整個(gè)小芯片,間隔大約2毫米。網(wǎng)狀互連是1968位寬,并使用具有相反方向信號(hào)(opposite direction signals )的逐位交錯(cuò)線路(bit-wise-interleaved wires )在M12和M13中布線,以最小化耦合( minimize coupling)。

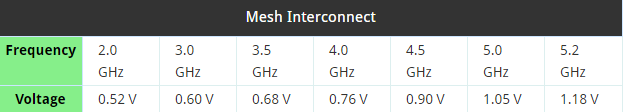

總之,片上網(wǎng)狀互連(on-die mesh interconnect)可以在4 GHz(0.8 V)到5 GHz(1.2 V)之間正常工作。緩存和Cortex集群都連接到最近的左下角(bottom-left )網(wǎng)格停止點(diǎn)(垂直方向時(shí))。

互連可在0.76V下達(dá)到4GHz的頻率。

再看一下芯片互聯(lián);

每個(gè)小芯片上都有兩個(gè)LIPINCON(Low-voltage-In-Package-INterCONnect簡稱)接口。每個(gè)物理層的測(cè)量值僅為0.42 mm×2.4 mm(1.008 mm2)。這些是單端(single-ended),單向(unidirectional),低擺幅接口(low-swing interfaces)。一個(gè)接口用作與L3通信的主設(shè)備,而第二個(gè)接口是用于相反方向的從設(shè)備。

與SoC的其他部分不同,由于電源接地(power-ground)噪聲問題,專用時(shí)鐘有一個(gè)獨(dú)立的PLL。每個(gè)物理層使用2:1多路復(fù)用功能,以便將速度加速到8 Gb / s。每個(gè)子通道有兩個(gè)延遲鎖相環(huán)( DLL):一個(gè)減少PVT變化,另一個(gè)用于減少時(shí)鐘偏差,使系統(tǒng)級(jí)芯片和物理層之間的時(shí)鐘相位對(duì)齊。由于使用單相鎖相環(huán),因此會(huì)采用兩個(gè)環(huán)路——第一個(gè)環(huán)路鎖定進(jìn)入的時(shí)鐘周期,并將其分為八個(gè)相位,第二個(gè)環(huán)路將該相位分為16個(gè)步驟。換句話說,在4 GHz(250 ps)下,您將看到低于2 ps的分辨率。

在本篇論文中,兩個(gè)裸片連在一起。第二個(gè)小芯片旋轉(zhuǎn)180度,用于LIPINCON PHY基臺(tái)(abutment)。

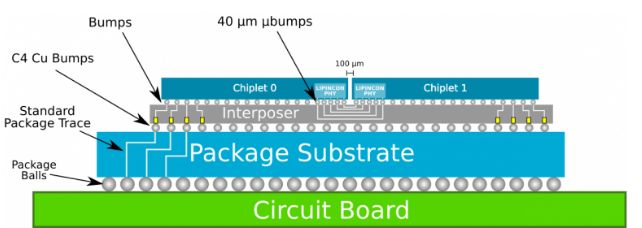

芯片本身采用了臺(tái)積電COWOS(Chip on Wafer on Substrate)2.5D封裝技術(shù),也就是將邏輯芯片和DRAM 放在硅中介層(interposer)上,然后封裝在基板上。臺(tái)積電在這里應(yīng)用,就意味著硅中介層(silicon interposer)將用作安裝在其上的兩個(gè)相同小芯片的基板。

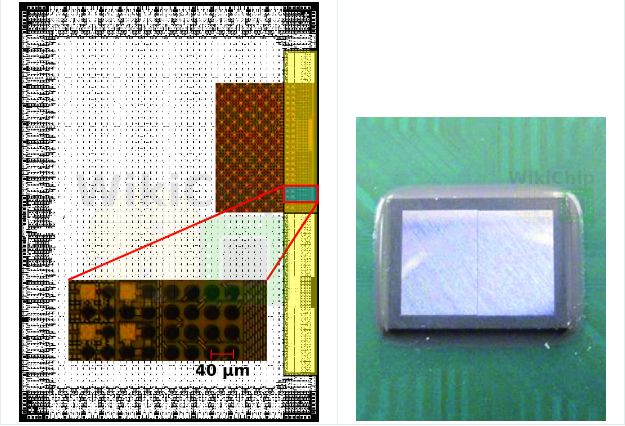

使用硅中介層可以采用更小的凸塊(bumps),使得小芯片之間的導(dǎo)線更密集和更低。在這種設(shè)計(jì)中,使用了一個(gè)非常激進(jìn)的40μm的微凸距,兩個(gè)裸片之間只有100微米的間隔。

我們最后來看一下技術(shù)比較;

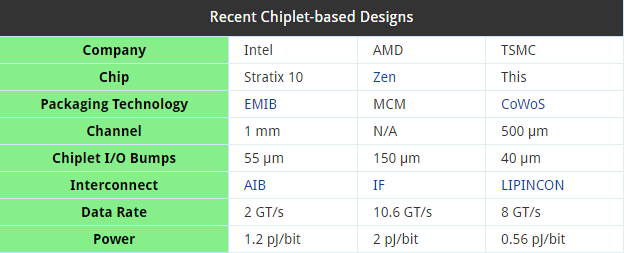

在兩倍的時(shí)鐘速度下,物理層運(yùn)算速度為8GT/s。在互連寬度( interconnect width)為320位時(shí),兩個(gè)裸片之間的總帶寬為320 GB / s。在40μm的bump pitch 下,這實(shí)際上是我們?cè)谧罱男酒O(shè)計(jì)中看到的最激進(jìn)的間距之一,它還可以達(dá)到1.6 Tb / s /mm2的數(shù)據(jù)通量。下表對(duì)比了AMD和Intel最近的兩款小芯片設(shè)計(jì)。值得一提的是,英特爾之前曾提到過EMIB(嵌入式多芯片互連),其bump pitches為45μm,甚至將電流密度增加一倍至35μm。

但是,到目前為止,我們還沒有發(fā)現(xiàn)任何能夠證明這些功能的英特爾產(chǎn)品(包括Kaby Lake G)。

-

芯片

+關(guān)注

關(guān)注

455文章

50714瀏覽量

423131 -

頻率

+關(guān)注

關(guān)注

4文章

1494瀏覽量

59211 -

高性能

+關(guān)注

關(guān)注

0文章

157瀏覽量

20396

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

臺(tái)積電要自研光刻機(jī)#芯片 #臺(tái)積電

【AD新聞】競(jìng)爭(zhēng)激烈!臺(tái)積電中芯搶高通芯片訂單

小米自研芯片澎湃S2采用16nm工藝 臺(tái)積電代工

基于臺(tái)積電5nm工藝的麒麟9000或?qū)⑹侨A為高端芯片的絕版

臺(tái)積電市值多少億_臺(tái)積電為什么聽美國的

蘋果已預(yù)定臺(tái)積電基于3納米工藝芯片的生產(chǎn)能力

蘋果已預(yù)定臺(tái)積電3nm產(chǎn)能

蘋果已預(yù)訂臺(tái)積電最新的3nm芯片

臺(tái)積電為什么不自己做芯片?

首個(gè)2nm芯片定了!富士通自研CPU將由臺(tái)積電生產(chǎn)

焦點(diǎn)芯聞丨蘋果 CEO 為臺(tái)積電美國工廠站臺(tái),自研芯片將首次在美制造

OpenAI自研芯片計(jì)劃調(diào)整,傳交臺(tái)積電生產(chǎn)

谷歌Tensor G5芯片轉(zhuǎn)投臺(tái)積電3nm與InFO封裝

蘋果2025下半年將采用自研Wi-Fi 7芯片

這次來真的了?蘋果自研Wi-Fi7芯片采用臺(tái)積電N7工藝,或明年iPhone上首發(fā)

關(guān)于臺(tái)積電自研芯片性能分析和應(yīng)用

關(guān)于臺(tái)積電自研芯片性能分析和應(yīng)用

評(píng)論