3D NAND的位出貨量現在已經超過了2D NAND。并且正在迅速成為NAND Flash存儲器的主導形式。3D NAND已經將NAND微縮形式從光刻驅動轉換到由堆疊層驅動的沉積和蝕刻。

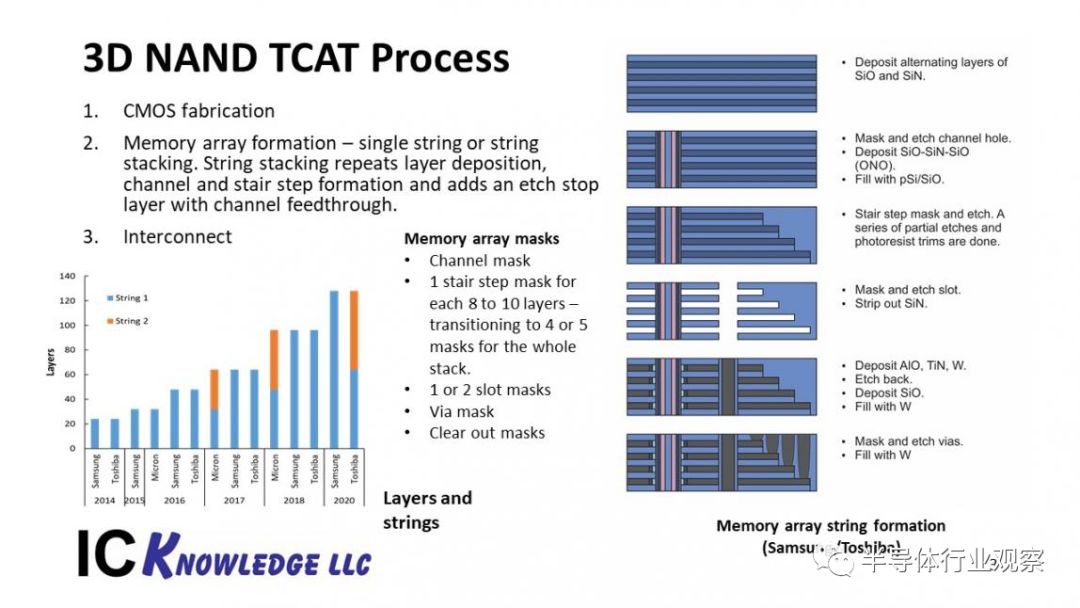

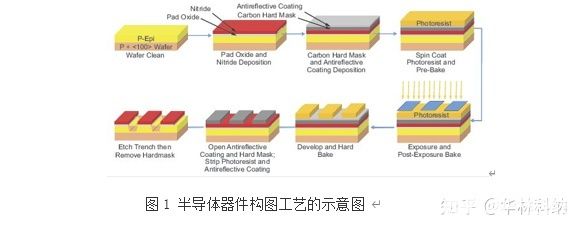

圖1展示了三星和東芝這兩家最大的3D NAND生產商使用的TCAT工藝。

圖1:3D NAND TCAT工藝

在3D制作中,有三個主要部分:

CMOS制造——制造電荷泵,讀寫和存儲器尋址電路。

存儲器陣列的形成——可以是一串或多串。例如,在64層單串制造順序中,所有64層都會沉積,然后形成圖案。在64層雙串制造順序中,先沉積32層并形成圖案,然后沉積另外32層并形成圖案。

Interconnect——CMOS和存儲器陣列是互連的。

存儲器陣列串形成順序是:

沉積氧化物和氮化物的交替層(Deposit alternating layers of oxide and nitride)。 這是柵極的最后一道工序,三星和東芝都在使用。英特爾沉積氧化物和多晶硅的交替層。

應用溝道孔掩模,并向下蝕刻通過堆疊(The channel hole mask is applied and etched down through the stack)。 溝道孔填充氧化物—氮化物—氧化物(ONO)薄膜,然后再填充氧化物的多晶硅溝道。這種蝕刻非常具有挑戰性,特別是對于氧化物/聚合物而言,這就是為什么英特爾比三星或東芝更早地進行串堆疊(string stacking)。

應用厚的光刻膠,并使用階梯式掩模形成圖案(A thick photoresist is applied and patterned with the stair-step mask.)。 蝕刻和收縮順序用于創建一組階梯。在必須剝離掩模并應用新掩模之前,可以創建大約8個階梯。64層器件通常需要8個掩模來制造整個階梯。

應用slot 掩模,并向下蝕刻通過堆疊。(A slot mask is applied and etched down through the stack)。 使用濕法蝕刻蝕刻出氮化物層,然后用氧化鋁和氮化鈦存儲單元膜代替,然后用鎢填充水平層。將鎢蝕刻回slot 中,沉積氧化物,并用鎢填充溝槽。可能還有第二個淺slot 。

現在應用通孔掩模并蝕刻到階梯(The via mask is now applied and etched down to the stair steps)。

在溝道和slot掩模之前可能需要清除掩模,因為硬掩模和層堆疊難以對準。清除是指在層上蝕刻的大面積正方形,以此來暴露對準目標。

上圖左下角的圖表顯示了按公司排列的串。英特爾—美光開始在64層進行串堆疊,東芝預計將在128層進行串堆疊,三星預計將生產128層的單串。

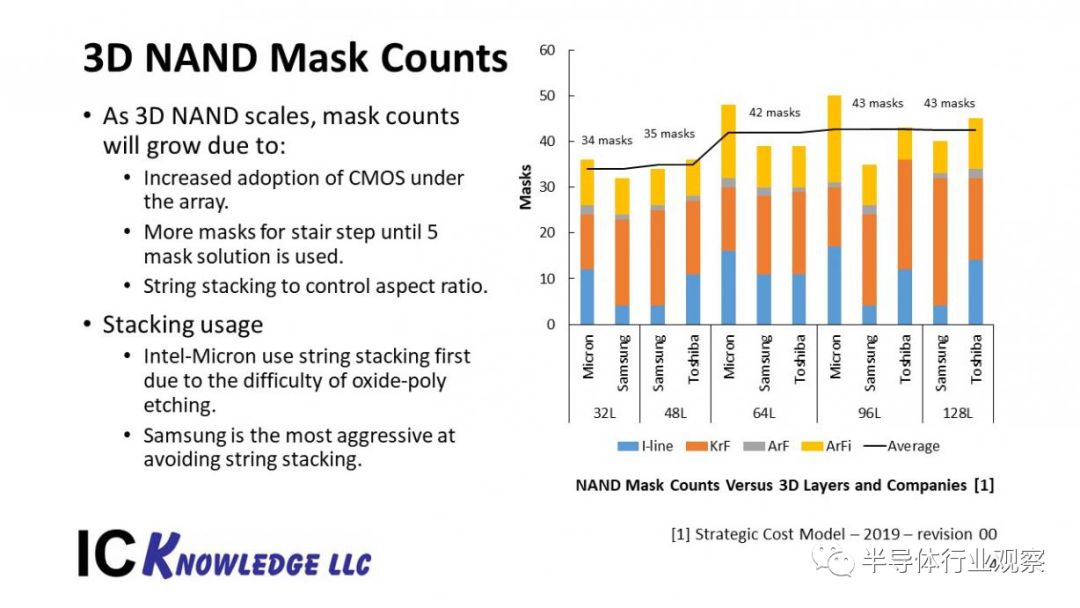

圖2展示了各公司的3D掩膜數量:

圖2:3D NAND掩膜數量

此處有一對相互競爭的趨勢。在存儲器陣列下進行串堆疊和移動某些CMOS會增加掩模數量,而使用較少掩模的精簡階梯的方案會減少掩模數量。

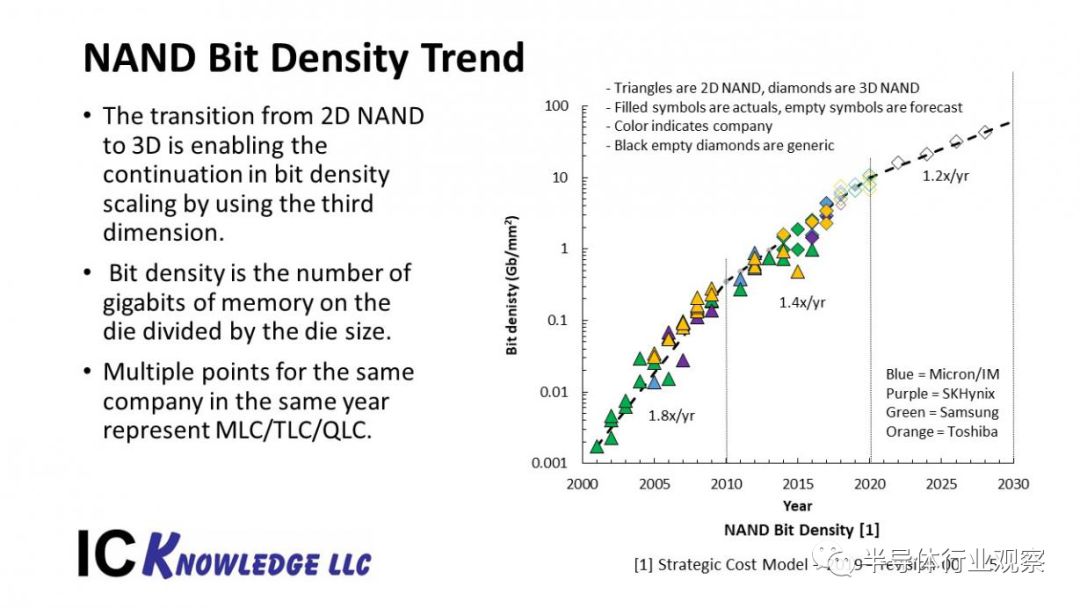

圖3展示了各年份的NAND位密度。

圖3:NAND位密度趨勢

從2000年到2010年,2D NAND由光刻驅動的微縮帶來了1.8倍/年的位密度增長。2010年后,由于器件微縮問題,2D NAND光刻驅動微縮速度減慢,位密度增長放緩至1.4倍/年。21世紀10年代中期,3D NAND被引入,并在這個十年的接下來的時間中延續了1.4倍/年的微縮趨勢。在20世紀20年代,由于制造如此高的存儲器堆棧的挑戰,我們預測微縮將進一步放緩到1.2倍/年。

DRAM—外圍微縮和新選擇

DRAM微縮一直面臨著試圖縮小電容的基本挑戰,外圍微縮已成為關鍵因素。

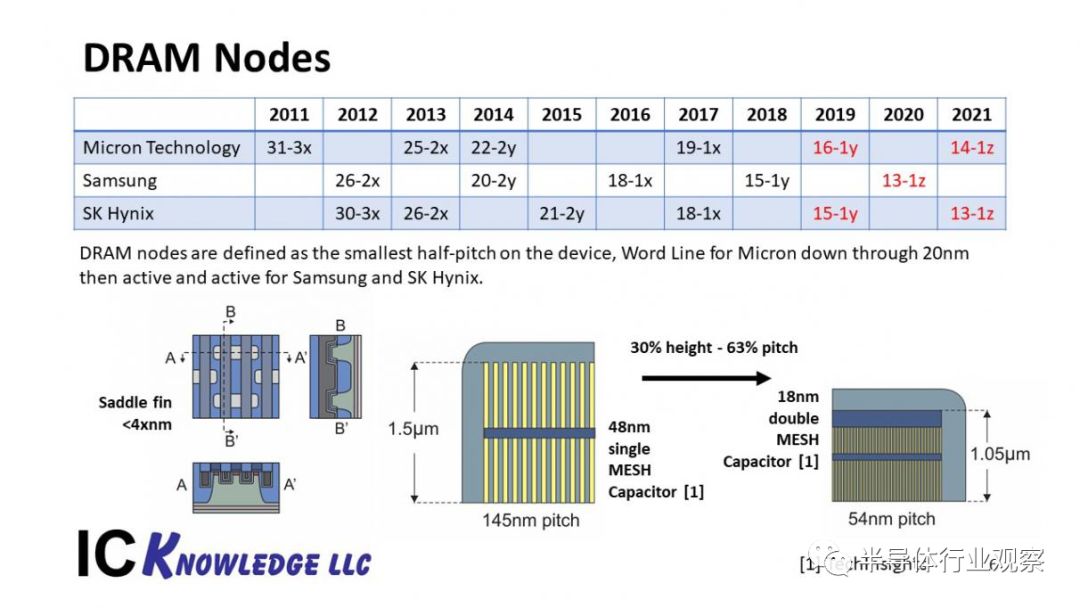

圖4展示了各公司的DRAM節點微縮情況。

圖4:DRAM節點

圖4中可以看到各公司的DRAM節點。在幻燈片底部列出了一些關鍵的技術成果。左下角是馬鞍形存取晶體管(Saddle Fin access transistor),目前在DRAM中普遍使用。右下角列出了從48nm節點到18nm節點的電容微縮。

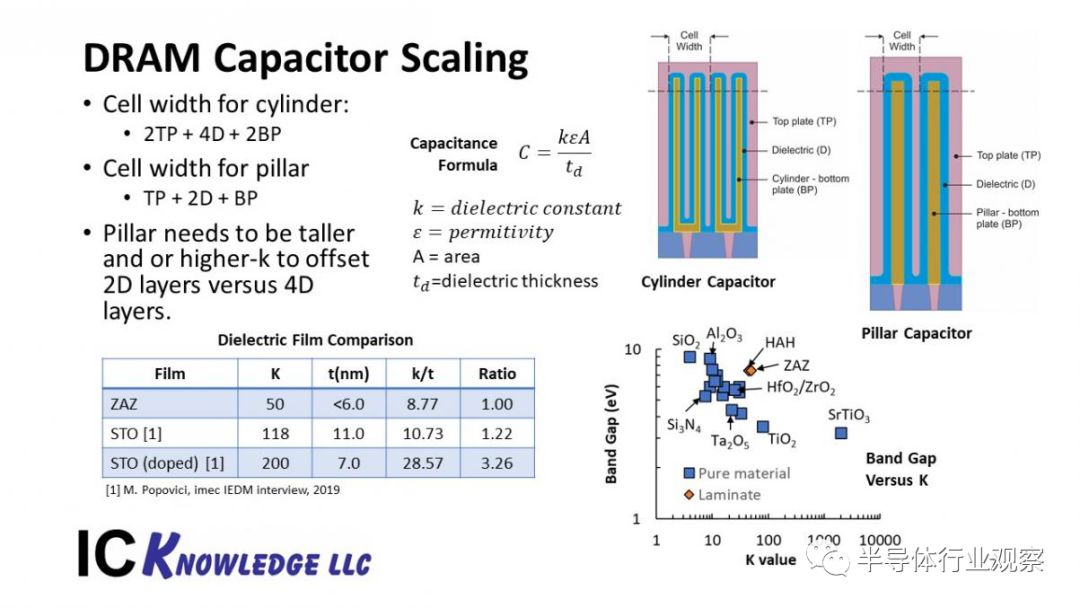

圖5展示了DRAM電容的微縮。

圖5:DRAM電容微縮

DRAM將數值存儲為電容器上的電荷或缺少電荷。為了保持這個值并可靠地感知它,我們需要一個最小電容值。電容器的電容由薄膜的k值乘以一個常數和電容器的面積除以薄膜厚度得到。理想情況下,我們希望電容器更小,以縮小DRAM,但這會降低電容。我們使用垂直尺寸來增加電容器的3D面積,同時縮小水平面積,但我們面臨著高度上的機械限制。電介質的薄膜厚度已經在沒有太多泄漏的情況下盡可能地薄了。從右下角的圖中可以看出,隨著k值的增大,帶隙通常會減小,而帶隙的減小會增加泄漏。

Imec在IEDM 2019會議上報告的一個有趣的最新結果是,一種基于鈦酸鍶的薄膜具有較高的k值,如果足夠厚,可以達到可接受的泄漏。當然,使薄膜變厚會降低電容,因此薄膜的品質因數變為k / t,其中t是可接受泄漏的厚度。左下方的表格列出了目前的氧化鋯—氧化鋁—氧化鋯(ZAZ)薄膜、目前的Imec STO薄膜,以及Imec認為可以實現的摻雜STO薄膜。目前ZAZ薄膜的品質因數是8.77,Imec為10.73,提高了1.22倍,如果Imec能夠實現它們的預期薄膜,品質因數將是28.57,提高3.26倍。

要想獲得更厚的薄膜,就需要改變電容的結構。目前的圓柱結構在每個單元中具有2個底部存儲板厚度,4個介質膜厚度和2個頂部存儲板厚度。為了適應介質膜的厚度,單元需要改變,以滿足所需的單元尺寸。柱狀結構具有1個頂部存儲板厚度、2個介質膜厚度和1個底部存儲板厚度。這使得縮小單元更容易,但它只有2個而非4個介質膜厚度,因此你得到的電容只有一半,除非你使支柱更高。柱子在機械上更堅固,應該可以更高,但可能不能高出兩倍。然而,如果一種薄膜可以達到像Imec預計的STO(摻雜)那樣的效果,那么它的品質因數是3.26,即使在相同的高度下也會增加電容。

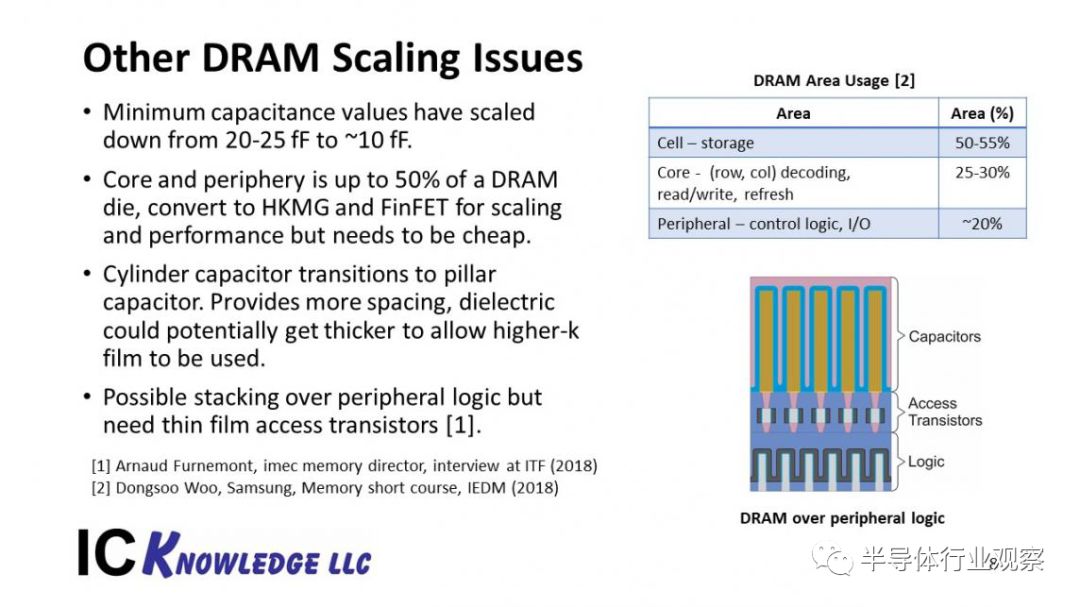

圖6展示了其他一些DRAM微縮問題。

圖6:其他DRAM微縮問題

圖6總結了其他一些DRAM擴展問題,特別是:

最小電容值已從一度被認為是最小電容值的20-25fF縮小到10fF左右。這是通過優化驅動電路和感應放大器實現的。

如右上角的表格所示,核心和外圍電路占DRAM裸片的大約50%,縮小這些電路有助于縮小DRAM裸片。最終,這些晶體管將轉變為高k金屬柵極(HKMG)和FinFET,但這需要以較低的成本來完成。

正如前面所討論的,圓柱形電容器可以改為柱狀電容器,以便為介質薄膜提供更多的空間。

如果薄膜晶體管能夠以足夠低的漏電率開發,那么DRAM電容在晶體管上的堆疊邏輯就可以成為一次性微縮的助推器。

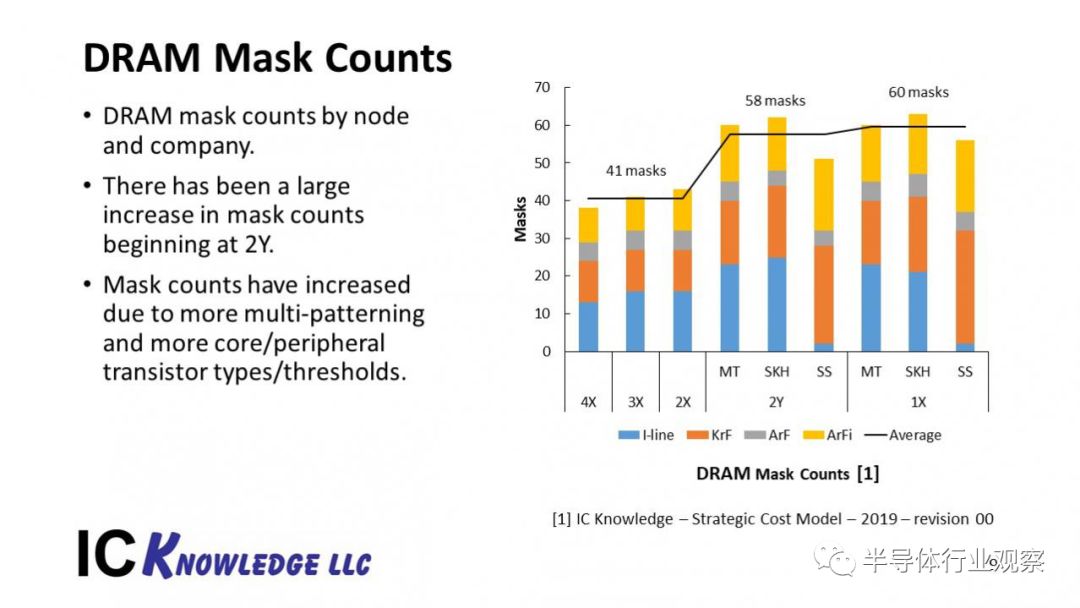

圖7展示了DRAM的掩模數量。

圖7:DRAM掩模數量

優化外圍晶體管和核心晶體管的需求使得多種晶體管類型和閾值電壓的晶體管數量大幅增加。這是從去年的演示中更新的,在去年的演示中,我們低估了兩年及以后的DRAM的掩模數量。

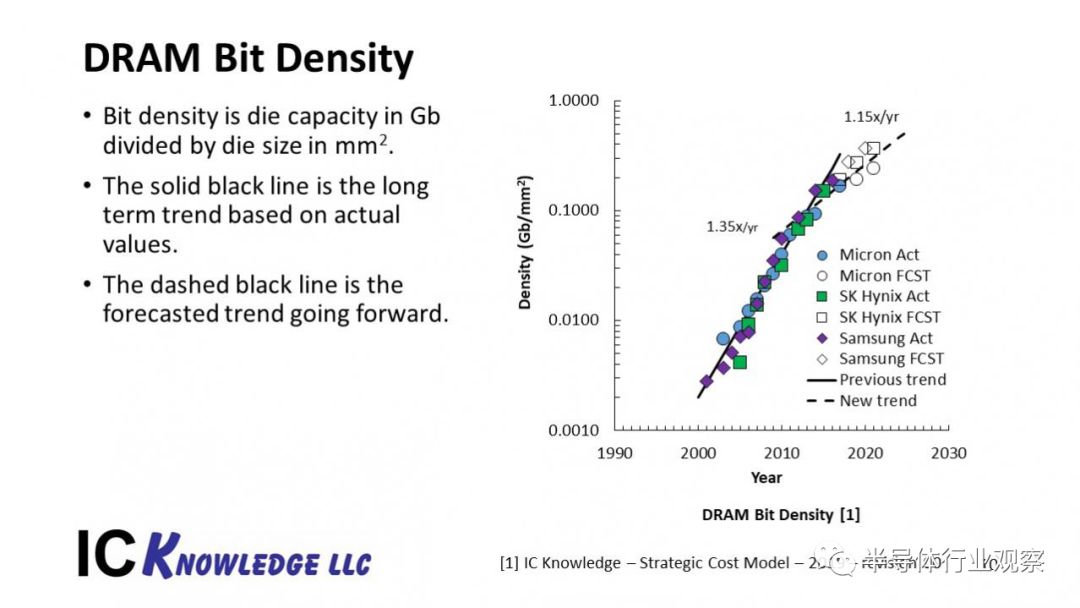

圖8展示了DRAM的位密度趨勢。

圖8:DRAM位密度

從圖8中我們可以看到,2010年之前,DRAM的位密度以每年1.35倍的速度增長,此后,位密度的增長已經放緩到1.15倍/年左右。

邏輯—高性能和物聯網

前沿邏輯已經從平面晶體管發展到分裂的路線圖,FinFET用于高性能,FDSOI用于物聯網。更長遠的“環繞柵極”(gate-all-around)即將到來。

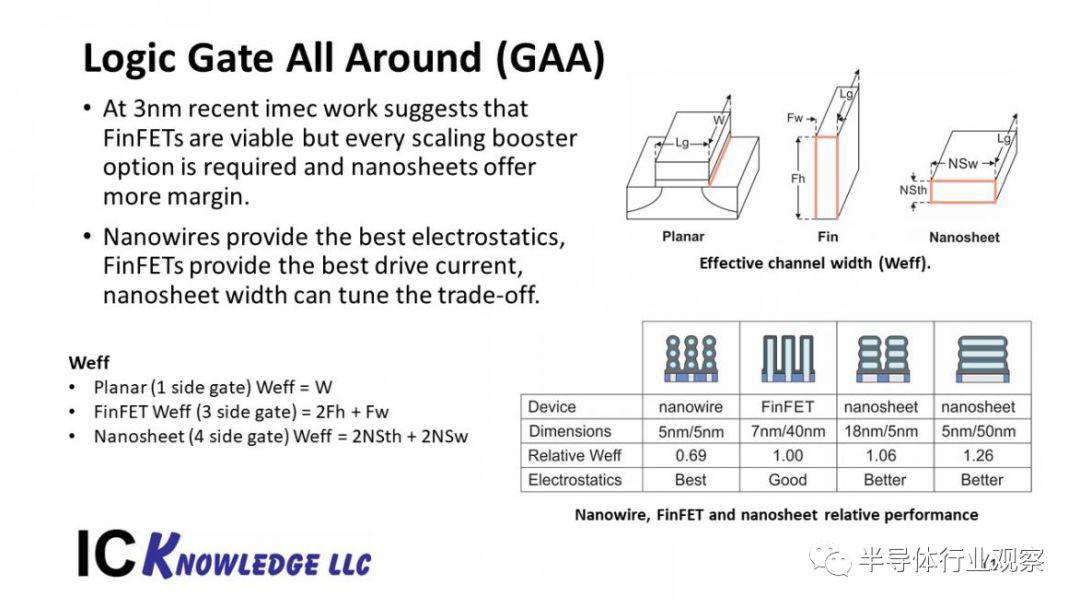

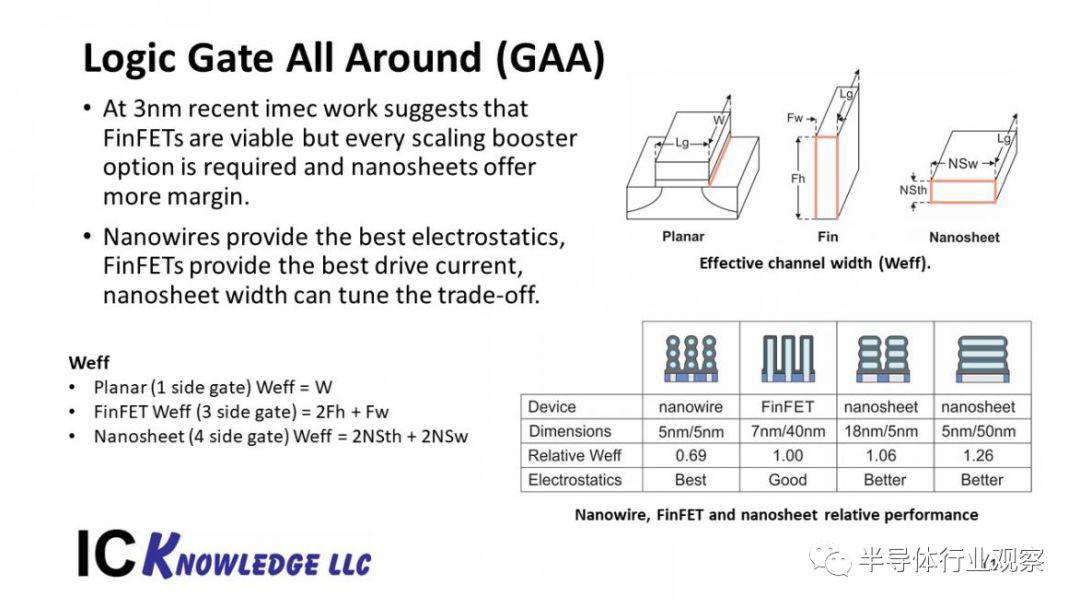

圖9展示了邏輯的環繞柵極(GAA)。

圖9:邏輯的環繞柵極(GAA)

從圖9可以看出,對于平面晶體管,有效柵寬(Weff)是由晶體管柵寬決定的。對于FINFET,Weff取決于鰭的寬度和高度的2倍,因此Weff只能以離散的增量變化。對于GAA,Weff為厚度的2倍,寬度的2倍。改變寬度的能力可以再次啟用可變Weff,并實現晶體管優化。例如,從右下角我們可以看到,水平納米線(HNW)的靜電性能最好,但單位面積的Weff小于FinFET。隨著水平的納米片的變化,寬度可以提供比具有更好靜電的FinFET更高的單位面積的Weff數值,盡管不如HNW好。

圖10展示了從2D到3D的前沿邏輯路線圖

圖10:從2D到3D的前沿邏輯路線圖

圖10展示了從28nm和20nm節點的2D平面晶體管到FinFET,然后是HNS,以及最終堆疊3D CFETS的路線圖。直到N7的典型代工邏輯尺寸全都如表所示。

對于N5和N3.5,我們對三星和臺積電有具體的預測。在N2.5,我們有一個通用的預測,兩家公司都集中在HNS上。

對于3D,我們可以從寬松的14nm設計規則CFET(7層)開始,以及更激進的3.2、3.3和3.4 CFET(3nm光刻,2、3、4層)。圖中顯示了單層器件的nFET和pFET,然后是用于2層CFET的pFET和nFET。

圖11展示了不同公司的掩膜數量,并通過2層CFET進行了預測。

圖11:前沿邏輯掩模數量趨勢

此圖的一個有趣特性是EUV如何有助于減少掩模數量的增加。1.75nm節點的CFET也有助于通過高度自對準來控制光刻難度。

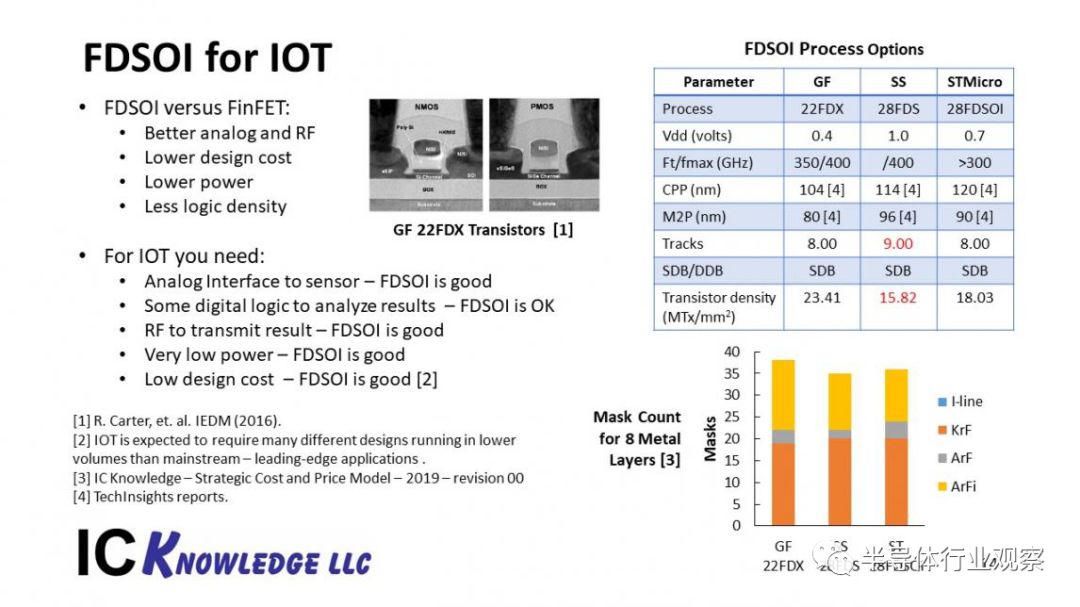

圖12展示了物聯網應用的FDSOI工藝。

圖12:物聯網應用的FDSOI

物聯網需要有模擬傳感器接口,處理結果、存儲結果,并進行無線傳輸,這與FDSOI工藝非常匹配。與FinFET相比,更簡單的FDSOI工藝的設計和生產成本也更低。

右邊的表格總結了三家領先供應商的FDSOI工藝,GLOBALFOUNDRIES最密集、功率最低,射頻性能更高。右下角的圖表列出了工藝的掩模數量。將30年代中期的掩模數量與60年代的FINFET工藝和掩模數量進行比較會是一件很有趣的事情。

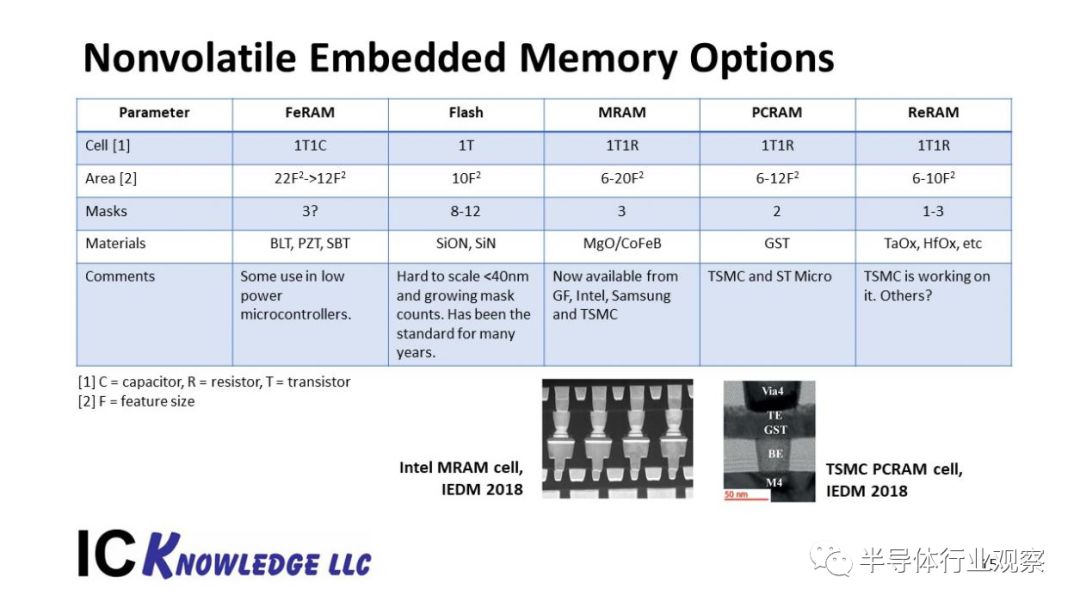

圖13展示了各公司正在探索或提供的非易失性嵌入式存儲器選擇。

圖13:非易失性嵌入式存儲器選擇

圖13展示了嵌入式非易失性存儲器的五種主要替代方案。從歷史上看,Flash已被廣泛使用,FeRAM已經在低功耗微控制器中得到了一些應用。目前,MRAM得到了最多的關注,英特爾和所有領先的代工廠都支持它。PCRAM和ReRAM正在引起人們的注意,但還沒有那么成熟。

結論

NAND已經從2D光刻驅動工藝遷移到3D蝕刻和沉積驅動工藝。pitch從2D值放寬,未來不太可能變得更嚴格。由于串堆疊,掩模數量將會增加。

DRAM微縮是電容器的限制,并面臨基本的物理限制。微縮的重點是核心和外圍的改進,潛在的新的高k電介質即將到來。微縮速度正在放緩。

邏輯繼續以光刻方式進行微縮,但2D收縮的基本限制正在迫近。CFET提供了一種可能的3D微縮路線,可以產生與3D NAND類似的不嚴格的光刻尺寸。物聯網和其他應用正在引起人們對更簡單的FDSOI工藝和新興嵌入式存儲器的興趣。

-

半導體

+關注

關注

334文章

27432瀏覽量

219298 -

嵌入式

+關注

關注

5085文章

19138瀏覽量

305709 -

存儲器

+關注

關注

38文章

7494瀏覽量

163917 -

光刻

+關注

關注

8文章

322瀏覽量

30194

發布評論請先 登錄

相關推薦

回顧半導體技術趨勢及其對光刻的影響分析與應用

回顧半導體技術趨勢及其對光刻的影響分析與應用

評論