隨機(jī)變化需要新方法、新工具,以及不同公司之間的合作。

極紫外(EUV)光刻技術(shù)正在接近生產(chǎn),但是隨機(jī)性變化——又稱為隨機(jī)效應(yīng)正在重新浮出水面,并為這項(xiàng)期待已久的技術(shù)帶來了更多的挑戰(zhàn)。

GlobalFoundries、英特爾、三星和臺積電希望將EUV光刻技術(shù)加入到7nm和5nm生產(chǎn)中。但就像以前一樣,EUV由幾部分組件組成,在芯片制造商能夠引入之前,它們必須整合在一起。包括光刻機(jī)、光源、光刻膠和掩膜。最近,行業(yè)已經(jīng)開始發(fā)布關(guān)于量子隨機(jī)效應(yīng)的警報(bào),這種現(xiàn)象會引起光刻圖案隨機(jī)變化。

有些組件已經(jīng)準(zhǔn)備就緒,而有些則發(fā)展緩慢。事實(shí)上,EUV團(tuán)隊(duì)首次將光刻膠及其相關(guān)問題列為EUV的最大挑戰(zhàn),超過了電源。經(jīng)過多年的推遲,EUV光源功率終于滿足了大批量生產(chǎn)(HVM)的要求。

光刻膠是用來制作圖案的光敏聚合物,它是造成隨機(jī)性效應(yīng)的罪魁禍?zhǔn)字弧8鶕?jù)定義,隨機(jī)效應(yīng)描述了具有光量子隨機(jī)變化的事件。它們是不可預(yù)測的,沒有穩(wěn)定的模式。

在EUV的情況下,光子擊中光刻膠并引起光化學(xué)反應(yīng)。但是對于EUV光刻膠而言,由于量子非定域效應(yīng),每個或多個反應(yīng)期間可能出現(xiàn)新的不同的反應(yīng)。因此EUV容易發(fā)生涉及隨機(jī)效應(yīng)。一般來說,該行業(yè)將隨機(jī)性主要?dú)w咎于光刻膠,但EUV的光掩膜和其他部分(EUV光子平均自由程較大)也可能會出現(xiàn)隨機(jī)變量。

隨機(jī)效應(yīng)并不新鮮。事實(shí)上,這一現(xiàn)象多年來一直困擾著EUV團(tuán)隊(duì)。眾所周知,隨機(jī)效應(yīng)會導(dǎo)致光刻圖案的變化。行業(yè)一直在努力解決這個問題,但人們要么低估了問題,要么沒能及時(shí)解決問題,要么兩者兼而有之。

新情況是,行業(yè)終于迎來了另一個問題。一顆先進(jìn)的邏輯芯片集成了十億個甚至更多的微小通孔。 如果EUV光刻過程中出現(xiàn)問題,芯片可能會遭受由于隨機(jī)效應(yīng)引發(fā)的失效或缺陷(通孔缺失contact missing)。換言之,一顆芯片可能會因?yàn)橐粋€觸點(diǎn)通孔的缺陷而失效。

這可能是一廂情愿的想法,但芯片制造商相信他們可以躲避7nm工藝節(jié)點(diǎn)潛在的由隨機(jī)性引發(fā)的缺陷。事實(shí)上,EUV可能出現(xiàn)在7nm工藝節(jié)點(diǎn)。但在5nm甚至是7nm工藝節(jié)點(diǎn)的情況下,芯片制造商可能無法避免這些和其他問題,除非行業(yè)出現(xiàn)一些新的突破。GlobalFoundries高級研究員兼高級技術(shù)研究總監(jiān)Harry Levinson表示:“公平地講,我們的行業(yè)非常樂觀地看待我們向EUV光刻前進(jìn)的方向。我們正準(zhǔn)備將第一代引入到大批量生產(chǎn)中,展望第二代EUV光刻技術(shù),抵抗隨機(jī)效應(yīng)絕對是最重要的問題之一。”

無論節(jié)點(diǎn)如何,EUV隨機(jī)效應(yīng)都為芯片制造商、晶圓廠工具供應(yīng)商和IC設(shè)計(jì)團(tuán)體帶來了麻煩。西門子公司DFM項(xiàng)目總監(jiān)David Abercrombie表示:“從設(shè)計(jì)的角度來看,隨機(jī)效應(yīng)確實(shí)是隨機(jī)的,因?yàn)槟銦o法預(yù)測變化的位置和數(shù)量。因此,沒有系統(tǒng)的方法可以說一個特定的布局特征應(yīng)該在這個區(qū)域還是在另一個區(qū)域中進(jìn)行修改。換言之,除了避免的所有敏感特性的出現(xiàn),將其轉(zhuǎn)化成傳統(tǒng)設(shè)計(jì)規(guī)則約束以外,完全沒有辦法在設(shè)計(jì)過程中補(bǔ)償隨機(jī)效應(yīng)影響。”

作為回應(yīng),該行業(yè)正在采取措施解決一些問題。其中包括:

? 供應(yīng)商正在改進(jìn)EUV光刻膠。

? Applied Materials和ASML正在開發(fā)一種新的電子束測量工具,承諾可以檢測出隨機(jī)性缺陷。此外,創(chuàng)業(yè)公司Fractilia已經(jīng)設(shè)計(jì)了一種方法來輔助測量。

? 然后,通過這些新的測量數(shù)據(jù),芯片制造商請求有競爭力的晶圓廠工具供應(yīng)商進(jìn)行合作,并一起對信息進(jìn)行整合。

為什么是EUV?

芯片制造商需要EUV,因?yàn)槭褂媒裉斓墓饪碳夹g(shù)來繪制微小特征變得越來越困難。

最初,芯片制造商將把今天的193nm沉浸式光刻和多重曝光擴(kuò)展到10nm和7nm工藝節(jié)點(diǎn)。這些技術(shù)是可行的,但是使用它們來實(shí)現(xiàn)特定圖形變得更加困難。因此,芯片制造商最初希望將EUV用于器件的通孔層。他們將繼續(xù)在其他部分使用沉浸式光刻和多重曝光。

根據(jù)GlobalFoundries的數(shù)據(jù),為了處理觸點(diǎn)/通孔,在今天的7nm工藝節(jié)點(diǎn)中,每層需要2到4個掩膜。但是,EUV每層只需要一個掩膜。

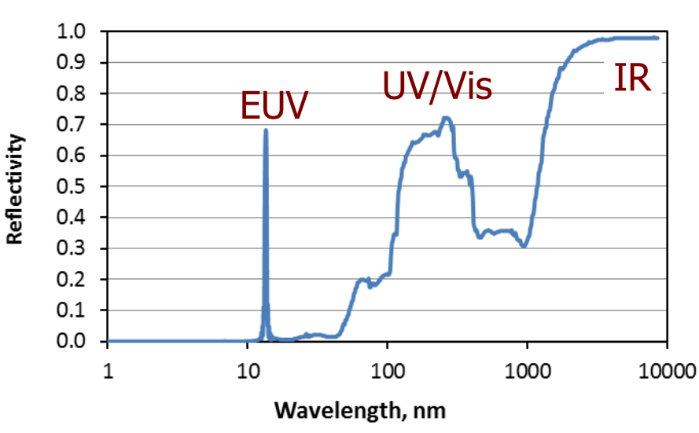

EUV的引入取決于技術(shù)的成熟程度。今天,ASML正在出貨其首款量產(chǎn)EUV光刻機(jī),NXE:3400B。13.5nm波長,擁有13nm光刻圖形分辨率。

EUV光刻機(jī)可以曝光出優(yōu)良的圖形,但多年來EUV光源沒有產(chǎn)生足夠的功率。這影響了系統(tǒng)的整體生產(chǎn)率。現(xiàn)在,ASML正在出貨一個246瓦的EUV光源,生產(chǎn)率為125片晶圓/每小時(shí)(wph)。這達(dá)到了HVM大規(guī)模量產(chǎn)的目標(biāo)水平。

然而,挑戰(zhàn)遠(yuǎn)未結(jié)束。今天的193nm光刻機(jī)可以在250wph下不間斷運(yùn)行。然而,EUV的正常運(yùn)行時(shí)間徘徊在70%和80%左右。ASML產(chǎn)品營銷總監(jiān)Michael Lercel表示:“我們已經(jīng)證明我們可以實(shí)現(xiàn)生產(chǎn)率指標(biāo)。今年的重點(diǎn)是確保實(shí)現(xiàn)可用性。我們的目標(biāo)是達(dá)到90%以上的可用性。”

此外,EUV掩膜版保護(hù)薄膜還沒有準(zhǔn)備好。“薄膜正在進(jìn)步。雖然透光率仍然很低,但是我們已經(jīng)證明了這些薄膜可以在245瓦的條件下使用。在采用一些新材料的離線測試中,我們認(rèn)為它們甚至可以超過300瓦。”

光子計(jì)數(shù)

光刻膠是另一個挑戰(zhàn)。多年來,行業(yè)在248nm和193nm的光刻中使用了化學(xué)放大型光刻膠(CAR)。

簡而言之,光刻光源產(chǎn)生光子或光粒子。光子撞擊光化學(xué)放大型光刻膠,產(chǎn)生光酸。然后,化學(xué)放大型光刻膠在曝光后的烘烤過程中進(jìn)行光酸催化反應(yīng)。

可用于EUV的化學(xué)放大型光刻膠經(jīng)歷類似的過程之后會有不同的結(jié)果。IMEC先進(jìn)圖案部門主管Gregory McIntyre表示:“在EUV案例中,情況要復(fù)雜得多,而且不是很好理解。你要有更高能量的光子,它會產(chǎn)生高能電子,并迅速躍遷為低能量電子。然后這些電子就會與被撞擊的物質(zhì)相互作用。這里有很多的未知因素,比如產(chǎn)生了多少電子,能量是多少,更重要的是,這些電子會產(chǎn)生什么樣的化學(xué)反應(yīng)。”

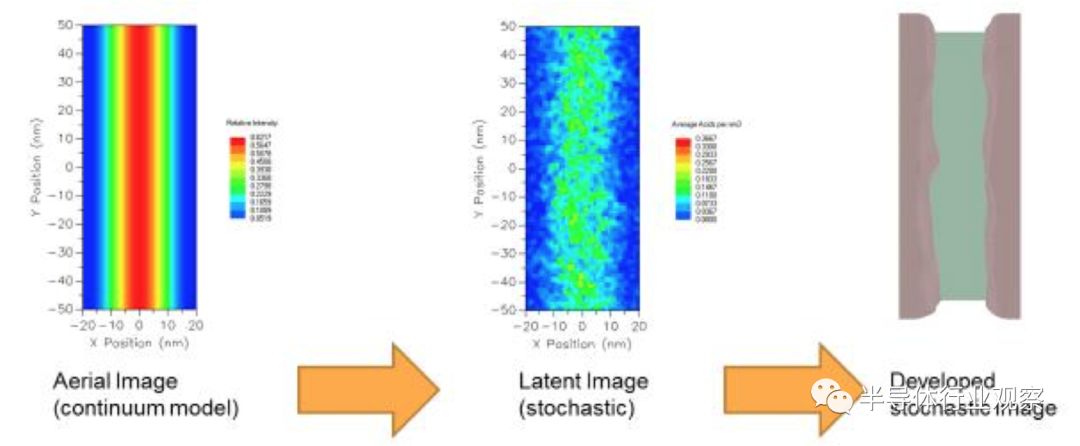

另一種解釋是,當(dāng)系統(tǒng)將光刻膠暴露于EUV光照射下,將一定數(shù)量的光子送入了光刻膠。理想情況下,這些光子會均勻分散。但是光刻膠的一點(diǎn)可能會吸收10個光子,而另一個點(diǎn)可能會吸收8個光子。這種不希望的結(jié)果被稱為量子隨機(jī)效應(yīng)(量子漲落)。

圖1:隨機(jī)性圖像。 (來源:Fractilia,GlobalFoundries)

在另一個例子中,假設(shè)EUV光在三個連續(xù)和單獨(dú)的事件中擊中光刻膠。在第一個事件中,光刻膠吸收10個光子。第二次吸收9個光子,第三次吸收11個光子。這種從一個事件到下一個事件的變化稱為光子散射噪聲現(xiàn)象。

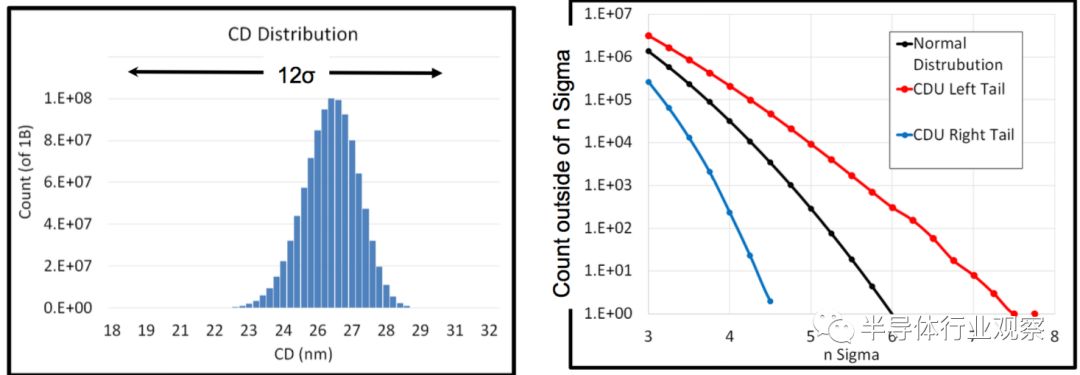

如果將這些事件繪制在圖表曲線上,那么光子的分布有時(shí)是不理想的。McIntyre表示:“隨著我們走向越來越小的特征尺寸,我們會發(fā)現(xiàn)高斯分布開始長出一條尾巴,并且在一邊變得不對稱。這種尾巴的增長導(dǎo)致極不可能發(fā)生事件的可能性增加。”(隨機(jī)漲落效應(yīng)的影響大大增加)

圖2:帶尾巴的高斯分布。右邊的圖表基于1B數(shù)據(jù)點(diǎn)。(來源:GlobalFoundries)

多年前,隨機(jī)效應(yīng)和散射噪聲并沒有出現(xiàn)在雷達(dá)屏幕上,但問題開始出現(xiàn)在193nm光刻技術(shù)中。在193nm處,芯片制造商在光刻圖形邊緣附近使用10mJ/cm2的劑量。Fractilia的首席技術(shù)官Chris Mack解釋說:“如果觀察1nm2的面積,那么在整個曝光過程中,平均有97個光子會穿過該區(qū)域進(jìn)入光刻膠。但是如果觀察10nm2的面積,平均會有9700個光子。”

因此,根據(jù)Mack的說法,當(dāng)有足夠數(shù)量的光子來生成一個圖案的時(shí)候,那么光子散射噪聲或隨機(jī)變異則只有1%。(在大量粒子統(tǒng)計(jì)情況下,量子漲落可以微不足道)

然而,EUV光子的每個光子的能量比193nm的光子高14倍。Mack表示:“這意味著,對于相同的劑量,EUV的光子數(shù)量要少14倍。因此,在上例中,我們有97個光子暴露在1nm2的區(qū)域,而EUV中只有7個光子。相對不確定性是光子數(shù)的平方根分之一。對于97個光子,這是+/-10%的不確定性。對于7個光子,不確定性為+/-40%。”

使得問題復(fù)雜的是,每個節(jié)點(diǎn)的特征尺寸都要更小一些。當(dāng)你計(jì)算光刻過程中光子的數(shù)量時(shí)會發(fā)現(xiàn),在這一點(diǎn)上的變化呈指數(shù)級上升。

這并不新鮮。多年來,Mack和其他人都警告說:“EUV隨機(jī)效應(yīng)可能導(dǎo)致圖案成像中不希望的邊緣粗糙度(LER)。LER被定義為圖案邊緣與理想形狀的偏差。”

LER會影響晶體管的性能。此外,LER不隨著特征大小微縮,因此它在每個節(jié)點(diǎn)的圖案中會占據(jù)更大的百分比。

圖3:線邊緣粗糙度(LER)。 (來源:Lithoguru,F(xiàn)ractilia)

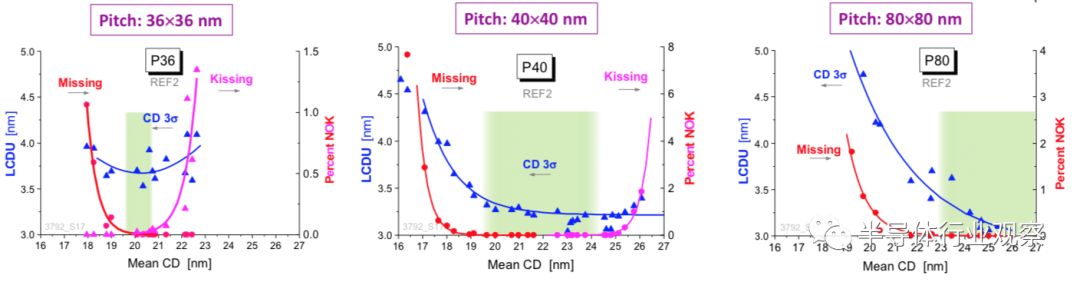

除了LER之外,業(yè)內(nèi)現(xiàn)在還擔(dān)心芯片的其他部分,特別是觸點(diǎn)通孔。在操作中,EUV光刻機(jī)產(chǎn)生對接觸孔進(jìn)行圖案化的光子。但有時(shí),這一過程并不完美,導(dǎo)致通孔中存在隨機(jī)性缺陷。這些缺陷表現(xiàn)為斷線或通孔合并,有時(shí)稱為“通孔丟失和通孔接觸”。

圖4:隨機(jī)性失效和收縮工藝窗口 (來源:Imec)

這些缺陷是災(zāi)難性的。Mack表示:“接觸孔是一個小點(diǎn),你要放一些光子。但是如果只有少量光子,接觸孔有時(shí)會得到100個光子,有時(shí)會是80個,有時(shí)會是140個,結(jié)果就是接觸孔大小的變化。”

這些缺陷可能會在7nm工藝節(jié)點(diǎn)出現(xiàn),但它們更可能在5nm及更先進(jìn)的節(jié)點(diǎn)處出現(xiàn)。Mentor的Abercrombie表示:“EUV中的隨機(jī)效應(yīng)實(shí)際上在CD控制的正常劑量/聚焦窗口上添加了隨機(jī)變化,以及額外的線邊緣粗糙度和光刻劑量變化。對于工程師來說,這意味著更少的工藝窗口,它可以轉(zhuǎn)化為更復(fù)雜的DRC設(shè)計(jì)規(guī)則和更少的工藝縮減。”

Abercrombie表示:“這使得以設(shè)計(jì)為導(dǎo)向的對策非常無效,因?yàn)槟銦o法預(yù)測在任何特定布局位置或配置中會發(fā)生什么情況,因此無法對其進(jìn)行修改。事實(shí)上,由于隨機(jī)效應(yīng)可能會對目標(biāo)平均值產(chǎn)生正負(fù)偏差和LER影響,因此,根據(jù)情況在一個特定位置進(jìn)行修改可能造成的傷害跟益處一樣多。隨機(jī)效應(yīng)將主要成為決定哪些層將使用哪種光刻/多重曝光技術(shù)來實(shí)現(xiàn)驗(yàn)證流程節(jié)點(diǎn)所需的面積和產(chǎn)量要求的重要因素。”

新的解決方案?

解決隨機(jī)問題的一種方法是使用更高曝光能量的EUV光刻膠。理想情況下,芯片制造商需要20mJ /cm2的曝光能量。對于250瓦的光源,這個劑量將達(dá)到125 wph的吞吐量。

20mJ/cm2的光刻膠還沒有準(zhǔn)備好用于7nm工藝節(jié)點(diǎn)。5nm工藝節(jié)點(diǎn)更是懸而未決。因此,行業(yè)做出了一些妥協(xié)。芯片制造商使用曝光能量為30-40mJ/cm2的CAR型抗蝕劑。這些曝光能量提供了良好的分辨率,但速度較慢,并影響EUV的生產(chǎn)率。芯片制造商似乎在30-40mJ/cm2劑量的光刻膠中獲得了良好的產(chǎn)量。

根據(jù)ASML的統(tǒng)計(jì),使用30mJ/cm2的能量時(shí),250瓦光源的EUV掃描器的吞吐量約為104-105 wph,沒有掩膜版保護(hù)薄膜。這低于理想的125 wph目標(biāo)。

那么未來的解決方案是什么呢?英特爾前高級研究員Yan Borodovsky表示:“一種方法是將光源提高到500瓦或1000瓦。這樣就可以使用更高的能量并確保產(chǎn)量。但是500瓦(或以上)的光源仍在研發(fā)中。”

另一種方法是改善EUV光刻膠。Lam Research技術(shù)總監(jiān)Richard Wise表示:“現(xiàn)在,功率的縮減已經(jīng)接近預(yù)期,人們開始投入更多材料。一旦你研究了缺陷或隨機(jī)缺陷的機(jī)制,就會發(fā)現(xiàn)它實(shí)際上是由光子散射噪聲和光刻膠污跡引起的。我可以展示一個圖案,但缺陷是災(zāi)難性的,無法忍受。”

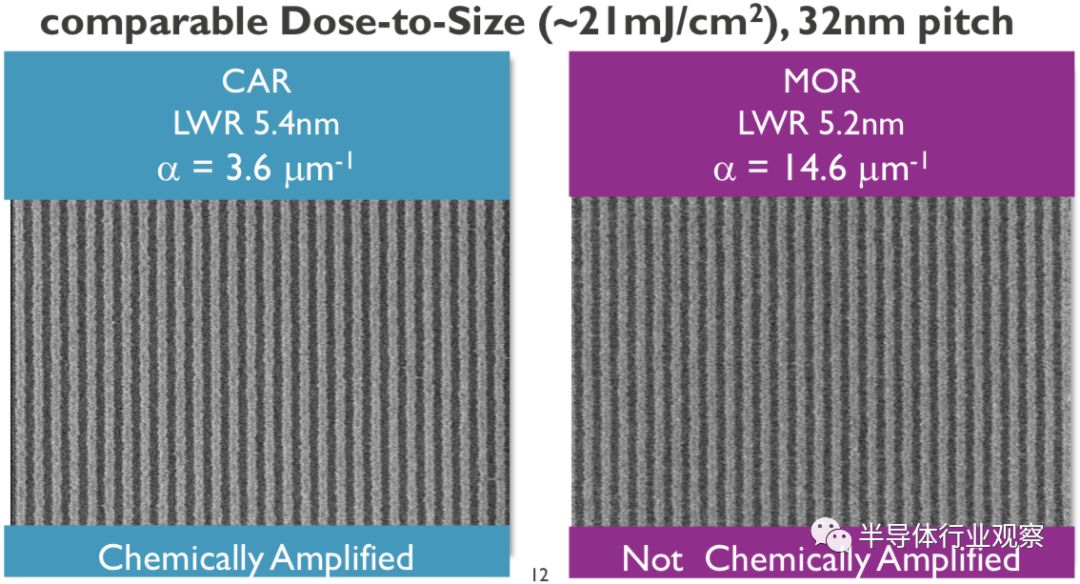

在EUV中,有兩種主要的光刻膠類型——CAR化學(xué)放大型和金屬氧化物。Wise表示:“CAR有著悠久的歷史。這種機(jī)制很好理解。金屬氧化物是更新的。這兩個系統(tǒng)都在取得進(jìn)展。我認(rèn)為他們正在以同樣的速度取得進(jìn)展。”

CAR有幾種變體。一位候選是一個金屬敏化CAR。金屬具有較高的光吸收。康奈爾大學(xué)材料工程教授Christopher Ober表示:“通過加入合適的金屬,你可以在CAR性能方面取得顯著的進(jìn)步。”

其次,JSR、TEL和其他公司正在開發(fā)另一種稱為光敏CAR(PSCAR)的變體。為此,這種機(jī)制會釋放一種酸。然后,它會觸發(fā)光敏劑。Ober表示:“你可以進(jìn)行整片曝光,這會導(dǎo)致更高性能的成像。”

與此同時(shí),初創(chuàng)公司Irresistible Materials正在開發(fā)一種多元觸發(fā)型化學(xué)放大光刻膠。除CAR之外,Inpria正在開發(fā)基于納米氧化錫的金屬氧化物EUV光刻膠。Lam公司的Wise表示:“金屬氧化物的理論是合理的。你會捕獲更多的光子,并且有更高的散射噪聲密度。”

盡管如此,關(guān)于光刻膠還是有一些挑戰(zhàn)和折衷。在SPIE的一篇論文中,TEL和Imec比較了CAR和金屬氧化物抗蝕劑在低于36nm的間距下的低曝光劑量。在SPIE的一次演講中,TEL公司的工藝工程師Sophie Thibaut表示:“在這兩種情況下,你都會有光刻,線寬和粗糙度。CAR在中高頻區(qū)域具有更好的LER和LWR性能。 但含金屬的抗蝕劑對于低頻區(qū)域更好。”

圖5:CAR抗蝕劑vs金屬氧化物抗蝕劑 (來源:Imec)

十億個觸點(diǎn)

除了光刻膠,行業(yè)還面臨著另一個挑戰(zhàn)。如何確保一顆集成了10億個或更多通孔觸點(diǎn)的芯片獲得良好的產(chǎn)量?

計(jì)量學(xué)是第一步,這是測量芯片的科學(xué)。在晶圓廠中,芯片制造商最初使用CD-SEM。但CD-SEM僅限于每次測量10,000個特征圖形,這意味著它可能無法檢測到所有因隨機(jī)效應(yīng)引起的缺陷。

Applied Materials公司的計(jì)量和過程控制主管Ofer Adan表示:“在處理EUV隨機(jī)效應(yīng)時(shí),我們需要測量你所看到的許多屬性。你想看到阻斷層、分割層和正確的CD。你想看到它們被放置在正確的位置。你希望看到它們沒有觸及觸點(diǎn)和通孔。你還希望看到它們沒有間距變化。你有EUV隨機(jī)性。他們與其余的流程步驟互相影響。所以我們需要覆蓋EUV和非EUV之間的接口。這包括套刻精度以及EUV層和非EUV層之間的混合圖形匹配,所以這是一個巨大的挑戰(zhàn)。”

這里還有其他挑戰(zhàn)。GlobalFoundries的高級技術(shù)人員Benjamin Bunday表示:“如果你用光刻機(jī)曝光的產(chǎn)品平均視場尺寸除以我們期望在這些節(jié)點(diǎn)上的接觸孔的間距,那么你的每個全視場就可以處理大約1萬億個特征圖形。我們需要以百萬分之一級別的敏感度來進(jìn)行抽樣。我們?nèi)绾卧诖蠛@頁频侥歉槪恳虼耍瑥哪撤N意義上講,我們正在開始關(guān)注一個理論,我們可能想要衡量10億個特征圖形,以便對這些圖形有很好的抽樣和確定性。現(xiàn)在,當(dāng)然,我相信我們會找到一種方法來減少一些條件,削減幾個數(shù)量級。我們必須要做到切實(shí)可行。但這就是數(shù)字所說明的問題。”

為了幫助解決這一問題,Applied Materials和ASML正在為其電子束檢測工具增加計(jì)量功能。他們將把CD-SEM和套刻精度測量能力混合在一起。

實(shí)際上,一個工具可以在短時(shí)間內(nèi)拍攝大視野。那么,根據(jù)設(shè)備制造商的說法,你可以使用成像技術(shù)來啟用CD-SEM,在幾小時(shí)內(nèi)提供數(shù)百萬次測量。ASML公司的Lercel表示:“只有測量結(jié)果告訴你哪里出了問題,你才能開始解決這些問題。如果你可以測量每一個通孔觸點(diǎn),你就會得到這些數(shù)據(jù),來發(fā)現(xiàn)高斯分布的拖尾部分。”

CD-SEM和相關(guān)工具可能會遇到信號與噪聲問題,從而導(dǎo)致所謂CD偏差的問題。為了解決這個問題,F(xiàn)ractilia有一個能夠測量LER和通孔失效的軟件工具。該工具可以把CD-SEM的誤差和光刻特征圖形區(qū)分開。

對于EUV計(jì)量,光學(xué)CD(OCD)是另一種可能性。 然后,芯片制造商還必須使用晶圓檢測工具(如明視野)來定位缺陷。KLA-Tencor公司全球客戶參與高級總監(jiān)Neeraj Khanna表示:“對于EUV來說,缺陷更加隨機(jī),這是一個巨大的挑戰(zhàn)。”

一旦芯片制造商深入了解了計(jì)量/檢驗(yàn)數(shù)據(jù),他們就可以調(diào)整晶圓廠工具上的可調(diào)工藝參數(shù)來處理EUV隨機(jī)性。然而,這并不那么簡單。Khanna表示:“所有這一切都需要更多的過程控制,其中很多都要回到基本的產(chǎn)量控制上。如果你只在一個過程中控制它,比如光刻,那將是非常困難的。今天,我們有光刻、蝕刻、CMP和一個非常閉環(huán)的反饋通道。”

與任何工藝一樣,芯片制造商必須使工具在晶圓廠中協(xié)同工作。但由于EUV隨機(jī)效應(yīng),芯片制造商可能會遇到新的復(fù)雜數(shù)據(jù)的爆炸式增長。ASML有一個解決方案。ASML的Lercel表示:“這是我們添加的整體光刻技術(shù)的關(guān)鍵部分。這可以確保我們擁有計(jì)量方法,確保我們與蝕刻公司有良好的合作關(guān)系,并確保我們是否能夠獲得足夠的計(jì)量數(shù)據(jù)來執(zhí)行正確的工藝閉環(huán)控制。這就是我們認(rèn)為需要共同努力才能取得成功的原因。如果你可以一起優(yōu)化所有這些部件,你就能最終達(dá)到你所需要的邊緣放置誤差容限EPE。”

晶圓廠有很多不同的工具,但可能還不夠。因此,芯片制造商要求他們的計(jì)量和其他工具供應(yīng)商一起工作,并幫助整理數(shù)據(jù)。據(jù)一家芯片制造商稱:“目前還不清楚將如何工作,因?yàn)闆]有開放的框架可以做到這一點(diǎn)。”

不過,行業(yè)必須合作。否則,隨著更多的隨機(jī)效應(yīng)需要處理,EUV的引入可能會變得更困難。

-

晶圓

+關(guān)注

關(guān)注

52文章

4890瀏覽量

127934 -

晶體管

+關(guān)注

關(guān)注

77文章

9682瀏覽量

138084 -

EUV

+關(guān)注

關(guān)注

8文章

605瀏覽量

86005

發(fā)布評論請先 登錄

相關(guān)推薦

日本首臺EUV光刻機(jī)就位

RJ45連接速度與性能分析 RJ45插頭的類型及其應(yīng)用

JDSU Xgig1000 12G SAS/SATA 分析儀應(yīng)對高速串行總線挑戰(zhàn)的理想平臺

使用Arthas火焰圖工具的Java應(yīng)用性能分析和優(yōu)化經(jīng)驗(yàn)

智能駕駛的挑戰(zhàn)與機(jī)遇

灌區(qū)信息化面臨的挑戰(zhàn)分析

晶閘管與IGBT的性能分析

日本大學(xué)研發(fā)出新極紫外(EUV)光刻技術(shù)

臺積電A16制程采用EUV光刻機(jī),2026年下半年量產(chǎn)

高端性能封裝技術(shù)的某些特點(diǎn)與挑戰(zhàn)

如何獲得高純度的EUV光源?EUVL光源濾波系統(tǒng)的主流技術(shù)方案分析

ASML為什么能在EUV領(lǐng)域獲勝?

關(guān)于EUV的性能分析和挑戰(zhàn)

關(guān)于EUV的性能分析和挑戰(zhàn)

評論