芯片制造商已經在基于 10nm 和/或 7nm finFET 準備他們的下一代技術了,但我們仍然還不清楚 finFET 還能堅持多長時間、用于高端設備的 10nm 和 7nm 節點還能延展多久以及接下來會如何。

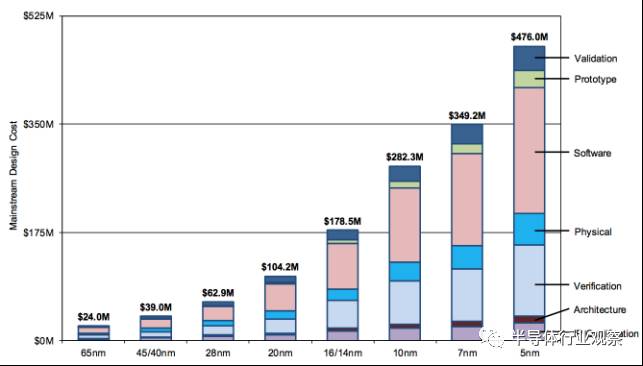

在 5nm、3nm 以及更小節點,半導體行業還面臨著巨大的不確定性和許多難題。即使在今天,隨著每個節點的工藝復雜度和成本的上升,傳統的芯片尺寸縮減也在放緩。因此,能夠負擔先進節點芯片設計的客戶越來越少。

理論上,正如英特爾所定義的那樣,finFET 有望延展到 5nm 節點。(一個完整延展的 5nm 工藝大致相當于代工廠的 3nm)。不管這些讓人困惑的節點名稱是啥,finFET 很可能將在 fin 寬度達到 5nm 時壽終正寢。所以在 5nm 或更先進的節點,芯片制造商將需要一種新的解決方案。否則傳統的芯片縮放將會放緩或完全停滯。

一段時間以來,芯片制造商已經為 5nm 及以后節點探索了各種各樣的晶體管。到目前為止,僅有三星提供過細節。在 5 月份,該公司推出了自己的技術路線圖,其中包括在 2020 年之前實現一種 nanosheet FET。

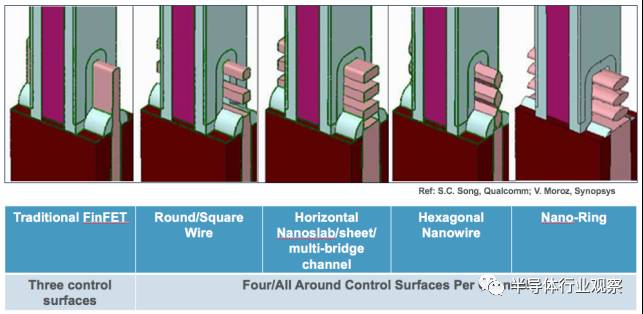

其它芯片制造商也傾向于同一時間框架內的相似結構,即使它們還沒有公開宣布它們的意圖計劃。 nanosheet FET 和其它變體、nanowire FET 都是屬于環繞柵極(gate-all-around)類別。其它變體還包括hexagonal FET、nano-ring FET 和 nanoslab FET。

圖 1:水平式環繞柵極架構的類型,來源:高通、 Synopsys、Applied Materials

目前來看,環繞柵極技術似乎是 finFET 之后最實用的技術。這是 finFET 之后的一步進化,它們具有很多同樣的工藝步驟和工具。有一種橫向環繞柵極技術基本上就是一個被柵極包裹著的側向 finFET。細小的線或片用作信道。

另外還有其它晶體管選項。一些芯片制造商甚至尋求使用先進的封裝技術來進行擴展。供應商正在權衡各種選擇以及尋求每種方法的技術價值和經濟價值。“finFET 還能延展一兩代,”英特爾一位資深研究員和工藝架構與集成總監 Mark Bohr 說,“但問題可能在于‘其中一種替代技術是更好的選擇嗎,它是否是環繞柵極的、III-V 族材料或隧道 FET?’如果我們不得不這樣做,我們可以擴展 finFET。但問題在于‘還有更好的選擇嗎?’”

所謂的 III-V 族材料,Bohr 是指通道中使用 III-V 族材料的 finFET,這可以極大提升器件中的遷移率。隧道 FET(TFET)是一種陡峭次閾值斜率器件(steep sub-threshold slope device),可以在很低的電壓下運行。

盡管環繞柵極技術氣勢正盛,但并不是每個人都會選擇它——至少目前還沒有。“我不一定贊同那一點,但它確實贏得了很多關注。”Bohr 在一次采訪中表示,“現在就預測哪種技術會成功還為時尚早。但現在已經有足夠多的好想法能確保還能再多續幾代。”

但是,分析師相信 10nm/7nm finFET 還將在可預見的未來里持續。International Business Strategies(IBS)首席執行官 Handel Jones 說:“(finFET 提供了)更高性能、更低功耗和更低成本的組合。”

如果下一代晶體管在 5nm 或以后節點投入生產,那么這項技術將會非常昂貴且會受限于特定的應用。Jones 說:“很可能會采用環繞柵極,但主要的好處在于高性能。”據 IBS 報告稱,在 5nm 節點將需要花費 4.76 億美元來設計一款主流芯片,相較而言,在 7nm 節點為 3.492 億美元,在 28nm 節點為 6290 萬美元。

圖 2:IC 設計成本,來自 IBS

為了幫助客戶取得領先,Semiconductor Engineering 已經預先估計了未來的狀況并突出強調了其中的難點工藝步驟。

不同的選擇

未來至少有三條主要路徑——暴力縮減尺寸、停留在成熟節點和先進封裝。

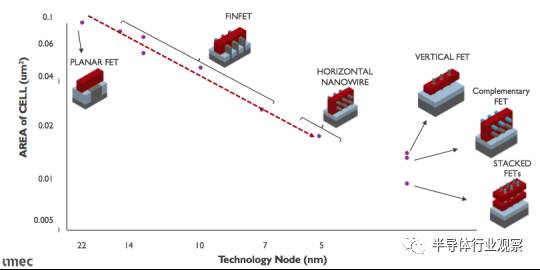

那些資金充足的公司很可能繼續推進傳統的尺寸縮減,實現 10/7nm 及以后節點。環繞柵極技術是 finFET 之后的領先者,至少目前來說是這樣。更長期來看,還有其它選擇,比如 III-V 族 finFET、互補式 FET(CFET)、TFET 和垂直納米線(vertical nanowires)。垂直納米線涉及到以垂直的方式對線進行堆疊。

CFET 是一種更加復雜的環繞柵極技術,其中 nFET 和 pFET 線堆疊在彼此之上。當前的環繞柵極器件只堆疊一種類型的線,不管是 nFET 還是 pFET。

CFET、TFET 和垂直納米線是更具變革性的技術,預計在短期內無法實現。它們將需要新的突破。

圖 3:后幾代晶體管架構,來自 Imec/ISS.

所以高端玩家會怎么做?GlobalFoundries 首席技術官 Gary Patton 說:“7nm 將是一個長壽的節點。finFET 還有很長的路要走。finFET 仍然還有很大的擴展空間。”

在 finFET 之后,研發方面存在多種選擇。比如 GlobalFoundries 正在探索納米片、納米線和垂直納米線。

對于一項技術的決策和時機選擇取決于各種技術和經濟因素。“你要努力開發一種能夠生產并能提供價值主張(value proposition)的工藝。”Patton 說,“這種事已經不如以往那樣直觀了。而需要遠遠更多的審查核驗。”

事實上,一項技術可能會持續處于研發階段十年之久。然后根據一系列指標,最好的技術上市,其它技術則為之崩猝。

但是可以確定,并非所有公司都會需要 finFET 和納米線。大部分都會停留在 22nm 平面工藝或以上的節點。許多公司無力承擔 finFET,而且模擬和射頻等器件也不需要這種技術。

“10nm、7nm 和 5nm 聽起來很誘人。”聯華電子公司(UMC)業務管理副總裁Walter Ng 說,“但有多少公司能真正負擔得起并且把設計和制造費用賺回來?只有少數幾家才能真正做到需求推動前沿。”

但那些處于 22nm 及更高節點的公司也面臨著一些挑戰。“其它每家公司都需要了解它們可以怎樣繼續競爭。”Ng 說,“他們正在努力尋找一種實現差異化和壓低成本的方式。”

所以很多公司轉向了先進封裝。所有芯片都需要 IC 封裝,比如說,客戶可以使用傳統的封裝,比如倒裝 BGA。先進封裝是這一思想的延展,在同一封裝集成多個 die 以創造高性能系統。2.5D/3D 和 fan-out 是這類方法的代表。

所以這一市場的最終贏家會是誰?Coventor 首席技術官 David Fried 說:“還沒有答案。人們確實還是尋找應用來推動實際的解決方案。”

Fired 指出并不存在一種適用于所有應用的解決方案。比如,finFET 或后續技術的晶體管可以用于高端微處理器。“但對于物聯網設備,這可能是個錯誤方向。”他說,“不存在一種能夠推動整個市場的單一應用。人們必須停止尋找一勞永逸的答案。很多不同的技術可以在同一時間都獲得成功,但它們針對的是不同的應用。”

Fried 預測說:“我猜想 7nm 似乎是相當具有變革性的。將會是 finFET。如果我們看到變成了 finFET 之外的其它技術,那可能是在 5nm 節點了。但要記住,橫向環繞柵極納米線器件(lateral gate-all-around nanowire device)就像是使用了 2 次額外蝕刻的 finFET。從 finFET 到橫向環繞柵極納米線器件是相當變革性的。我希望我們能在 5nm 節點時開始看到它。除此之外,我們并沒有太多可見性。”

晶體管趨勢和工藝

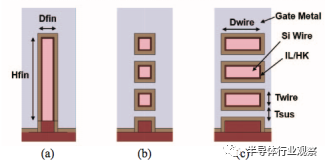

現在 finFET 是前沿的晶體管技術。在 finFET 中,對電流的控制是通過在 fin 的三個側面的每一個上實現一個柵極來實現的。

柵極間距(gate-pitch)是一個關鍵指標。英特爾 10nm finFET 技術的柵極間距是 54nm,14nm 技術的柵極間距是 70nm。(英特爾的 10nm 相當于代工廠的 7nm)。

當柵極間距接近 40nm 時,就需要重大決策了。根據 Imec 的仿真,finFET 開始接近 42nm 柵極間距了。Imec 半導體技術和系統執行副總裁 An Steegen 說:“納米線將會向下擴展并且仍然會有很好的靜電控制。”據 Imec 介紹,納米線 FET 已經在 36nm 柵極間距上表現出了很好的靜電控制能力。Imec 也已經設計出了一種直徑低至 9nm 的納米線。

圖 4:Imec 的微型納米線,來自 Imec

一般而言,環繞柵極可以提供比 finFET 更好的性能,但也存在一些難題,即驅動電流和寄生電容。將這些問題結合到一起的是一個相對新的層,被稱為 middle-of-line(MOL)。MOL 使用一系列接觸式結構將分離的晶體管和互連件連接起來。在 MOL 中,寄生電容是個問題。它會給器件的各個部分帶來外部電阻。這包括與低電阻肖特基勢壘和硅化物所在的結(junction)的接觸。

有一種版本是橫向納米線 FET,其中你是將一個 finFET 切成碎片,每一個碎片都變成一個微小的水平納米線,用作源極和漏極之間的通道。

其它常見變體還包括納米片(nanosheet)或納米板(nanoslab)FET。這兩種技術都類似于橫向納米線 FET,但線要寬和厚很多。

每一種變體都有各自的優勢劣勢。英特爾的 Bohr 說:“(納米片 FET)并不如聽起來那樣具有變革性。它只是側向放置的 finFET。不確定它是否有納米線那樣高的價值。”

在納米線 FET 中,環繞柵極整條線,可以實現對柵極的更好控制。Applied Materials 晶體管與互連組高級總監 Mike Chudzik 說:“正是這種改進過的柵極控制,使得你可以繼續延展柵極長度。”

正如前面說的那樣,finFET 被切割成了碎片。因此,器件上的表面積會減少。Chudzik 說:“你正在失去硅本身的紅利。我很肯定你能在截止電流上獲得好處,但在整體驅動電流上會出現缺憾。”

所以納米片 FET 也是合理的。他解釋說:“這就是你開始延長這些線的地方。你要獲得更大的驅動電流。此外,你也可以調整這些線或片的形狀來幫助降低電容。”

另一個被稱為 nano-ring FET 的版本也有類似的優勢。他說:“nano-ring 的整個思想實際上就是將片稍微擠壓到一起,這么做能夠有效地降低電容。”

第一款環繞柵極器件很可能將有三根線。但隨著時間的推進,芯片制造商將需要堆疊更多的線以提供更多性能。他說:“我們肯定不想引入一種只能持續一個節點的新器件架構。(所以我們的想法)是考慮堆疊更多納米板。但你不能只是不斷無限地堆疊通道,因為你會遇到大量同樣的寄生、電容和阻抗問題,正如你會在更高的 finFET 中遇到的那樣。”

作為未來的預兆,GlobalFoundries、IBM 和三星最近發表了一篇關于 5nm 和 3nm 節點納米片 FET 的論文;稱這項技術相比于 finFET,能在更小的 footprint 上得到更好的性能。

圖 5:(a) finFET、(b) 納米線 (c) 納米片的橫截面仿真圖,來自 IBM

對一些層使用極紫外(EUV)光刻技術,來自這三家公司的納米片 FET 有三個片或線。它有 12nm 的柵極長度、使用 5nm 硅通道的 44nm/48nm 接觸的 poly pitch。據該論文稱,nFET 有 75mV/decade 的亞閾值斜率(sub-threshold slope),而 pFET 的則為 85mV/decade。

在實驗室中,研究者堆疊了 3 層納米片,每一片厚度為 5nm,中間有 10nm 的間隔。他們使用片寬度為 15nm 到 45nm 的單堆疊納米片結構演示了逆變器和 SRAM。該論文稱:“相比于具有繼承于 finFET 的多個閾值和隔離解決方案的 extremely scaled finFET,它有更好的靜電性能和動態性能。所有這些優勢使得堆疊的納米片器件成為了一種非常有吸引力的 finFET 替代選擇,而且可以擴展到 5nm 及以后的器件節點,在圖案化策略方面的復雜度也更低。”

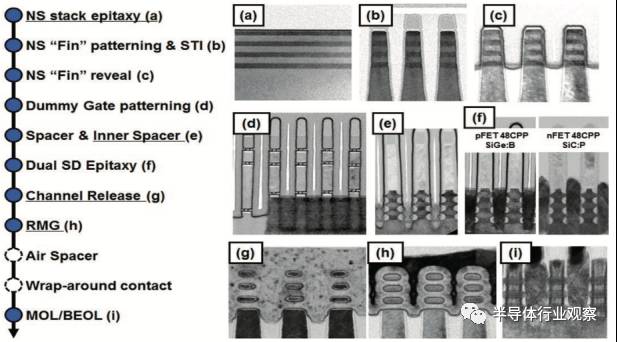

圖 6:堆疊的納米片工藝序列和 TEM,來自 IBM、Samsung、GlobalFoundries.

一般而言,環繞柵極和 finFET 的工藝步驟是類似的,只有一些例外。但這些例外使得環繞柵極技術具有了很大的挑戰性。圖案化、缺陷控制和變異性是其中的一些問題。

環繞柵極的第一步就不同于 finFET。在環繞柵極中,目標是使用一個外延反應器(epitaxial reactor)在基底上構建一個超晶格結構。這個超晶格由交替的硅鍺(SiGe)層和硅層構成。理想情況下,一個堆疊由 3 層 SiGe 和 3 層硅構成。

然后,就像 finFET 流程一樣,下一步涉及到淺溝槽隔離的形成。Applied Materials 的 Chudzik 說:“這個超晶格在硅鍺和硅之間有 ultra-abrupt 結是至關重要的。”

接下來是下一個關鍵步驟。在環繞柵極中,柵極不僅會圍繞通道,而且還會圍繞一些接觸區域。這會增加這個混合結構的電容。Chudzik 說:“所以你需要形成所謂的 inner spacer,這里你實際上是將高 k 區域和源極-漏極區域隔開。這可以通過 ALD 類型的薄膜完成。”

然后,使用一種替換工藝從這個超晶格結構中移除 SiGe 層。這會留下硅層和它們之間的間隔。每一個硅層都是納米線的基礎。

掩模/光刻難題

在這個工藝流程中,還有一系列光刻步驟。在 16nm/14nm 和 10nm/7nm 節點,芯片制造商使用的是今天的 193nm 浸沒式光刻工具和多重圖案化。

在 7nm 和/或 5nm 節點,半導體行業希望加入 EUV。在 EUV 中,電源將等離子體轉換成13.5nm 波長的光,從而在芯片上實現更精細的特征。

芯片制造商希望為最困難的部分加入 EUV,即 metal1 和通孔。在其它許多步驟,還將繼續使用傳統的光刻技術。

據 ASML 報道,與三重圖案化相比,EUV 可以將金屬線的成本降低 9%,將通孔的成本降低 28%。ASML 產品營銷總監 Michael Lercel 說:“(EUV)可以消除晶圓廠的步驟。如果考慮執行多次浸沒式光刻步驟的成本,再加上其他工藝步驟(如清潔和計量)的成本,我們相信相比于三重圖案化浸沒式和肯定的四重圖案化等等,EUV 每層的成本更低。”

但目前 EUV 還不足以用于生產。ASML 正在準備其最新的 EUV 掃描機 NXE:3400B。起初這款工具配置了一個 140W 的電源,可以實現 100 片晶圓/每小時(wph)的吞吐量。

為了將 EUV 投入生產,芯片制造商需要 250W 的功率,實現 125 wph 的吞吐量。ASML 最近已經開發出了一款 250W 電源,將在明年年初出貨。

與此同時,EUV 抗蝕劑是另一個絆腳石。為了讓 EUV 達到所需的吞吐量,行業需要 20mJ/cm2 劑量的抗蝕劑。“好的成像似乎需要更多,現在達到了 30mJ/cm2 到 40mJ/cm2 的范圍。”Lam Research 技術管理總監 Richard Wise 說,“所以為了我們希望達到的目標,劑量不是必需的。”

比如,據分析師稱,在 30mJ/cm2 劑量下,250W 電源的 EUV 掃描機的吞吐量是 90 wph,這低于所需的 125wph 目標。

但是開發所需劑量的抗蝕劑難度很大。Wise 說:“要降低劑量,存在大量的基礎物理難題,因為 EUV 存在隨機效應。”

這涉及到一種被稱為光子散粒噪聲(photon shot noise)的現象。光子是光的基本粒子。在圖案化的過程中,光子數量的變化會影響 EUV 抗蝕劑。它可能導致出現我們不想要的線邊緣粗糙度(LER)——LER 的定義是理想形狀上特征邊緣的偏差。

在行業攻堅抗蝕劑的同時,光掩模制造商也正在開發 EUV 掩模。今天的光掩模由一個在玻璃基底上的不透明鉻層組成。而 EUV 掩模則是一種反射技術,由基底上交替的硅層和鉬層組成。

“我們需要 EUV 來避開三重圖案化。”D2S 首席執行官 Aki Fujimura,“這意味著 EUV 掩模將會有比 ArF 掩模多很多的主特征,而且其中每一個特征都會很小。由于 EUV 能更準確地反映晶圓上的掩模偏差,所以 EUV 掩模需要印刷更多更小的結構,且每一個都要更準確。”

要生產 EUV 掩模,光掩模制造商還需要一些新工具。比如他們需要更快的電子束掩模寫入器。隨著掩模特征越來越復雜,今天的單束電子束工具需要更長的時間來圖案化或寫入掩模。今天的電子束基于可變形束(VSB)技術。

這個問題的解決方案是多束掩模寫入器,今天已有 IMS 在提供多束掩模寫入器了,可用于光掩模和 EUV 掩模,而 NuFlare 也正在開發多束工具。

多束有助于改善掩模產量、周轉時間和成本。Fujimura 說:“世界上大多數掩模仍然可以完美地使用 VSB 寫入器制造,但關鍵的少數將需要多束寫入,從而保證合理的寫入時間。”

他說:“最可能的情況是 EUV 將在 5nm 節點時就緒,一些掩模層將會有很高的多束寫入需求。比如,如果一個掩模層包含大量非正交、非 45 度的特征,那么肯定會需要多束。193i 無法看到掩模上的小擾動,所以在有相對大的步進大小時,這些圖案的‘曼哈頓化(Manhattanization)’效果良好。但是 EUV 可以做到更好,這會極大地增加發射數量,使得 VSB 寫入不太可能實現。但這些是針對特定芯片的非常專門的掩模。對于絕大多數掩模層,盡管掩模上的主特征的數量會倍數式地暴增,但用來描繪裝飾圖案和 SRAF 的發射的數量卻將大幅減少。具有足夠精度的先進 VSB 寫入器可能足以用于大多數 EUV 掩模了。”

檢測/計量難題

在 5nm 及以后節點,檢測和計量也是一大關鍵。“向垂直架構發展的趨勢帶來了缺陷隱藏的檢測難題和描述復雜的計量難題。”KLA-Tencor 客戶參與高級總監 Neeraj Khanna 說,“在這些節點,EUV 會被大量采用,這會推動新的隨機和系統性的缺陷機制。隨機問題將會帶來對更高采樣率的需求。”

這意味著什么?Khanna 說:“我們預計這些新架構會帶來對檢測和計量的新需求。這個行業必須不斷創新和拓展核心技術。”

-

芯片

+關注

關注

455文章

50732瀏覽量

423257 -

集成電路

+關注

關注

5387文章

11536瀏覽量

361663 -

晶體管

+關注

關注

77文章

9684瀏覽量

138102

發布評論請先 登錄

相關推薦

語音集成電路有哪些特點

網關和路由器的對比分析

集成電路的封裝形式介紹

關于FinFET與集成電路的對比分析介紹

關于FinFET與集成電路的對比分析介紹

評論