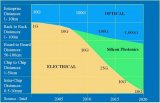

2006年前英特爾高級(jí)副總裁帕特·基爾辛格說(shuō):“今天,光學(xué)是一個(gè)非常小的細(xì)分技術(shù),明天,它將成為我們制造每一個(gè)芯片的主流。” 事實(shí)上,光互連對(duì)于內(nèi)部和數(shù)據(jù)中心之間的高速通信是非常重要的。

最近公司接觸的項(xiàng)目中,因?yàn)樗衅渌Χ寄芨叨燃稍谝粋€(gè)CMOS芯片上,外部只需要激光二極管。為了讓CMOS高速通信芯片和激光二極管之間實(shí)現(xiàn)高速通信,片上ESD(靜電保護(hù))保護(hù)的寄生電容必須盡可能的小。在過(guò)去5年當(dāng)中,公司在不同的光互聯(lián)項(xiàng)目中,一直使用公司自創(chuàng)的TAKE CHARGE 工具,得到了很好的結(jié)果。當(dāng)通用的或者半導(dǎo)體廠的在片ESD不符合您的需求時(shí),采用公司的TAKE CHARGE是非常理智的選擇。因?yàn)椋琓AKE CHARGE在數(shù)千個(gè)IC商業(yè)應(yīng)用芯片上已經(jīng)證明,它能提供一個(gè)快速,可靠的方式來(lái)平衡ESD保護(hù)與成本之間的關(guān)系,同時(shí)發(fā)揮最大的IC性能。

設(shè)計(jì)無(wú)約束

保護(hù)接口與最敏感的節(jié)點(diǎn),如GATE,核心器件等

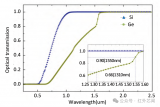

高速電路的低寄生電容

200fF,100fF甚至低于15fF

縮短幾個(gè)月量產(chǎn)和上市的時(shí)間

現(xiàn)有低寄生電容可用的on-chip ESD 解決方案ESD

TSMC: 180nm down to 28nm

UMC: 130nm, 65nm, 28nm

GF: 65nm

SMIC: 40nm

Several other foundries, …

針對(duì)其他技術(shù)節(jié)點(diǎn)或者半導(dǎo)體廠的私人定制EOS / ESD解決方案,可在幾天內(nèi)交貨

大幅降低IC成本

已經(jīng)在硅產(chǎn)品上被證明的ESD解決方案有助于降低IC開發(fā)成本和時(shí)

兼容所有的標(biāo)準(zhǔn)工藝流程

已經(jīng)和歐洲,美國(guó)的大客戶在光互連項(xiàng)目方面取得很多合作和經(jīng)驗(yàn)

公司所有合作的客戶:

如果你在硅光電這塊或者高速電路這塊有涉足,那么公司的on-chip ESD 解決方案,會(huì)給貴公司產(chǎn)品帶來(lái)更多的附加價(jià)值。

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27290瀏覽量

218090 -

硅光電

+關(guān)注

關(guān)注

0文章

5瀏覽量

7433 -

高速電路

+關(guān)注

關(guān)注

8文章

157瀏覽量

24240

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

集成電路電磁兼容性及應(yīng)對(duì)措施相關(guān)分析(一) 電子系統(tǒng)性能要求與ESD問(wèn)題

硅光電池板是由超導(dǎo)材料制成的嗎

硅光電池板是由什么材料制成的

硅光電池板是半導(dǎo)體還是超導(dǎo)體

Chip天線相比較其他天線的優(yōu)勢(shì)有哪些?

IEC ESD性能的ESD401 1通道ESD保護(hù)二極管數(shù)據(jù)表

光電探測(cè)器和硅光電池一樣嗎?

硅基鍺PIN光電探測(cè)器的研究進(jìn)展綜述

ESD的3種模型和RF PA ESD保護(hù)方案介紹

硅基光電子工藝中集成鍺探測(cè)器的工藝挑戰(zhàn)與解決方法簡(jiǎn)介

硅光電池測(cè)量光照強(qiáng)度

FPGA設(shè)計(jì)關(guān)于功耗專業(yè)的術(shù)語(yǔ)解析

什么是CHIP

關(guān)于光纖通信的ESD保護(hù)

關(guān)于硅光電應(yīng)用下的on-chip ESD的性能分析和介紹

關(guān)于硅光電應(yīng)用下的on-chip ESD的性能分析和介紹

評(píng)論