在說明差分對布線重要性之前,首先了解影響傳輸線阻抗因素:走線線寬、線長、線厚、側壁形狀、阻焊層覆蓋范圍和傳輸線介質是明顯的影響因素。而介電常數和介質厚度也會影響傳輸線阻抗精度,具體計算公式請參考信號完整性分析相關書籍。知道這些影響因素,可以幫助我們設計出好的走線,特別是在需要明確走線阻抗的時候,通過相關的軟件來調整走線寬度和厚度等都可以完成固定阻抗的走線。

差分對,之所以是叫差分對,是因為它上面?zhèn)魉偷男盘柕扔趦蓚€互補并且彼此互為參考的信號之間的差值,因此可以極大地降低外部對其的干擾。

差分對的布線方式應該要適當的靠近且平行。所謂適當的靠近是因為這間距會影響到差分阻抗(differential impedance)的值,此值是設計差分對的重要參數。需要平行走線。

在電路設計中,如果所有的信號線都采用單端線,做好了阻抗設計,一般情況下系統(tǒng)是可以正常工作的,一旦信號線兩端的地電位不同,甚至差距比較大,則會引起系統(tǒng)不能正常工作,而采用差分對布線或者走線是一種有效的解決方法。因為差分線具有等長,等阻抗,經過近似相同的環(huán)境,這在穩(wěn)定信號上有著先天的優(yōu)勢。

在原理圖設計中,差分信號通常以“_N”和“_P”作為后輟進行標記,差分線可以有效解決信號源和負載之間沒有良好的參考地連,可抑制電子產品的干擾和減小信號線對外產生的電磁干擾(EMI)。

那么,為什么差分線能有效的消除噪聲呢?首先我們看下在布差分線時的常規(guī)要求:差分線在設計時要保證兩條線的長度相等,通常在5%之內。兩條差分線之間有3w的距離和差分線周圍包地都是很好的設計經驗。

這樣,一方面,差分線的兩條信號線產生的磁場相互抵消,以此降低EMI;另一方面,差分對信號線假如同時引入外部噪聲干擾信號,因為取其差分結果,這樣可以很好的消去噪聲,這與經典的三運放放大器有著異曲同工之妙。

在繪制PCB差分對的走線時,盡量在同一層進行布線,差分對走線換層會由于增加了過孔,會引入阻抗的不連續(xù)。

其次,若換層還會使回路電流沒有一個好的低阻抗回路,會存在RF回路,若差分對較長,那么共模的RF能量就會產生影響了。

還有一個原因是差分對在不同板層之間有不同的信號傳輸速度,在信號完整性分析相關資料中都能看到信號在微帶線上傳輸比帶狀線快,這也會引起一定的時間延時。

在連接方面,還要注意差分對的連接問題,如果負載不是直接負載而是有容性負載,那么可能會引入EMI。在電路設計方面也需要注意終端的阻抗匹配,防止發(fā)送反射而引入EMI問題。

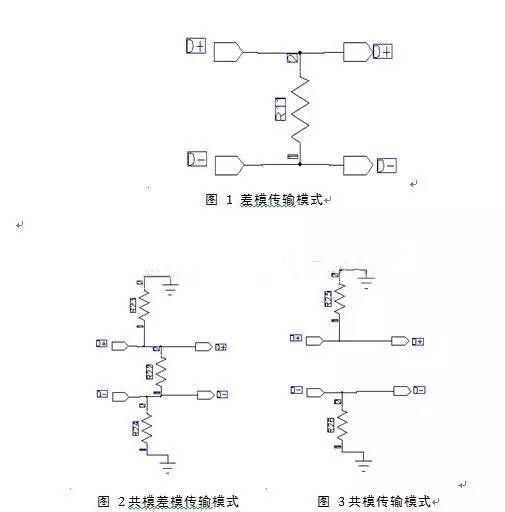

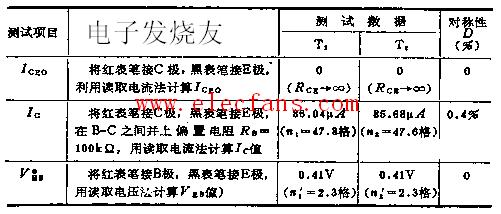

關于終端阻抗匹配,差分信號傳輸我們通常采用差模模式,還有一種傳輸模式是共模模式。其終端電阻配對參考設計如下所示

匹配電阻的大小通常用阻抗分析儀進行測量和標定。

對于我們常用的差模終端匹配電阻,通常選用50歐姆或者100歐姆進行,實際中也需要進一步的匹配。由于差模模式傳輸的信號是相互間的參考而與地無關,因此沒有了共模的RF能量。也可以在設計初定為共模差模模式,在后期調試過程中采用不同的模式進行比較,這也不失為一種好方法。

-

電阻

+關注

關注

86文章

5507瀏覽量

171931 -

介電常數

+關注

關注

1文章

108瀏覽量

18429 -

差分對

+關注

關注

0文章

9瀏覽量

6850

發(fā)布評論請先 登錄

相關推薦

【AD問答 9】如何設置差分對

請教各位大神, allegro 差分對與差分對之間的間距如何設置?

設置差分對的方法

如何在PADS中創(chuàng)建差分對

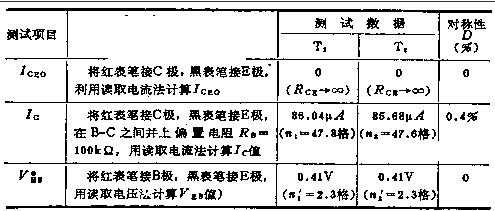

檢測差分對管的方法有哪些

探討繪制性能良好的差分對的方法和步驟

探討繪制性能良好的差分對的方法和步驟

評論