電力傳輸網絡(PDN)是SOC中最重要的組件之一,因為它為設計中的所有組件供電。隨著設計復雜性的增加,分區方法越來越受歡迎,而功率門控有助于降低不斷增長的功耗。通過這些方法,設計變得更加高效,但是它們在PDN的設計方面引入了額外的問題和挑戰。

電網設計

使用的金屬在電網中,主要取決于設計的功率要求和技術節點中使用的金屬選項。更多的金屬選擇成本更高,但它創造了比較少金屬選項設計更強大的設計。電網中的金屬用量(寬度,間距和金屬堆疊)由電力需求定義。如果我們有更多的功率要求,那么在這種情況下我們必須使用更寬的金屬條紋用于網格。

應選擇金屬寬度,以免浪費路由軌道。有時,DRC規則也在決定電網金屬寬度方面發揮作用。讓我們看一下下面給出的DRC間距樣本表。

DRC間距規則取決于金屬寬度和寬度。也是在金屬的平行運行長度上。間隔表下方顯示間距如何隨所用金屬寬度而變化。如果我們采用W4μm的M4功率條寬度,則在這種情況下,與下一個寬度為w1μm的M4信號路徑(M4的最小金屬寬度)的間隔必須為“s3”。選擇M4寬度“w2”來照顧寬金屬規則,這樣我們就不會浪費附近的布線軌道。我們假設特定技術節點的路由網格為“x”μm,這可能因技術而異。

電網設計和模擬集成的挑戰

1。分區設計中的電源門控

對設計進行分區有助于將設計分解為更小的層次結構,這些層次結構可以單獨以更有效的方式處理。此外,對這些模塊中的一些進行電源門控可以顯著降低設計的總功率。但是對模塊進行電源控制會導致電網連續性中斷。因此,電源門控分區的最大缺點之一是核心網格面臨的IR丟棄問題。本討論專門針對基于引線鍵合的封裝(QFP,QFN,BGA等)。

我們可以最大限度地減少跌落的方法之一是使網格更強大。這需要定量地完成,因為它有自己的擁塞限制和模具面積的顯著增加。

第二種方法可以是通過電源門控模塊為核心電源提供饋通路徑,以便核心網格保持連續。

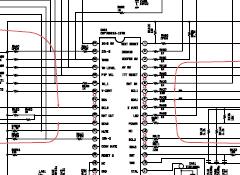

圖1:電源門控分區設計中的傳統電網

圖2:引入饋通路徑分區以維持核心網格連續性

2。分區和頂部之間的網格對齊(非功率門控分區)

分區和網格之間的核心網格對齊可能是一個棘手的迭代業務,特別是當大量的塊是參與其中。對于所有塊和頂部,始終建議對于金屬條紋具有共同的設定距離,寬度和間距。如果遵循這一點,則最終可以以幾微米的移動為代價來實現對準,同時將塊放置在芯片頂部上。

芯片頂部和塊級之間通常存在金屬共享。在這些情況下的對齊可以通過復制塊LEF中的塊內的網格來實現,使得頂部的網格可以在這里和那里以幾微米的移動容易地連接到這些塊銷。從一開始就始終建議在這方面采取干凈的方法。

圖3:頂部反映的塊電源引腳。

圖4:頂部電網連接到塊電源引腳

3。電源門控設計

低功耗模式是一種在不使用時通過關閉邏輯某些部分的電源來降低芯片總功耗的功能。電源開關通常用于為電源門控模塊提供電源。即使使用電源開關增加了集成的額外復雜性,包括芯片面積的影響,但在設計性能方面,它們是最好的。

與電源開關相關的一個問題是它的位置方面電源和電源門控模塊。我們將在下面討論設計中使用電源開關的一些例子。

CASE1:當通過控制芯片內部的電源開關來完成電源門控時。板載源始終為ON。

圖5:源鎮流器始終開啟時使用電源開關

在上面的圖5中,我們已經示出了如何在A點使用電源開關對可切換P1域進行電源門控。因此,A點的電壓控制整個芯片的電壓降。因此,開關A需要盡可能靠近電源放置。需要通過保持墊和點A之間的下降盡可能忽略來在A點建立整個網格。然而,這種方法容易在開關上產生電壓降,因此需要根據電流要求,開關提供的電阻和所用開關的大小來使用合適的開關。

CASE2:當通過關閉電路板電平來完成電源門控時。

圖6:使用電源開關鎮流器用于電源門控

在上圖中,電路板上的鎮流器被關閉以供電門電源域P1。低功率域P2(始終為開)連接到非常靠近電源板的電源開關,以創建并聯電網。

案例3:僅使用內部鎮流器時

圖7:僅為內部鎮流器使用電源開關

開關盡可能靠近內部穩壓器,以便為可切換電源供電域P1。

4。記憶方向

這是一種極為罕見的情況,與影響IR掉落和芯片功能的內存方向有關,但如果不加以處理,則可能非常關鍵。

我們在NPI中的記憶常常有不同的方向,在給定技術中,取決于存儲器的允許取向,在水平和垂直方向上具有存儲器電源引腳。

當從頂部金屬掉到存儲器引腳時,“addStripe”命令僅通過正交存儲器引腳丟棄。因此,當頂部金屬柵極和存儲器引腳在同一方向時,沒有過孔添加到存儲器引腳。如果沒有捕獲,這可能會非常危險。

圖8:存儲器電源引腳與電網正交

圖9:與電網方向相同的存儲器電源引腳

-

PCB打樣

+關注

關注

17文章

2968瀏覽量

21721 -

華強PCB

+關注

關注

8文章

1831瀏覽量

27779 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43062

發布評論請先 登錄

相關推薦

【送書福利】不懂PDN談何電源完整性?請收下這本PDN設計指導硬核書

哪些方法可以改善PDN對電源系統性能?

PDN 電源分配網絡設計步驟 PDN layout步驟

PDN設計的目的

Altium Designer PDN Analyze簡介

NEC FS2186PDN chassis彩電電路圖

PCB制造:PDN設計指南

PDN設計

利用Altium Designer自帶PDN Analyzer對電源平面進行PDN實例仿真分析,超經典!

PDN 元件對阻抗的影響

震旦ad330pdn

震旦ad330pdn

評論