逐次逼近寄存器(SAR)模數轉換器(ADC)通常用于需要中到高分辨率的應用中。 SAR ADC的主要優點是高性能,低功耗和小芯片面積。

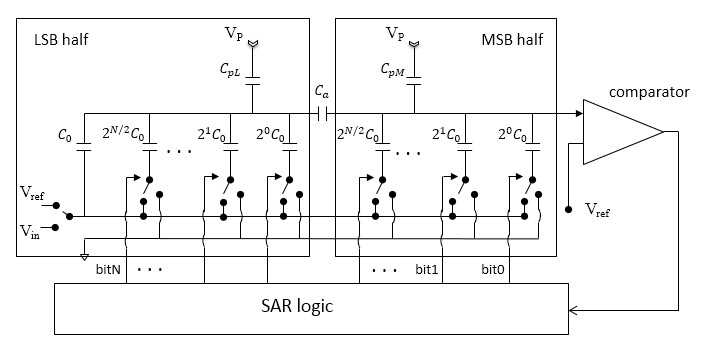

為了減小芯片面積,使用分離電容DAC陣列。該架構如圖1所示。分離電容陣列既可用作DAC,也可用作采樣保持電路。衰減器電容器C a用于將陣列分成兩個子陣列。在采樣階段之后,陣列輸出端的輸出電壓為V in - V ref ,其中V in是ADC輸入電壓,V ref 是參考電壓。在近似階段期間,輸出電壓達到V ref + V qe 的值,其中V qe 是量化誤差。導致該值的DAC輸入是轉換結果。但是有一些誤差源必須最小化。

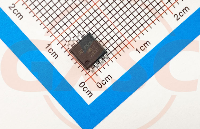

圖1:分離電容SAR ADC

2。誤差來源

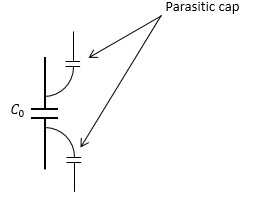

2.1寄生電容

在DAC的每個電容上陣列,上板和下板都有一些寄生帽。下板上的寄生電容對于SNR計算并不重要,因為它在逐次逼近過程中不參與電荷共享。寄生帽的價值取決于各種因素,如布局,制造工藝等;加上它隨著死亡而變化。

圖2:寄生帽

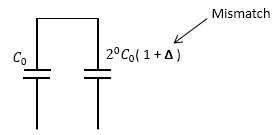

2.2電容不匹配

不可能在芯片上制作精確值的電容。與Parasitics一樣,不匹配也取決于布局和制造過程。圖3顯示了兩個電容,第二個電容應具有第一個雙倍值,但其值隨delta變化。通過適當的布局,可以實現低至0.1%的delta值。

圖3:不匹配

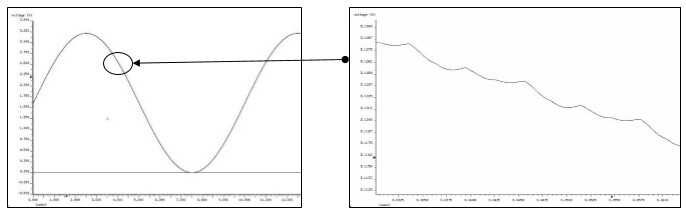

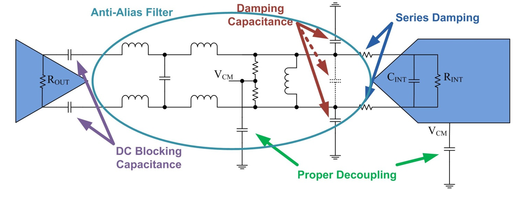

2.3來自附近網絡的耦合

如果輸入或參考電壓的相鄰網絡正在切換,那么它們可以耦合噪聲。圖4顯示了輸入正弦波;在放大的快照中可以看到與附近網絡的正弦波耦合的噪聲。

圖4:輸入噪聲

3。分析

為了研究各種因素對ADC信噪比的影響,采用了行為模型[2]。在每次模擬中,取出1024個正弦波樣本并將其轉換為12位數字值,然后計算SNR。進行了1000次這些模擬,最后得到了所有SNR值的RMS值。

DAC的輸出電壓可按如下方式計算:

其中C sumL是陣列的LSB一半的總電容,C sumM是MSB一半陣列的總電容。 N是DAC使用的位數, C 0是單位電容值, 等于陣列MSB一半的相應DAC位。

等于陣列MSB一半的相應DAC位。

運行SAR算法進行轉換,上面的方程用于通過切換找到V out 從MSB到LSB的逐位比特。

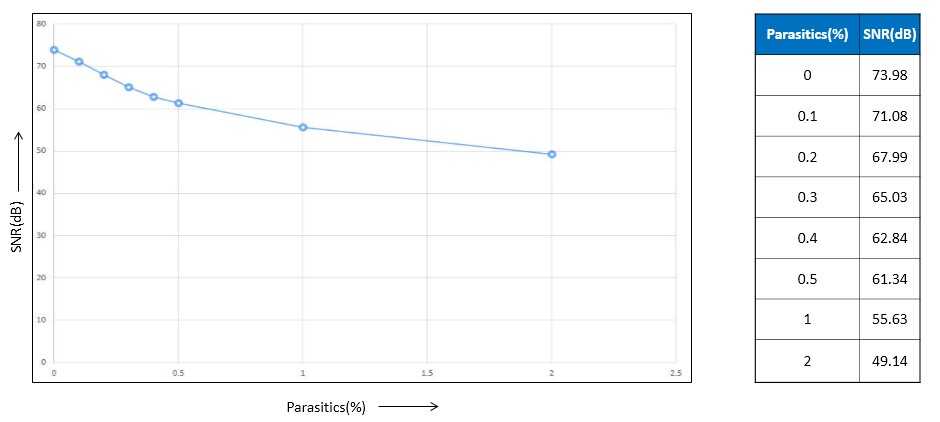

3.1寄生電容對SNR的影響

隨機值(介于0之間)在每次模擬中產生每個電容器的寄生電容的最大值(%)。進行1000次這樣的模擬,最后計算SNR的RMS值。圖5顯示了SNR隨寄生效應的變化,表中寄生值是寄生電容的最大可能值。我們可以看到只有0.2%的寄生電容可以導致6dB的SNR下降。

圖5:SNR與寄生效應

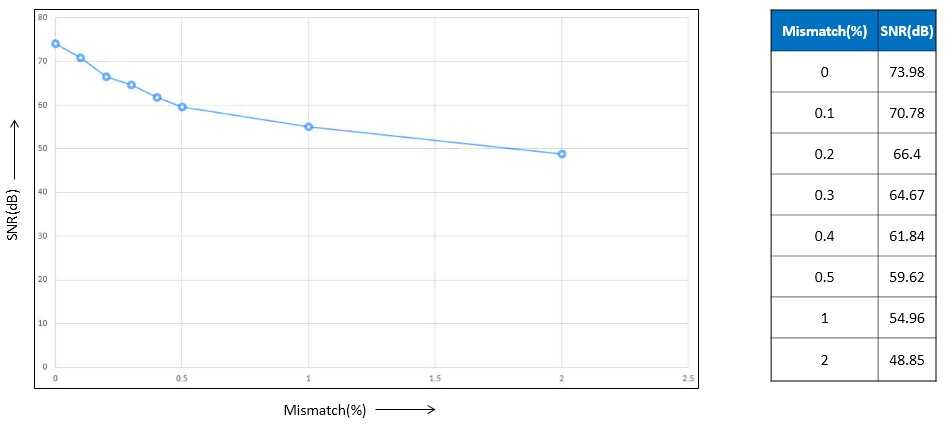

3.2不匹配的影響

這里也針對不同的最大不匹配值,為每個電容器生成隨機值,然后轉換完成。完成1000次這樣的轉換,最后計算SNR的RMS值。電容之間0.1%的不匹配會使SNR降低3.2 dB。

圖6:SNR與失配

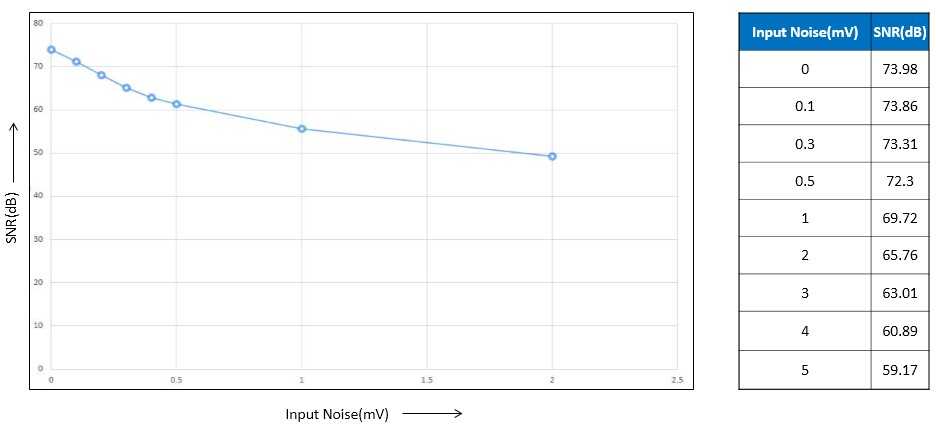

3.3耦合的影響

這里我們得到噪聲的隨機值(從0到最大值),它被加到輸入信號值上。對于每次轉換,有1024個樣本,因此每次轉換都會添加1024個不同的噪聲值,并完成1000次轉換,然后計算SNR的RMS值。

圖7:SNR與輸入噪聲

4。結論

上述分析表明,附近網絡耦合的電容,寄生電容或噪聲之間的小的不匹配會如何降低SAR ADC的性能。這種高靈敏度使得必須在布局階段正確匹配電容器,并在片上SAR算法中使用各種校準技術來提高其性能。屏蔽ADC網絡可以幫助避免噪聲耦合,這將再次有助于提高性能。

-

噪聲

+關注

關注

13文章

1142瀏覽量

48358 -

PCB打樣

+關注

關注

17文章

2978瀏覽量

22714 -

華強PCB

+關注

關注

8文章

1831瀏覽量

28730 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

44034

發布評論請先 登錄

XD08M3232紅外感應單片機擁有哪些配置實現高性能處理能力

卡套管的使用有助于提高效率并達到更合格的標準

燃料電池技術獲新突破 鉑鈷顆粒將有助于提高性能

質子傳導膜效率提高有助于氫燃料電池性能提高

技術資訊 I 面向電路的噪聲耦合抑制技術

評論