經(jīng)過(guò)兩年的初步研究,以及幾項(xiàng)正在申請(qǐng)的專利,去年夏天成立,加利福尼亞創(chuàng)業(yè)公司賽道種子父母和女兒聯(lián)合創(chuàng)始人鮑勃和蘇珊舒柏已經(jīng)開始對(duì)他們的深度子微米基于CMOS的模擬電路。

創(chuàng)始人將他們的關(guān)鍵發(fā)明,互補(bǔ)電流場(chǎng)效應(yīng)晶體管(CiFET)描述為充電模式模擬CMOS電路設(shè)計(jì),重點(diǎn)關(guān)注器件中的電荷。他們聲稱,新技術(shù)可以與數(shù)字工藝節(jié)點(diǎn)一起縮小,可能取代大多數(shù)附加模擬電路,并在任何節(jié)點(diǎn)上提供全混合信號(hào)SoC集成的圣杯。

兩位聯(lián)合創(chuàng)始人記錄了3階段CiFET前饋放大器產(chǎn)生20位線性度,并表示他們已經(jīng)在40nm芯片上使用幾個(gè)模擬模塊(包括放大器,ADC和PLL)證明了他們的設(shè)計(jì)方法,工作范圍可低于0.1V。這組作者說(shuō),這些電路以邏輯速度運(yùn)行,是自偏置的,不受參數(shù)變化的影響。不需要精密部件或匹配,電路可以顯示極高的功率噪聲抑制。

基本緩沖放大器設(shè)計(jì)

-

模擬電子

+關(guān)注

關(guān)注

58文章

660瀏覽量

81766 -

PCB打樣

+關(guān)注

關(guān)注

17文章

2968瀏覽量

21742 -

華強(qiáng)PCB

+關(guān)注

關(guān)注

8文章

1831瀏覽量

27810 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43087

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

CMOS模擬電路設(shè)計(jì)教材(11章)

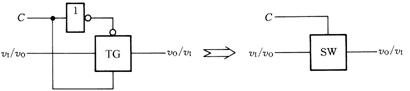

CMOS雙向模擬開關(guān)的電路結(jié)構(gòu)和符號(hào)

CMOS模擬開關(guān),CMOS模擬開關(guān)是什么意思

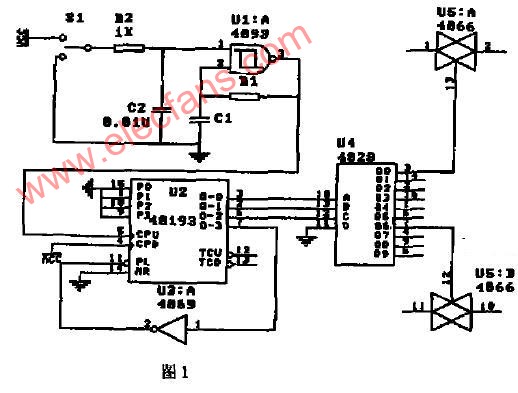

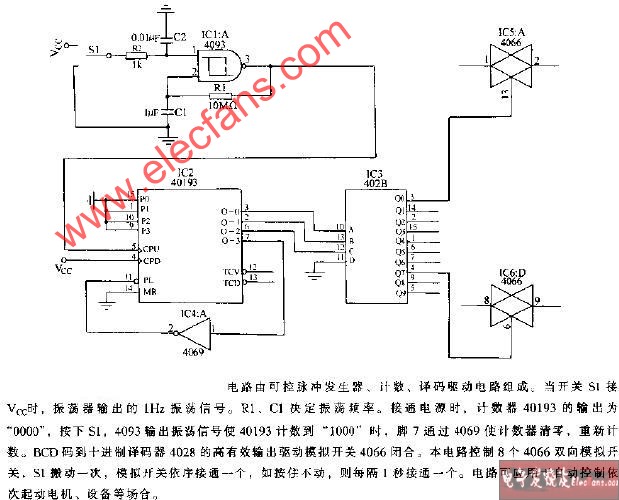

CMOS模擬開關(guān)控制電路的組成

充電模式模擬CMOS電路的設(shè)計(jì)

充電模式模擬CMOS電路的設(shè)計(jì)

評(píng)論