在整個電子行業(yè)中,芯片級的亞微米特征尺寸正在將封裝元件尺寸降低到早期技術(shù)的設(shè)計規(guī)則水平。今天的集成電路(IC)封裝技術(shù)必須提供更高的引腳數(shù),更小的引腳間距,最小的占位面積和顯著減小的體積,這導(dǎo)致半導(dǎo)體制造商開發(fā)小外形封裝(SOP),表面貼裝存儲器封裝。 SOP包裝通過消耗早期包裝替代品的三分之一至二分之一來支持小型化的趨勢。 SOP組件是手持式儀器,便攜式通信設(shè)備,筆記本電腦和筆記本電腦,磁盤驅(qū)動器以及眾多其他應(yīng)用的小巧外形的合理選擇。電源SOP(PSOP)封裝的機械尺寸與散熱熱質(zhì)量(銅塊)相結(jié)合,使其成為辦公自動化,工業(yè)控制,網(wǎng)絡(luò)和消費應(yīng)用的理想選擇,這些應(yīng)用會產(chǎn)生內(nèi)部熱量并承受壓力溫度條件。

PSOP引線位于封裝的長邊,使封裝的兩側(cè)敞開。封裝的開口側(cè)可用于在元件下方布線,節(jié)省電路板層并簡化電路板布局。與舊版本相比,封裝可以彼此更加靠近,也可以放置在電路板上的其他元件上。

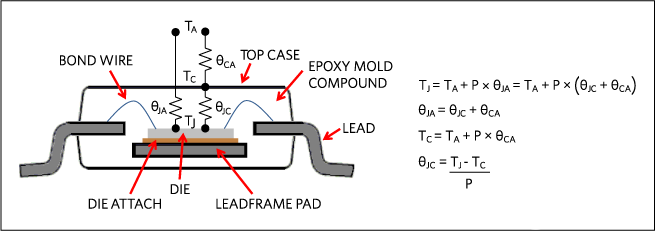

當IC封裝尺寸縮小時,熱功率密度增加,以及從芯片到外部環(huán)境的傳熱路徑需要進行優(yōu)化以在芯片上實現(xiàn)最大可能的功耗,同時仍確保芯片溫度低于最大允許值。盡管PSOP在溫度應(yīng)力,電流和可焊性下進行可靠性測試,以及在制造之前在制造商處進行機械檢查,但物理測試或設(shè)計測試板以測試封裝的所有可能性將是耗時且昂貴的。應(yīng)用和配置。

計算流體動力學(xué)(CFD)軟件在這種情況下非常有用,因為它可以模擬和估算IC在各種條件下連接到PCB時的結(jié)溫(Tj),包括不同的供電條件,電路板電導(dǎo)率,熱通孔分布,材料清單和IC封裝結(jié)構(gòu)本身。 CFD工具使機械或電氣工程師和/或IC設(shè)計人員能夠從熱管理的角度定性和定量地快速了解設(shè)計變更的影響。為了測試這一點,我們對ADI公司的計算熱分析進行了高分析。速度,高壓,1A輸出驅(qū)動放大器,ADA4870-1,PSOP安裝在PCB上,使用Mentor Graphic的CFD FloTHERM。具體而言,我們希望確定可以在芯片有源區(qū)域上消耗的最大功率,同時保持Tj低于150°C。我們研究了各種環(huán)境來估算這個最大功率,例如,改變電路板面積,增加散熱孔和安裝散熱器。

這個封裝可以安裝在電路板上,無論是向下壓還是向上壓(圖1) ,取決于形成的引線的方向。在嵌入式配置中,元件表面安裝在電路板的初級側(cè),銅嵌條焊接到電路板的頂側(cè)。在細長配置中,引線焊接到電路板的初級側(cè)。對于我們的實驗,我們使用了slug-down配置;首先沒有散熱器,然后散熱器連接到電路板的次級側(cè),電路板和散熱器底座之間有導(dǎo)熱油脂。

圖1:PSOP尺寸以毫米為單位,底部有銅塞。

對于CFD模擬,我們使用的測試板是六層板,尺寸為59 x 61 mm。我們假設(shè)每個導(dǎo)電層的銅覆蓋率均勻地涂抹在層的體積內(nèi)。基于此,我們基于單個層內(nèi)的銅覆蓋百分比計算每層的熱導(dǎo)率(k)作為體積平均值(表1)。為了進一步準確,我們還可以處理圖層中的銅覆蓋范圍,以在電路板平面內(nèi)提供電導(dǎo)率映射。

-

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

549瀏覽量

67992 -

PCB打樣

+關(guān)注

關(guān)注

17文章

2968瀏覽量

21721 -

華強PCB

+關(guān)注

關(guān)注

8文章

1831瀏覽量

27779 -

華強pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43063

發(fā)布評論請先 登錄

相關(guān)推薦

尋找SO-8封裝中M95256-W的結(jié)至環(huán)境熱阻

SSOP比SO的封裝怎樣

封裝/PCB系統(tǒng)設(shè)計需要進行熱分析

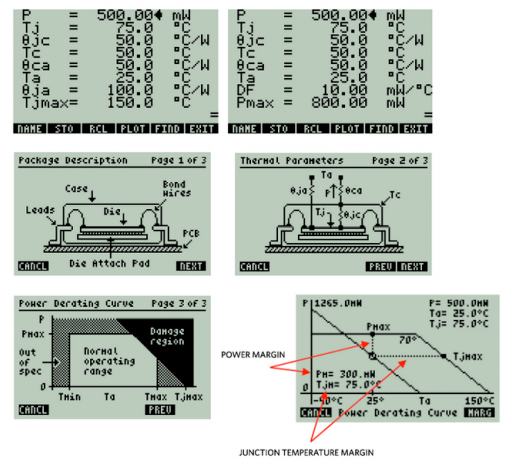

SO封裝技術(shù)的熱分析知識簡介

SO封裝技術(shù)的熱分析知識簡介

評論