無論高級(jí)靜態(tài)時(shí)序分析(STA)工具如何成型,運(yùn)行GLS仍然有很多優(yōu)勢,因?yàn)樗軌虬l(fā)現(xiàn)很多隱藏的設(shè)計(jì)問題,這些問題在RTL中很難找到模擬。它清晰地展示了設(shè)計(jì)在所需頻率下的行為方式,并確實(shí)存在實(shí)際延遲。因此,盡管GLS有其自身的一系列挑戰(zhàn)(例如設(shè)置問題,長時(shí)間運(yùn)行等),但它仍然是簽核過程的一部分,并且充當(dāng)了設(shè)計(jì)質(zhì)量的信心助推器。

JEDEC標(biāo)準(zhǔn)為DDR存儲(chǔ)器定義了許多時(shí)序參數(shù),需要遵循這些參數(shù)以確保正確操作。時(shí)序要求嚴(yán)格,需要謹(jǐn)慎實(shí)施。例如,數(shù)據(jù)選通信號(hào)(通常稱為DQS)的占空比要求約為45-55%;如果在寫入期間(存儲(chǔ)器控制器將選通信號(hào)驅(qū)動(dòng)到外部存儲(chǔ)器)或讀取(存儲(chǔ)器驅(qū)動(dòng)選通信號(hào)的位置)中違反此規(guī)范,則我們無法確保數(shù)據(jù)的健全性。物理實(shí)現(xiàn)本身就是一個(gè)挑戰(zhàn),因?yàn)樵O(shè)計(jì)人員必須注意各種時(shí)序參數(shù)沒有偏離標(biāo)準(zhǔn)。 DDR實(shí)施很困難,因?yàn)樗采婕霸S多自定義程序。因此,在DDR的情況下我們不能僅僅依靠STA工具,并且運(yùn)行GLS成為“必須”以確保設(shè)計(jì)的正確物理實(shí)現(xiàn)。運(yùn)行GLS for DDR接口具有挑戰(zhàn)性,因?yàn)樗婕案鞣N測試平臺(tái)設(shè)置問題,多個(gè)時(shí)序檢查,偏斜檢查,各種數(shù)據(jù)傳輸模式(突發(fā)長度-4,8),各種符合標(biāo)準(zhǔn)(如DDR3,DDR3L,LPDDR2等) 。)等等。

本文將嘗試強(qiáng)調(diào)通過運(yùn)行DDR的門級(jí)仿真可以找到的各種類型的問題,如何在設(shè)計(jì)中正確修復(fù)和實(shí)現(xiàn)它們以及應(yīng)該如何物理設(shè)計(jì)/STA團(tuán)隊(duì)可以避免此類問題。

DDR存儲(chǔ)器接口的門級(jí)仿真 - 示例問題,挑戰(zhàn)和解決方案

進(jìn)入DDR內(nèi)存控制器的時(shí)鐘占空比

進(jìn)入DDR控制器的時(shí)鐘質(zhì)量是一個(gè)重要參數(shù),因?yàn)榭刂破黩?qū)動(dòng)大多數(shù)信號(hào)(如DDR時(shí)鐘,數(shù)據(jù)選通等)都是從這個(gè)時(shí)鐘本身導(dǎo)出的。

具有DDR控制器的SoC的通用圖

進(jìn)入外部存儲(chǔ)器的時(shí)鐘占空比應(yīng)在47-53%的范圍內(nèi)。確保正確操作。如果占空比超出源本身(即進(jìn)入控制器的時(shí)鐘)的范圍,則必須看到時(shí)鐘的高周期和低周期之間存在巨大差異,這可能導(dǎo)致違反各種參數(shù),如tdqsh_min ,tdqsl_min等.STA對此進(jìn)行檢查,但是有任何錯(cuò)誤;不匹配可能導(dǎo)致寫入/讀取失敗。

WRITE的失敗看起來非常明顯,但這個(gè)問題也可能導(dǎo)致READ操作失敗!重要的是要知道在READ期間,由DDR存儲(chǔ)器驅(qū)動(dòng)的DQS內(nèi)部源自它接收的DDR時(shí)鐘。因此,如果存儲(chǔ)器正在獲得具有不良占空比的時(shí)鐘,則它在讀取期間生成的DQS可能違反讀取后同步周期(trpst)等規(guī)范。

因此,設(shè)計(jì)人員必須確保來自時(shí)鐘源(例如 - PLL)輸出到控制器輸入時(shí)鐘的輸入應(yīng)在時(shí)鐘的高低周期引入最小時(shí)滯。

讀取DQS門控問題

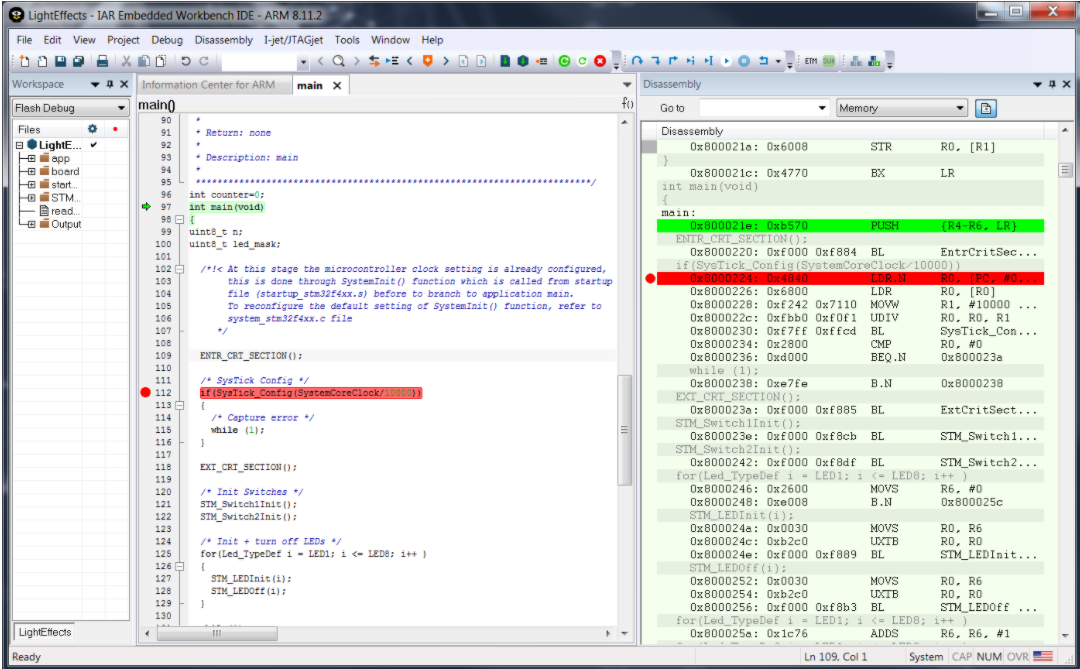

讀取DQS門控是一種功能,其中DQS被門控到控制器的讀取電路,直到讀取操作實(shí)際開始。這樣做是為了防止控制器的讀取FIFO損壞。讀取DQS門控在READ開始時(shí)禁用,并在讀取操作結(jié)束時(shí)再次啟用。見下面的例子:

第一個(gè)信號(hào)是門控讀取DQS信號(hào),第二個(gè)是來自PAD的非門控DQS信號(hào),n_52是讀取的使能信號(hào)DQS門控。從上面的波形可以清楚地看出,在讀取結(jié)束時(shí)延遲啟用讀取DQS選通導(dǎo)致在門控讀取DQS信號(hào)上捕獲“x”。

此外,由于它是異步事件,完成控制器的正確軟件編程,以便在正確的時(shí)間禁用讀取DQS門控。

如果讀取DQS門控與其他DQS相比遲到特定DQS字節(jié),則可能導(dǎo)致缺少該字節(jié)的完整讀取DQS脈沖。見下面的例子:

前4個(gè)信號(hào)對應(yīng)DQS0,后4個(gè)信號(hào)對應(yīng)DQS1。由于讀取DQS門控后來被DQS0禁用,因此導(dǎo)致完全錯(cuò)過一個(gè)DQS脈沖(“rd_dqs”有4個(gè)脈沖而“rd_dqs_gated”只有3個(gè))。另一方面,對于DQS1(低4個(gè)信號(hào)),DQS門控啟用/禁用正確發(fā)生。

因此,時(shí)序團(tuán)隊(duì)必須確保讀取DQS門控禁用信號(hào)的延遲對所有人來說都是相同的字節(jié)。對讀取前導(dǎo)碼應(yīng)該有讀取DQS門控解除斷言時(shí)間的時(shí)序檢查。

在未使用讀取DQS門控功能的情況下讀取電路損壞

如果未使用讀取DQS門控,則在DQS焊盤上使用下拉來保護(hù)讀取電路在寫入操作期間不被損壞。通常,在寫操作結(jié)束時(shí),DQS焊盤的輸出路徑被禁用,輸入路徑被啟用。但是,如果輸入路徑稍微提前啟用(在寫入結(jié)束時(shí)),則可能導(dǎo)致DQS焊盤輸入路徑上的“x”損壞,從而破壞控制器的讀取電路。因此,時(shí)序團(tuán)隊(duì)必須確保DQS焊盤的輸入路徑僅在寫入操作完成后才會(huì)啟用。

環(huán)回操作時(shí)的注意事項(xiàng)

在環(huán)回的情況下,沒有外部存儲(chǔ)器連接到SoC。數(shù)據(jù)從DDR焊盤循環(huán)回存儲(chǔ)在讀FIFO中。環(huán)回功能用于確保讀/寫路徑的正確操作,并可用于測試目的。在環(huán)回的情況下,每當(dāng)向控制器發(fā)送WRITE命令時(shí),它都啟用輸出路徑以及DQS焊盤的輸入路徑。但由于圖片延遲,數(shù)據(jù)末尾可能會(huì)出現(xiàn)爭用。時(shí)序團(tuán)隊(duì)必須確保DQS焊盤的“ibe”(焊盤的輸入路徑使能)的解除斷言僅在讀取電路完全捕獲數(shù)據(jù)時(shí)發(fā)生,否則可能導(dǎo)致輸入“x”損壞在環(huán)回期間讀取數(shù)據(jù)時(shí)DQS填充路徑或完全丟失數(shù)據(jù)。請參見下面的示例:

信號(hào)ipp_ibe_DDR0_DQS1是DQS1焊盤的輸入緩沖器使能,ipp_obe_DDR0_DQS1是輸出緩沖器使能。對于環(huán)回操作,兩者都是“1”。 DDR0_DQS1是焊盤信號(hào),ipp_do_DDR0_DQS1是焊盤的輸出路徑,ipp_ind_DDR0_DQS1是輸入路徑。由于ibe解除斷言比焊盤上數(shù)據(jù)的下降沿更早發(fā)生,因此導(dǎo)致焊盤輸入路徑損壞(ipp_ind_DDR0_DQS1變?yōu)椤皒”)。

PAD電平的微調(diào)和微調(diào)選項(xiàng)

DDR電極板有多種微調(diào)選項(xiàng) - 比如微調(diào)信號(hào)的占空比,控制信號(hào)的交叉點(diǎn)差分焊盤(DQS& CLK)的情況,控制焊盤輸出路徑的延遲等。但是,在GLS期間必須以最小的方式使用這些修整選項(xiàng),并且必須通過定時(shí)本身來滿足大多數(shù)條件。這很重要,因此我們在沒有任何修整松弛的情況下完全強(qiáng)調(diào)設(shè)計(jì)。

關(guān)注DDR內(nèi)存模型發(fā)出的各種時(shí)序違規(guī)行為

重要的是要審查GLS模擬中由DDR內(nèi)存模型發(fā)出信號(hào)的每個(gè)警告/錯(cuò)誤。當(dāng)實(shí)際延遲在GLS中出現(xiàn)時(shí),模型會(huì)響應(yīng)違反各種時(shí)序參數(shù)的情況,這些參數(shù)本質(zhì)上看起來微不足道,但重要的是讓它們得到解決。例如,WRITE突發(fā)操作的結(jié)束稱為寫后同步周期(twpst)。一般的理解是寫可累計(jì)周期應(yīng)大于twpst_min參數(shù)。但是,僅當(dāng)twpst_min小于tdqsl_min(最小DQS低周期)時(shí)才會(huì)出現(xiàn)這種情況。在dqsl_min> twpst的情況下,對于寫后同步周期應(yīng)該滿足tdqsl_min時(shí)間。通過這種方式,我們在實(shí)現(xiàn)中維護(hù)tdqsl_min和twpst_min參數(shù)。

-

DDR

+關(guān)注

關(guān)注

11文章

712瀏覽量

65397 -

仿真

+關(guān)注

關(guān)注

50文章

4099瀏覽量

133720 -

PCB打樣

+關(guān)注

關(guān)注

17文章

2968瀏覽量

21742 -

華強(qiáng)PCB

+關(guān)注

關(guān)注

8文章

1831瀏覽量

27811 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43088

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

電感元件的各種類型及其常見用法討論

三相異步電動(dòng)機(jī)加壓啟動(dòng)的各種類型

如何辨別各種類型的接口

主板的各種類型信號(hào)的基本走線要求

了解各種類型IC的封裝在PCB設(shè)計(jì)時(shí)準(zhǔn)確選擇IC

C51各種類型的大小

如何選擇各種類型逆變器電路中的MOS管

各種類型的混頻器及優(yōu)缺點(diǎn)

為電路設(shè)計(jì)執(zhí)行各種類型的SPICE仿真

運(yùn)行DDR的門級(jí)仿真可以找到的各種類型的問題

運(yùn)行DDR的門級(jí)仿真可以找到的各種類型的問題

評(píng)論