InnoLogic的新嵌入式符號處理器(ESP)工具使用符號模擬技術來減少檢查設計所需的功能仿真向量的數量(圖)。基于Verilog的ESP使用變量或符號,以及傳統EDA模擬器用于檢查設計的0,1,X和Z狀態。當符號模擬器找到符號輸入時,它會傳播布爾表達式而不是數字值。例如,使用ESP,您可以在一個周期內驗證具有16個輸入的ALU;傳統的模擬器需要64,000個輸入來驗證所有輸入組合。

您可以使用事件驅動的ESP-XV模擬器在行為級,RTL和門級進行Verilog設計的功能驗證。隨著仿真時間的縮短,基于ESP的仿真的測試平臺生成比傳統仿真簡單得多,因為您不必擔心大量的輸入組合。第二個工具ESP-CV是基于符號模擬技術的等價檢查器。該工具將Spice網表與Verilog模型進行了比較。 ESP-CV通過將Spice描述轉換為交換機級描述并使用用戶輸入符號將功能與Verilog模型的功能進行匹配來執行此任務。該工具對嵌入式存儲器非常有用,因為它允許您在一個周期內“繪制”內存并在一個額外周期內檢查結果。目前的ESP工具可以處理多達100萬門的設計。符號容量取決于設計;最壞情況電路,如乘法器,可以有大約50個符號,最佳情況電路,如存儲器,可以有幾千個符號。

使用符號工具而不是傳統工具進行功能驗證涉及限制。由于InnoLogic工具的運行速度比傳統模擬器快10倍,因此如果在模擬過程中使用四個或更多符號,則可獲得運行時優勢。您也不能使用任意數量的符號。當您添加符號時,模擬器所承載的布爾表達式變得復雜并開始消耗比計算平臺更多的內存。如果發生這種情況,ESP會將一些符號轉換為二進制值;你失去了覆蓋面,但模擬結束了。在Verilog仿真中不能使用帶有C參考模型的符號,因為C模型不能接受符號。最后,當前版本的ESP工具無法處理某些可編程邏輯接口,盡管InnoLogic計劃在其未來版本的工具中添加此功能。 ESP-XV和ESP-CV都在Unix下運行。這些工具的起始價格為100,000美元。

-

PCB打樣

+關注

關注

17文章

2968瀏覽量

21699 -

華強PCB

+關注

關注

8文章

1831瀏覽量

27749 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43036

發布評論請先 登錄

相關推薦

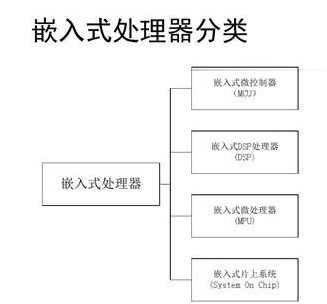

介紹幾種不同的嵌入式處理器

嵌入式處理器是什么

嵌入式處理器是什么

嵌入式處理器和數字信號處理器(DSP)選型指南

嵌入式系統教程之嵌入式處理器的詳細資料說明

嵌入式處理器

嵌入式處理器

InnoLogic的新嵌入式符號處理器工具介紹

InnoLogic的新嵌入式符號處理器工具介紹

評論