SAN JOSE - Xilinx公司正在通過提供一種技術(shù)使其基于Web的開發(fā)工具套件得到支持,該技術(shù)使系統(tǒng)設(shè)計(jì)人員能夠在其最先進(jìn)的FPGA之間即時(shí)創(chuàng)建高速接口。

稱為SelectLink,該工具自動(dòng)生成定制用于芯片間數(shù)據(jù)通道的Verilog源代碼和測(cè)試平臺(tái),支持多個(gè)引腳上每秒高達(dá)80千兆位的聚合帶寬。

SelectLink借鑒了Xilinx的Spartan-II,Virtex和Virtex E系列的標(biāo)準(zhǔn)功能,例如延遲鎖定環(huán)(DLL),Block RAM以及可編程SelectI/O和SelectI/O +技術(shù)。 Xilinx表示,SelectLink技術(shù)可用于創(chuàng)建一個(gè)系統(tǒng),每個(gè)引腳的吞吐量超過每秒311兆比特,總線寬度可達(dá)256個(gè)引腳。

SelectLink技術(shù)由兩個(gè)主要模塊組成。發(fā)送器模塊創(chuàng)建數(shù)據(jù)寬度轉(zhuǎn)換FIFO,其具有不同寬度的讀寫總線。據(jù)該公司稱,這提供了一種將數(shù)據(jù)從內(nèi)部總線匯集到更窄的外部總線的有效方法。

接收器模塊反轉(zhuǎn)發(fā)射器模塊執(zhí)行的漏斗和數(shù)據(jù)速率轉(zhuǎn)換,并執(zhí)行必要的數(shù)據(jù)移位,使其與信號(hào)時(shí)鐘對(duì)齊。

可從www.xilinx.com/applications/slcv/selectlink.htm

訪問SelectLink技術(shù)工具。

-

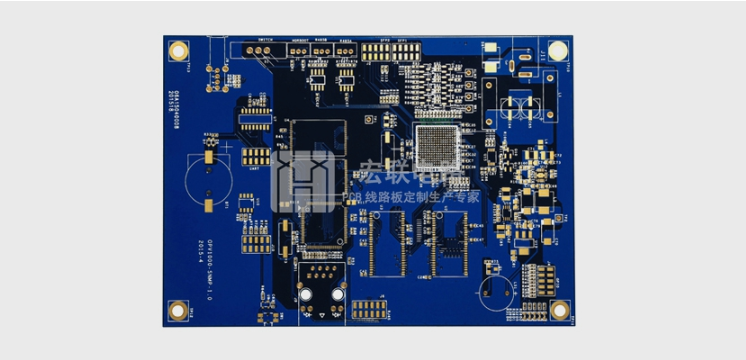

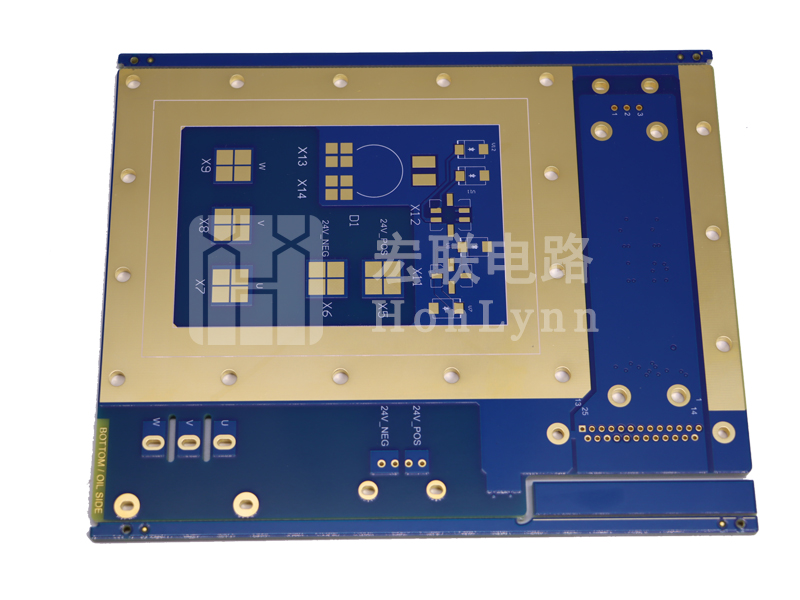

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43137

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

定制PCB線路板,這些注意事項(xiàng)你不可不知!

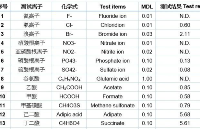

PCB線路板離子污染度的檢測(cè)技術(shù)與報(bào)告規(guī)范

線路板PCB工藝中的翹曲問題產(chǎn)生的原因

無鹵素PCB線路板具有的特殊特性

PCBA板與傳統(tǒng)線路板區(qū)別

PCB線路板的厚度對(duì)性能的影響

埋盲孔PCB線路板加工流程

高階HDI線路板跟普通線路板之間的差異

PCB線路板裸銅板:開啟高效電子時(shí)代的鑰匙

全球視野下的PCB線路板:技術(shù)革新引領(lǐng)產(chǎn)業(yè)變革

華強(qiáng)pcb線路板打樣Xilinx開發(fā)FPGA之間的高速鏈路介紹

華強(qiáng)pcb線路板打樣Xilinx開發(fā)FPGA之間的高速鏈路介紹

評(píng)論