RTC為整個電子系統提供時間基準,主控設計均離不開RTC電路設計,在應用RTC時,會出現精度或功耗大的現象,如何解決RTC精度及功耗問題?本文將為您介紹時鐘芯片應用問題及解決方法。

一、什么是RTC

實時時鐘(Real_Time Clock)簡稱為RTC,主要為各種電子系統提供時間基準。通常把集成于芯片內部的RTC稱為片內RTC,在芯片外擴展的RTC稱為外部RTC,PCF8563是一款低功耗的CMOS實時時鐘/日歷外部芯片,支持可編程時鐘輸出、中斷輸出、低壓檢測等,與處理器通過I2C串行總線進行通信,最大總線速率可達400kHz。

二、RTC精度設計

RTC的主要職責就是提供準確的時間基準,計時不準的RTC毫無價值可言。目前部分MCU在片內已集成RTC,實際測試中在電池供電6小時環境下片內RTC的偏差在1-2分鐘。因此,若對實時時鐘有較高的要求則需優先考慮外擴RTC,同時要求時鐘精度更高的RTC,比如PCF8563,表1所示是不同RTC的時鐘精度對比。

1、電路設計

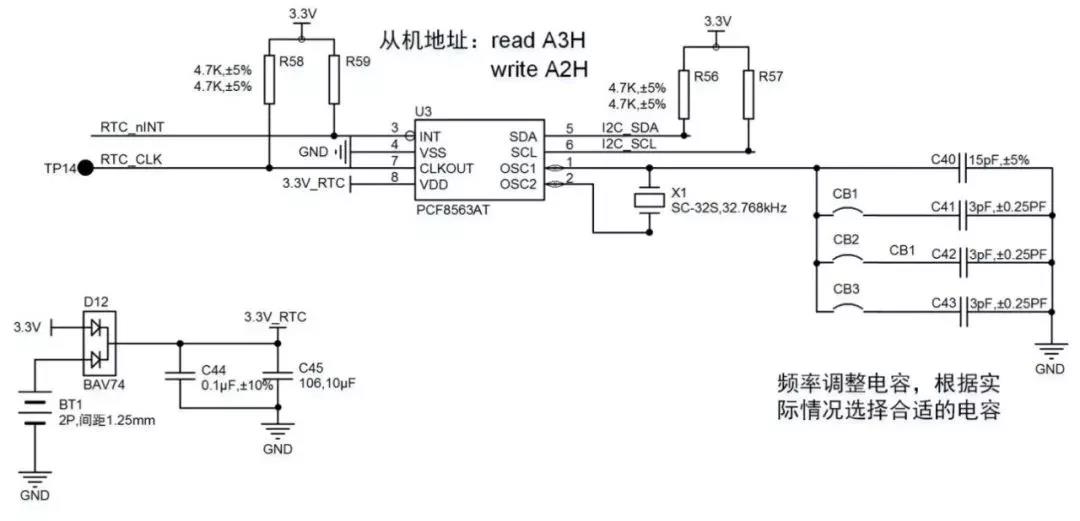

RTC設計電路簡約而不簡單,時鐘芯片的選擇、晶振的選擇、電路設計、器件放置、阻抗控制、PCB走線規范均會影響RTC的時間基準的穩定性,圖1為RTC芯片PCF8563電路設計。

圖1 PCF8563參考電路圖

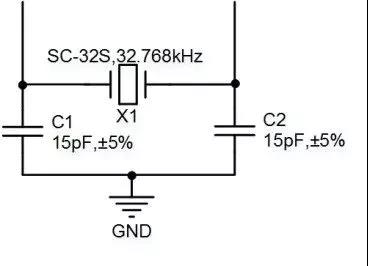

2、晶體對地電容容值選擇

負載電容:

Cload= [ (Ca*Cb)/(Ca+Cb) ]+Cstray

其中Ca、Cb為接在晶體兩引腳到地的電容,Cstray為晶體引腳至處理器晶體管腳的走線電容(即雜散電容總和),一般Cstray的典型值取4~6pF之間;

如要滿足晶體12.5pF負載電容的要求:

Cload= [ (15*15)/(15+15) ]+5=12.5pF

圖2 常見時鐘電路

3、PCB布線

由于RTC的晶振輸入電路具有很高的輸入阻抗,因此它與晶振的連線猶如一個天線,很容易耦合系統其余電路的高頻干擾。而干擾信號被耦合到晶振引腳導致時鐘數的增加或者減少,考慮到線路板上大多數信號的頻率高于32.768kHz,所以通常會發生額外的時鐘脈沖計數,因此晶振應盡可能靠近OSC1和OSC2引腳放置,同時晶振、OSC1和OSC2的引腳最好布成地平面,具體PCB布線如圖3所示。

圖3 PCB布線

4、電路相關說明

如圖1所示,R56、R57為I2C總線上拉電阻,PCF8563中斷輸出及時鐘輸出均為開漏輸出,所以也需要外接上拉電阻,如圖1中的的R58、R59,若不使用這兩個信號,對應的上拉電阻可以不用。

對于PCF8563芯片,需外接時鐘晶振32.768kHz(如圖1的X1),推薦使用±20ppm或更穩定的晶振。PCF8563典型應用電路推薦使用15pF的晶振匹配電容,實際應用時可以作相應的調整,以使RTC獲得更高精度的時鐘源。一般晶振匹配電容在15pF~21pF之間調整(相對于±20ppm精度的32.768kHz晶振),15pF電容時時鐘頻率略偏高,21pF電容時時鐘頻率略偏低。

5、精度調整方法

設置PCF8563時鐘輸出有效(CLKOUT),輸出頻率為32.768kHz;

使用高精度頻率計測量CLKOUT輸出的頻率;

根據測出的頻率,對CB1、CB2、CB3作短接或斷開調整,頻率比32.768kHz偏高時,加大電容值,頻率比32.768kHz偏低時,減小電容值。

說明:圖1中的C41、C42、C43的值在1pF~3pF之間,根據實際情況確定組合方式,以便于快速調整,推薦使用(3pF、3pF、3pF)、(1pF、2pF、3pF)、(2pF、3pF、4pF)。

三、RTC低功耗設計

很多RTC設計成可以只依靠一塊電池供電就能工作,如果主電源關閉,僅依靠一小塊鋰電池就能夠驅動振蕩器和整個時鐘電路,如何降低RTC電路工作時功率消耗?

通過應用幾種不同的方法可以降低RTC功耗:

選擇低功耗的RTC,比如PCF8563,表2所示是不同RTC的功率消耗對比:

表2 常見RTC功率消耗對比

RTC電源切換電路中,選擇漏電流小的二極管比如BAV74,當系統電源電壓3.3V斷開時,BT1鋰電池CR2032(3V/225mAh)通過二極管向RTC供電;

圖4 RTC電源切換電路

盡量少而且合理地訪問RTC,減少I2C總線的動態電流;

將I2C總線的上拉電阻設計得盡量大些,比如10k;

在應用時,通過設置寄存器關閉RTC的時鐘CLKOUT輸出。

-

功耗

+關注

關注

1文章

836瀏覽量

32700 -

RTC

+關注

關注

2文章

623瀏覽量

69012

原文標題:【干貨】如何解決RTC精度、功耗問題?

文章出處:【微信號:ZLG_zhiyuan,微信公眾號:ZLG致遠電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

電機常見故障分析及解決方法

321Y驅動器的常見故障及解決方法

電子焊接的常見問題及解決方法

gitee 常見問題及解決方法

mac的常見問題解決方法

Ubuntu系統常見問題及解決方法

回饋式直流電子負載常見故障及解決方法

評論