方法論體現(xiàn)IC,封裝和PCB

IC,其封裝和目標(biāo)系統(tǒng)板的設(shè)計傳統(tǒng)上是由通用規(guī)范驅(qū)動的獨(dú)立開發(fā)流程。系統(tǒng)設(shè)計人員通常將所有設(shè)計問題的最終分辨率降級到設(shè)計周期的后端集成階段。但是今天不斷縮小的芯片,朝著更小,更低成本和更強(qiáng)大的電路板和系統(tǒng)的驅(qū)動,以及快速將設(shè)計推向市場的無情壓力需要一種新的協(xié)同設(shè)計方法。

設(shè)計目前,在不同的設(shè)計環(huán)境中使用高度分散的一組設(shè)計流程來執(zhí)行系統(tǒng)互連分析。這主要是出于三個主要原因:不同的制造規(guī)模,材料和工藝;設(shè)計專業(yè)化導(dǎo)致各制造商之間的復(fù)雜設(shè)計鏈;傳統(tǒng)的CAD環(huán)境。

今天,設(shè)計人員需要一種平衡的方法來應(yīng)對高密度,千兆赫茲,低壓系統(tǒng)互連的挑戰(zhàn)。由于時序,功率和信號完整性設(shè)計問題緊密相關(guān),因此必須跨越各種系統(tǒng)互連組件(從設(shè)計規(guī)范到制造)來解決這些問題,以實(shí)現(xiàn)設(shè)計可預(yù)測性。

最初開發(fā)的設(shè)計流程和方法各個組件的設(shè)計現(xiàn)在看起來很古老。挑戰(zhàn)在于構(gòu)建具有足夠細(xì)節(jié)的完整互連模型,以支持適當(dāng)?shù)姆治黾墑e。單個信號互連網(wǎng)絡(luò)可以輕松跨越多個IC,封裝和電路板,每個都基于不同的技術(shù)。協(xié)同設(shè)計方法將解決傳統(tǒng)的物理和邏輯約束以及整個設(shè)計鏈中時序,功率和信號完整性的相互交織問題。

協(xié)同設(shè)計方法必須能夠吸收物理規(guī)則,制造材料的電氣特性,由設(shè)計重用和邏輯連接產(chǎn)生的任何經(jīng)驗(yàn)數(shù)據(jù)。要開發(fā)這種新方法,必須將設(shè)計挑戰(zhàn)分解為一組離散的任務(wù),從而產(chǎn)生可在CAD環(huán)境中實(shí)施的流程。

將設(shè)計行為概念化為一個融合過程非常重要,該過程以抽象模型開始并逐漸成熟為制造組件。系統(tǒng)互連的第一個完整模型應(yīng)該按照規(guī)范開發(fā),作為驗(yàn)證該規(guī)范可行性的努力的一部分。如果目標(biāo)無法實(shí)現(xiàn),那么追求目標(biāo)是沒有意義的。此抽象或虛擬系統(tǒng)互連模型將基于可用的經(jīng)驗(yàn)法則,近似值和經(jīng)驗(yàn)數(shù)據(jù)的組合。模型的準(zhǔn)確性應(yīng)足以執(zhí)行密鑰分析,但不能過于復(fù)雜地構(gòu)建或支持。該模型提供了自上而下的約束,并且隨著設(shè)計的進(jìn)展,它可以隨著實(shí)現(xiàn)數(shù)據(jù)逐步更新。

寄生電路模型必須近似或?yàn)槊總€系統(tǒng)互連組件提取(或兩者)并使用驅(qū)動程序和接收器模型組裝成單個網(wǎng)絡(luò)。寄生電路的阻抗描述了互連元件中電壓和電流的關(guān)系。阻抗與頻率有關(guān),因此必須在信號的預(yù)期工作頻率下計算。必須根據(jù)需要執(zhí)行頻域仿真,以開發(fā)執(zhí)行精確時域仿真所需的參數(shù)。為了支持近似,工程師可以在考慮工作頻率的情況下為每種制造技術(shù)預(yù)先描述互連結(jié)構(gòu)。這項額外的練習(xí)將提供每個頻率所需目標(biāo)阻抗的表格以及互連的長度,寬度和間距的一般行為。必須開發(fā)驅(qū)動器和接收器模型以表示源的信號行為和連接的加載。這些模型可以使用晶體管級模型在Spice中實(shí)現(xiàn),或者使用諸如I/O緩沖區(qū)信息規(guī)范之類的格式來實(shí)現(xiàn)。宜必思的開發(fā)旨在提供創(chuàng)建此類模型的方法。工程師可以從任何現(xiàn)有的Spice模型中獲得Ibis模型,或者他們可以編寫行為模型來表示I/O緩沖區(qū)(有關(guān)Ibis的詳細(xì)信息,請參閱www.eigroup.org/ibis/ibis .htm)。

一旦定義了協(xié)同設(shè)計方法的問題,數(shù)據(jù)和模型,下一步就是鏈接IC,封裝和電路板設(shè)計流程。這三個獨(dú)立的設(shè)計流程通常分布在不同的地理區(qū)域,組織和開發(fā)合作伙伴。因此,使用一個大型中央數(shù)據(jù)庫的概念通常是不實(shí)際的。

在這種環(huán)境下,這些設(shè)計流程之間的互操作應(yīng)該被定義為一個小的共享數(shù)據(jù)結(jié)構(gòu),用于描述設(shè)計界面。硬數(shù)據(jù)和約束。例如,用于倒裝芯片設(shè)計的IC到封裝接口包括以下部分:共享凸塊陣列; I/O緩沖區(qū)和凸點(diǎn),凸點(diǎn)和封裝球之間的賦值關(guān)系; I/O緩沖器到凸點(diǎn)再分配互連的電路描述;用于凸點(diǎn)到球封裝襯底互連的電路描述; I/O緩沖區(qū)宜必思車型;和共享約束,如差分對和目標(biāo)阻抗。

目標(biāo)定義

接下來,設(shè)計師必須定義共同設(shè)計目標(biāo)。在這種情況下,該定義將包括管理I/O緩沖器和凸點(diǎn)陣列和封裝球之間的分配,布局和布線仲裁的能力,以便系統(tǒng)互連滿足設(shè)計人員的成本,制造,時序,信號完整性和功率 - 分發(fā)要求。

封裝和電路板設(shè)計流程之間存在類似的數(shù)據(jù)和協(xié)同設(shè)計任務(wù)。此過程中最大的挑戰(zhàn)是確保IC到封裝和封裝到板的接口是相互考慮的。要解決這個問題,IC,封裝和電路板的協(xié)同設(shè)計必須通過緊密鏈接其不同的設(shè)計過程來執(zhí)行。

一旦定義了協(xié)同設(shè)計過程,就必須將其高度實(shí)現(xiàn)。高效的CAD解決方案在這個新的使用模型中,舊的方法和CAD工具實(shí)現(xiàn)已經(jīng)過時。對于這種新環(huán)境,必須開發(fā)新的CAD工具,以支持協(xié)同設(shè)計過程。它們必須支持跨平臺的操作,包括硬件和軟件應(yīng)用程序。同時,必須開發(fā)新的方法來管理共享數(shù)據(jù)和共同約束。

最終,通過允許開發(fā)團(tuán)隊同時設(shè)計IC,其包和目標(biāo)系統(tǒng)板,將產(chǎn)生這樣的方法縮短設(shè)計周期,降低設(shè)計成本,提高產(chǎn)品質(zhì)量。

Bill McCaffrey是Cadence Design Systems Inc.(加利福尼亞州圣何塞)的硅封裝板平臺架構(gòu)師。

-

pcb

+關(guān)注

關(guān)注

4325文章

23159瀏覽量

399343 -

封裝

+關(guān)注

關(guān)注

127文章

7990瀏覽量

143281 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43138

發(fā)布評論請先 登錄

相關(guān)推薦

材料失效分析方法匯總

eda與傳統(tǒng)數(shù)據(jù)分析的區(qū)別

十字路口的全球化,中國企業(yè)的破局之道

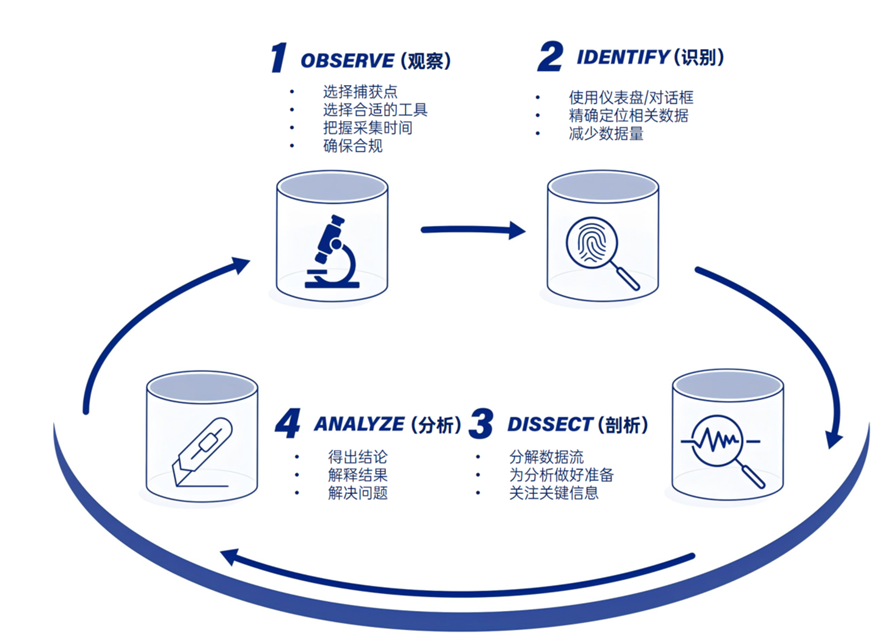

艾體寶干貨 OIDA之一:掌握數(shù)據(jù)包分析-學(xué)會觀察

基于TRIZ方法的電力隧道智慧感知系統(tǒng)

解決偶發(fā)、難復(fù)現(xiàn)、低概率電路故障的有效策略

方法論包含哪些部分

方法論包含哪些部分

評論