隨著系統(tǒng)設(shè)計公司應(yīng)對當今經(jīng)濟環(huán)境的考驗,他們面臨著尋找提高產(chǎn)品開發(fā)和制造流程效率的雙重挑戰(zhàn),同時管理這些產(chǎn)品日益復(fù)雜的問題。這些業(yè)務(wù)因素促使人們需要更高效地在印刷電路板(PCB)上實現(xiàn)高密度,高引腳數(shù)的FPGA,ASIC和IC以及新的工作流程方法,使公司能夠滿足上市時間和設(shè)計性能目標當我們考慮FPGA密度和性能的最新進展推動FPGA設(shè)計開始呈指數(shù)式增長時,對更高效流程的需求尤為重要。 FPGA正在越來越多的應(yīng)用中出現(xiàn),推動了對FPGA和PCB設(shè)計工具集成的需求。

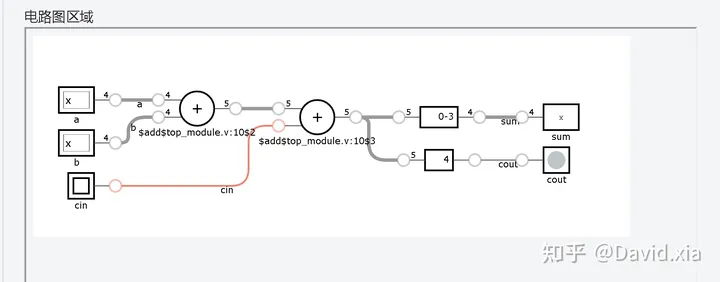

例如,PCB可能包含多個高引腳數(shù)(1,500至2,000)FPGA,這些FPGA與PCB同時設(shè)計,以滿足積極的上市時間目標。 FPGA封裝中的引腳輸出變化必須不斷反映到PCB原理圖和布局設(shè)計數(shù)據(jù)庫中。用于PCB的高速信號完整性分析工具必須能夠訪問I/O驅(qū)動器和接收器的驗證模型。為完成或滿足高速時序而布線PCB可能還需要對FPGA進行引腳輸出更改。

這種雙軌設(shè)計過程的一個主要例子是為單個PCB設(shè)計多個FPGA。 FPGA的設(shè)計可能包括EDA供應(yīng)商和FPGA供應(yīng)商提供的工具。 PCB的設(shè)計將包括來自EDA供應(yīng)商的工具,不一定與FPGA工具供應(yīng)商相同。

第一個問題是簡單地將FPGA布局布線工具的結(jié)果反映到原理圖和PCB布局工具中。對于1,500+引腳FPGA,如果手動完成,此過程可能需要一周時間。大型FPGA需要一個過程,在該過程中,符號在功能上被分解(斷裂),以便適合甚至最大的原理圖表。隨著FPGA設(shè)計過程的繼續(xù),引腳輸出發(fā)生變化(通常為4-6次),如果沒有完全自動化的FPGA工具到PCB原理圖符號和幾何過程,設(shè)計時間表將會丟失。

不幸的是, FPGA的設(shè)計不僅僅在FPGA設(shè)計者的控制之下。當FPGA放置并布線在PCB上時,互連網(wǎng)絡(luò)的定時和延遲調(diào)整可能需要更改FPGA的引腳分配。利用可了解FPGA引腳交換和驅(qū)動器規(guī)則的PCB設(shè)計系統(tǒng),可以在PCB環(huán)境中進行這些引腳更改,然后自動反射回FPGA工具。如果PCB工具沒有FPGA規(guī)則,這可能會成為一個非常迭代且耗時的過程。

為了確保正常的性能,必須執(zhí)行高速驗證,其中包括PCB。由于FPGA上現(xiàn)在常見的千兆位速度,F(xiàn)PGA供應(yīng)商提供的設(shè)計套件必須包含準確的IBIS,Spice或VHDL-AMS模型。利用這些模型和可在GHz范圍內(nèi)進行分析的PCB驗證工具,可以驗證設(shè)計的信號完整性和性能。

底線是電子公司需要緊密,雙向集成FPGA工具及其PCB設(shè)計工具以及EDA和FPGA供應(yīng)商之間的密切合作。通過這種整合與合作,可以實現(xiàn)上市時間和性能目標。如果沒有它,系統(tǒng)設(shè)計的日益復(fù)雜化將使這一過程停滯不前,并最終限制或消除電子公司的利潤。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21735瀏覽量

603154 -

pcb

+關(guān)注

關(guān)注

4319文章

23094瀏覽量

397710 -

華強pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43039

發(fā)布評論請先 登錄

相關(guān)推薦

Verilog vhdl fpga

FPGA基礎(chǔ)知識及設(shè)計和執(zhí)行FPGA應(yīng)用所需的工具

PCB板的電磁協(xié)同設(shè)計

PCB電路與結(jié)構(gòu)的EMC協(xié)同仿真技術(shù)研究

IOy系列BACnet/IP遠程IO模塊如何與智能樓宇系統(tǒng)進行集成和協(xié)同工作?

推挽驅(qū)動芯片的工作原理是什么

淺談如何克服FPGA I/O引腳分配挑戰(zhàn)

# FPGA 編程如何工作?

FPGA輸入的時鐘信號必須是方波么?正弦波會有影響么?

不同工作環(huán)境溫度對電感性能有何影響?

SOLIDWORKS 2024:智能工作、協(xié)同工作

FPGA,PCB工具為什么必須協(xié)同工作

FPGA,PCB工具為什么必須協(xié)同工作

評論