編者注:以下內容源于Lee Ritchey撰寫的第一次正確的高速PCB和系統設計實用手冊第38章。該書由Ritchey的培訓和咨詢公司Speeding Edge出版。

本章介紹封裝寄生電感對高速邏輯電路性能的影響。具體地說,在這種情況下涉及的封裝寄生是進出IC封裝的電源路徑中的不需要的電感。隨著邏輯速度的提高以及數據和地址總線變得越來越寬,這些切換事件中涉及的電流瞬變所產生的噪聲尖峰已經成為失敗的主要原因。

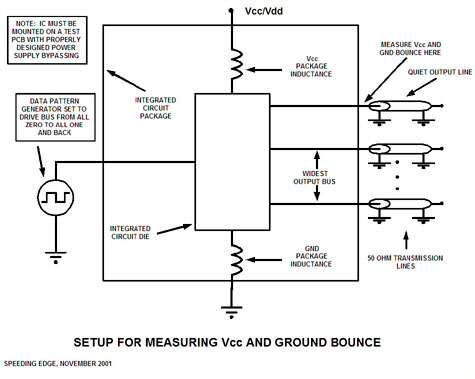

Vcc和接地反彈是IC芯片上Vcc和接地導軌相對于PCB平面上各自電平的變化。這種類型的不需要的瞬態通常是單端邏輯驅動器對傳輸線充電和放電的結果。圖38.1說明了創建Vcc和接地反彈的方式。

圖38.1 ??顯示Vcc和接地反彈的典型單端傳輸線

圖38.1的左側顯示了為傳輸線的寄生電容充電所需的電流的電流路徑以及負載的寄生電容。傳輸線從邏輯0切換到1.圖38.1的右側顯示了當邏輯線從邏輯1切換到0時與寄生電容放電相關的電流路徑。這些瞬態電流是同步開關噪聲(SSN)。圖中所示的電感包括將IC電源引線連接到電源層的過孔電感。

請注意,IC芯片的Vcc端子相對于PCB電源上的Vcc驅動為負極在邏輯0到1轉換期間的平面。 IC的所有端子同時被驅動為負(這是Vcc反彈)。結果是,所有靜音輸出和輸入都會出現此電壓尖峰。如果尖峰足夠大,則可能導致邏輯故障。在從邏輯1到0的轉換期間,IC的接地軌在PCB電源平面上相對于地驅動為正(這是接地反彈)。這個尖峰也出現在所有線路上,并且可能導致邏輯故障。

公式38.1可用于計算由邏輯狀態變化引起的電壓瞬變幅度。

公式38.1 ??用于計算電感器間電壓降的公式

其中:VL =電感器兩端的電壓降,L是Henrys電感器的電感,di =電流變化幅度,單位為安培, dt =進行當前更改所需的時間。

請注意,只有當通過它們的電流發生變化時,或者更準確地說,當通過它們的電磁場發生變化時,電感才會出現電壓降。

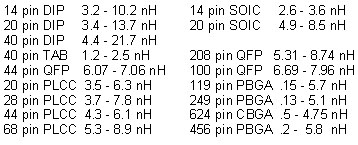

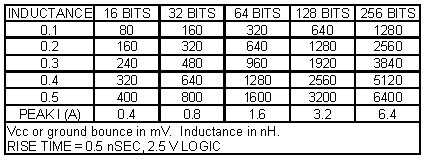

表38.1列出了某些典型IC的引線電感包。電感廣泛傳播的原因是大多數封裝中的引線長度差別很大。

表38.1 ??各種IC封裝的典型引線電感

為了了解常見IC封裝中可能出現的Vcc和接地反彈幅度,可以進行簡單的計算。例如,將使用20引腳DIP(雙列直插封裝)。該封裝上的電源引腳位于拐角處,每個電源引腳的電感為13.7納亨。在這種情況下,ΔI是當邏輯狀態從0變為1時,單個輸出為50 mA,而5V HCMOS部件的增量時間為2 ns。使用等式38.1中的這些值導致電壓尖峰為342 mV。

想象一下當總線的所有8位同時從0變為1時會發生什么。電壓尖峰為2.74伏。接下來,上升時間變為1 ns。峰值為5.48伏。正是這種切換瞬態驅動了從DIP到PLCC封裝的變化。試圖提高邏輯速度,同時保留在經過驗證的真實包中的公司發現他們的產品無法正常工作。應該注意的是,這個問題與封裝有關,并且不能通過在PCB上采取的動作來解決。

Vcc和接地反彈(SSN)是由IC封裝的電源路徑中的電感過大引起的。不能對PCB采取任何措施來解決此問題。更換為具有較低封裝引線電感的IC封裝是必要的。

以上討論也適用于業界常用的QFP封裝。電感不如DIP封裝高。但是,數據總線的寬度比8位寬得多。 SSN的失敗表現為偶爾的失敗。原因是當所有數據位從一個邏輯狀態同時改變到另一個邏輯狀態時,發生最壞情況的噪聲尖峰。這在2 n 次中僅發生一次,其中N是總線中的數據位數。目前處于制造或設計階段的許多“片狀”系統都沒有從這個原因中解脫出來。

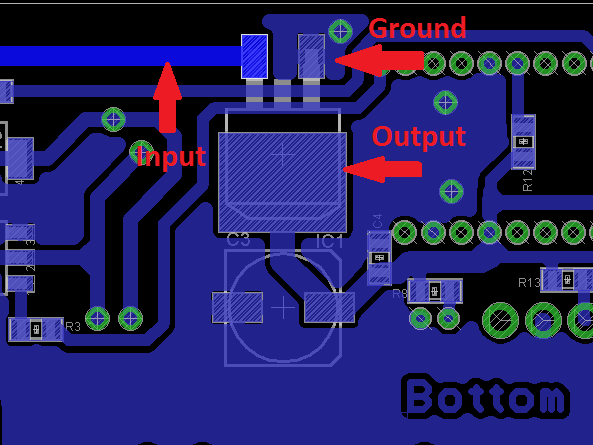

如果不了解這種現象在起作用,就會導致設計永遠不穩定。由于這種潛在的故障機制,在使用之前必須檢查每個被認為是單端邏輯總線驅動器的部件,以確保SSN不會導致故障。圖38.2說明了用于測量最壞情況SSN的測試設置。

圖38.2 ??用于測量最壞情況Vcc和接地反彈的測試設置

為了測量最壞情況Vcc和接地反彈,有必要用最逼真的方法加載最寬總線的所有輸出可以同時切換的負載集。通常通過在每個輸出端連接一個大電容(例如60 pF)來測試IC輸出,并觀察上升和下降時間。這不是一個現實的負載。它使輸出“過載”并導致上升或下降時間比輸出驅動傳輸線時實際發生的時間慢。此外,電容器充電或放電所需的電流尖峰比實際使用中的電流尖峰大得多。實際負載是50歐姆的傳輸線,因為這是通常預期驅動的部件。

在圖38.2中,所有輸出都“加載”了50歐姆的傳輸線。測量探頭連接到一個輸出,該輸出由與將要切換的數據線相同的內部電源和接地總線供電。 IC安裝在具有電源平面結構的PCB上,該電源平面結構能夠提供將所有數據線從0切換到1所需的充電電流,而不會下垂。

為了觀察Vcc反彈,IC采用信號模式驅動,使所有數據線同時從0切換到1。在發生這種情況時,與此事件相關的Vcc彈跳將出現在安靜的線路上,幾乎沒有衰減。 Vcc反彈波形來自該電流波形的上升沿。

為了觀察接地反彈,IC采用信號模式驅動,使所有數據線同時從1切換到0。在發生這種情況時,與此事件相關的地面反彈將出現在安靜的線路上,沒有衰減。

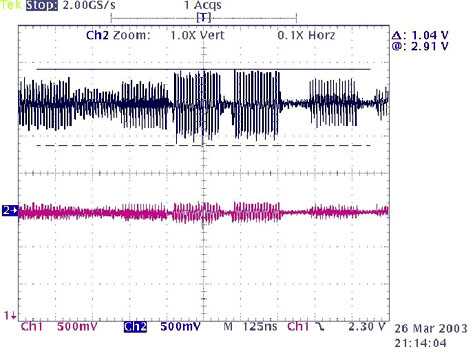

圖38.3中的波形以這種方式在實際IC上測量。在這種情況下,被切換的數據總線是64位寬,Vcc是2.5伏。頂部曲線是Vcc和地面反彈的組合。 Vcc以上的偏移是地面反彈,Vcc以下的偏移是Vcc反彈。通過將所有數據線從0切換到1然后多次切換1到0來產生這組波形。

請注意,偏移幅度大致相同,為500 mV。由此可以推斷,Vcc和接地路徑中的電感大約相同。可以粗略地了解這種電感有多大。這可以通過使用公式38.1來實現。

每個輸出的峰值電流為2.5V/100歐姆或25 mA。總電流為64 x 25 mA或1.6A。得到的電壓為0.5 V.增量時間為2 ns。電感計算為約.625 nH。這種電感是IC封裝引線的電感和通向PCB的通孔的組合,用于接入電源和接地層。

從早期的電源討論來看,已經確定需要電流執行此切換功能是從PCB內置的平面電容中提取的。如果此電容不夠大,每次數據線從0切換到1時,Vcc上都會出現紋波。這在圖38.1的左上角顯示為“v”形傾角。

圖38.3中的下部波形是Vcc上的紋波,對應于這些開關事件。在此示例中,設計到PCB中以支持此事件的平面電容為24 nF。產生的紋波約為150 mV。對于2.5V邏輯,這接近可接受的極限。減少這種紋波的唯一方法是重新設計PCB疊層以增加更多的平面電容。分立電容具有太大的電感來解決這個問題。

圖38.3 ??具有Vcc噪聲的64位數據總線上的實際Vcc和接地反彈

除了設計PCB疊層以產生足夠的平面電容以提供開關瞬態外,最小化電感也很重要到達飛機所需的過孔。因此,支持最大數據總線的平面對應該是元件下方的第一個平面對。

圖38.3中的波形是此特定設計的上電復位線。每次該數據總線的所有成員從0切換到1時,系統都會經歷上電復位周期。這將在內存訪問期間發生。結果是一個無法裝運的系統,無法通過在PCB上采取任何措施來修復。唯一的補救措施是重新設計IC封裝。這種設計通常被稱為硅谷墓碑。

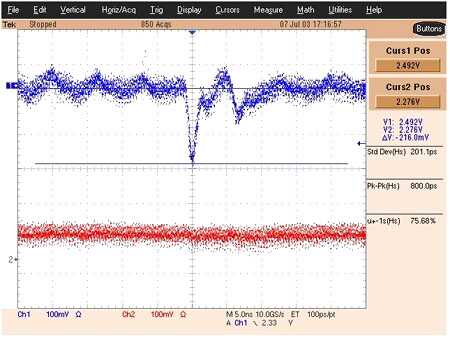

圖38.4 ??具有Vcc噪聲的80位數據總線上的實際Vcc反彈

圖38.4是來自另一個IC的Vcc反彈波形,其中80位數據總線同時從0切換到1。還顯示了Vcc上的噪音。應該注意的是,與該切換事件相關的Vcc噪聲很小,很難看到。這是因為支持此切換事件的平面電容為140 nF或圖38.3中的7倍。

圖38.4中的Vcc反彈來自2.5V DDR數據總線。可以使用公式38.1計算引起該噪聲的有效電感。在這種情況下,每行的ΔI也是25mA。總Δ增量為2A。 ΔV為216 mV。 ΔT為1.15 ns。由此,等效L為0.497nH。同樣,這是封裝電感和連接到電源層的過孔電感的組合。

圖38.4中的示例具有1.16 ns的相對較慢的上升時間。該示例中的組件能夠產生小于0.5ns的上升時間。如果性能頻譜快速側的這些部件中的一個安裝在同一電路中,則Vcc反彈將是所示的兩倍,即532 mV。這遠遠超過了該電路的噪聲容限。重新設計封裝以降低寄生電感是解決此問題的最可靠方法。

如果重新設計IC封裝不是一個選擇,還有其他可能的解決方案嗎?在某些情況下有。噪聲問題的根源是許多輸出同時切換。有時可以錯開輸出的時鐘,使得只有一部分可以同時切換。這通常稱為多相時鐘。另一種選擇可能是將輸出分配到幾個Vcc和地線上。這可以通過市場上的一些FPGA實現。

此等式中的一個參數是信號邊沿的上升時間。有可能減慢邊緣。

當然,最佳解決方案是選擇電源和接地導軌中具有極低電感的封裝的元件。表38.2顯示了各種2.5V寬數據總線為0.5 nSEC邊沿產生的Vcc或接地反彈量與電源路徑中總電感的函數關系。

表38.2 ?? Vcc和接地反彈與封裝電感,2.5V CMOS,0.5 ns邊緣

隨著邊沿變得更快,數據總線變得更寬,IC封裝的設計必須非常小心地完成應避免使用Vcc和接地反彈。

在設計中包含供應商無法展示Vcc和地面反彈數的部件是不明智的。

必須檢查每個用于驅動寬數據總線的IC,以確保封裝電感足夠低,以產生可接受的低Vcc和接地反彈。

Vcc和地面反彈已成為主要來源大多數新設計中的間歇性故障。這些故障可追溯到較差的IC封裝設計。

如何確定新IC在包裝之前的Vcc和接地反彈

通常,有必要選擇仍在開發中的部件。沒有真正要衡量的部分。可以在Spice建模軟件包中對I/O和封裝進行建模,并計算預期的Vcc和地面反彈。這是通過獲得輸出驅動器的Spice模型,將其與封裝電源和接地路徑的預測電感相結合,驅動適當阻抗的傳輸線并以最終電路中預期的最快上升和下降時間切換輸出來完成的。 。

設計不良的BGA封裝示例

通常,BGA封裝具有比其他封裝類型更好的Vcc和接地電感,例如QFP,PLCC和DIP。但是,情況并非如此。一些BGA封裝被設計成使得從電源和接地觸點到與PCB接觸的球的引線或導線。當考慮BGA封裝中的新元件時,必須檢查封裝布局以確保Vcc和接地路徑具有低且相等的電感。

圖38.5是兩個具有此問題的雙層BGA封裝的照片。在兩種情況下,管芯都通過觸點安裝在腔體中,觸點直接穿過封裝到BGA背面的球。這些是接地觸點,電感非常低。在這兩種情況下,Vcc引腳都是從管芯邊緣到BGA封裝邊緣的跡線。痕跡。

圖38.5 ??兩種在Vcc引線中具有過高電感的BGA封裝

確定可接受的Vcc和接地反彈量

通過分析來自其他源的噪聲并將其與所使用的邏輯系列的噪聲容限進行比較,可以計算出可以容忍的Vcc和接地反彈量。 Vcc和接地反彈可以消耗總噪聲容限的一部分。用于執行此分析的方法將在后續章節中介紹。

Lee Ritchey是Speeding Edge的創始人兼總裁,該公司為高科技公司提供私人現場培訓課程以及通過UC的課程伯克利的推廣計劃和行業會議。

-

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43063

發布評論請先 登錄

相關推薦

HDMI模塊的PCB設計

專業PCB設計,高速PCB設計,PCB設計外包, PCB Layout,PCB Design,PCB畫板公司,PCB設計公司,迅安通科技公司介紹

pcb設計中如何設置坐標原點

PCB設計與PCB制板的緊密關系

PCB設計基本原則總結,工程師必看

PCB設計的EMC有哪些注意事項

PCB設計中的常見問題有哪些?

pcb設計

多層pcb設計如何過孔的原理

什么是PCB扇孔,PCB設計中對PCB扇孔有哪些要求

DC電源模塊的 PCB設計和布局指南

良好的PCB設計是怎樣被破壞的

良好的PCB設計是怎樣被破壞的

評論