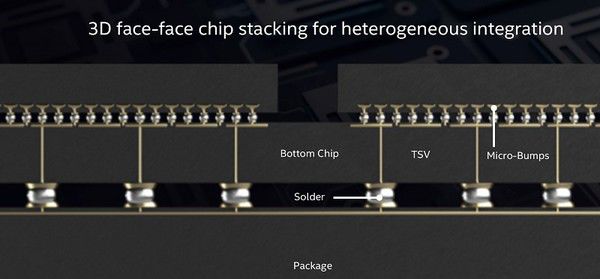

從英特爾所揭露的技術資料可看出,F(xiàn)overos本身就是一種3D IC技術,透過硅穿孔(Through-Silicon Via, TSV)技術與微凸塊(micro-bumps)搭配,把不同的邏輯芯片堆疊起來。

其架構概念就是在一塊基礎的運算微芯片(compute chiplet)上,以TSV加上微凸塊的方式,堆疊其他的運算晶粒(die)和微芯片(chiplets),例如GPU和記憶體,甚至是RF元件等,最后再把整個結構打包封裝。

而英特爾目前所使用的制程已達到10納米,預計也可以順利推進至7納米,也此透過此3D封裝技術,將可在單一芯片中達成絕佳的運算效能,并持續(xù)推進摩爾定律。

英特爾更特別把此技術稱為「臉貼臉(Face-to-Face)」的封裝,強調(diào)它芯片對芯片封裝的特點。而要達成此技術,TSV與微凸塊(μbumps)的先進制程技術就是關鍵,尤其是凸塊接點的間距(pitch)僅有約36微米(micron),如何透過優(yōu)異的打線流程來達成,就非常考驗英特爾的生產(chǎn)技術了。

圖六: Foveros的TSV與微凸塊疊合示意(source: intel)

但是英特爾也指出,F(xiàn)overos技術仍存在三個挑戰(zhàn),分別為散熱、供電、以及良率。由于多芯片的堆疊,勢必會大幅加大熱源密度;而上下層邏輯芯片的供電性能也會受到挑戰(zhàn);而如何克服上述的問題,并在合理的成本內(nèi)進行量產(chǎn)供貨,則是最后的一道關卡。

依照英特爾先前發(fā)布的時程,「Lakefield」處理器應該會在今年稍晚推出,但由于英特爾沒有在COMPUTEX更新此一產(chǎn)品的進度,是否能順利推出仍有待觀察。

-

英特爾

+關注

關注

61文章

9949瀏覽量

171694 -

邏輯芯片

+關注

關注

1文章

152瀏覽量

30565

原文標題:其他「小鋼炮」都一邊玩去吧

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

先進封裝中的TSV/硅通孔技術介紹

先進封裝中互連工藝凸塊、RDL、TSV、混合鍵合的新進展

一文了解硅通孔(TSV)及玻璃通孔(TGV)技術

TSV91xA-Q1運算放大器數(shù)據(jù)表

一文解鎖TSV制程工藝及技術

開啟高性能芯片新紀元:TSV與TGV技術解析

HBM:突破AI算力內(nèi)存瓶頸,技術迭代引領高性能存儲新紀元

TSV 制程關鍵工藝設備技術及發(fā)展

基于兩步刻蝕工藝的錐形TSV制備方法

TSV與異構集成技術的前沿進展與趨勢展望

一文詳解硅通孔技術(TSV)

TSV與μbumps技術是量產(chǎn)關鍵

TSV與μbumps技術是量產(chǎn)關鍵

評論