自20世紀90年代中期以來,內存技術大多根據其運行速度來命名。 PC100 SDRAM設備將以100MHz數據速率運行,PC133以133MHz數據速率運行,依此類推。雖然這種品牌推廣慣例的變化隨著時間的推移而發生變化,但大多數都讓潛在買家了解存儲設備的運行速度。

簡單地說,大多數存儲器技術,實際上是當今所有的主流存儲器技術,已經為自己打上了峰值數據速率,這一直是并將繼續成為計算時的最重要因素之一。記憶系統的性能。然而,在真實系統中運行的存儲器設備在100%的時間內不以其峰值數據速率運行。

從寫入切換到讀取,在特定時間訪問某些地址以及刷新數據都需要在數據總線上保持一定的不活動狀態,從而無法充分利用內存通道。另外,寬并行總線和DRAM核心預取都經常導致不必要的大數據訪問。

內存控制器在給定時間內可以訪問的可用數據量稱為有效數據速率,并且高度依賴于系統的特定應用程序。有效數據速率隨時間變化,通常遠低于峰值數據速率。在某些系統中,有效數據速率可降至峰值數據速率的10%以下。

通常,這些系統可以從內存技術的變化中受益,從而產生更高的有效數據速率。在CPU的產品領域也存在類似的現象,近年來AMD和Transmeta等公司表明,在測量基于CPU的系統的性能時,時鐘頻率并不是唯一重要的因素。

內存技術也已經成熟到高峰和有效數據速率可能與之前不匹配的程度。雖然峰值數據速率仍然是存儲器技術的最重要參數之一,但是其他架構參數可以極大地影響存儲器系統的性能。

影響有效數據速率的參數

有幾類參數影響有效數據速率,其中一類會導致不活動時間段到數據總線上。在這個類中的參數中,總線周轉,行周期時間,CAS延遲和RAS到CAS延遲(tRCD)導致許多系統架構師的大多數延遲問題。

總線周轉本身會在數據通道上造成很長時間的不活動。以GDDR3系統為例,該系統不斷將數據寫入存儲設備的打開頁面。在此期間,存儲系統的有效數據速率與其峰值數據速率相匹配。

但是,現在假設在100個時鐘周期內,存儲器控制器從讀取切換到寫入。由于此開關的懲罰是六個周期,因此有效數據速率降至峰值數據速率的94%。如果在這100個周期內,存儲器控制器將總線從寫入切換回讀取,則會丟失更多周期。

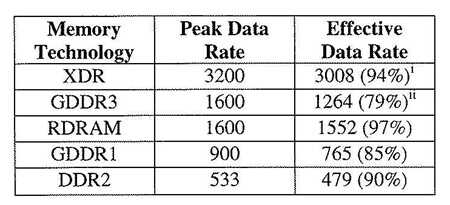

這種內存技術在從寫入切換到讀取時需要15個空閑周期,進一步將有效數據速率降低到峰值數據速率的79%。表1顯示了幾種高性能存儲器技術的相同計算結果。

表1 - 兩個總線轉向的有效和峰值數據速率-counds每100個周期

顯然,所有的內存技術都不是平等的。需要許多總線周轉的系統設計人員可以從選擇XDR,RDRAM或DDR2等更高效的技術中受益。另一方面,如果系統可以將事務分組為非常長的寫入和讀取序列,則總線轉向對有效帶寬的影響最小。但是,其他延遲增加現象(如銀行沖突)可能會通過降低有效帶寬對其性能產生負面影響。

DRAM技術都要求銀行的頁面或行在訪問之前打開。一旦打開,在經過稱為行周期時間(tRC)的最小時間段之前,不能打開同一存儲體中的不同頁面。對開放銀行的不同頁面的存儲器訪問被稱為頁面未命中,并且可能導致與tRC間隔的任何未滿足部分相關聯的延遲懲罰。

對于尚未開放足夠周期以滿足tRC間隔的銀行的頁面未命中被稱為銀行沖突。雖然tRC確定了銀行沖突延遲的大小,但是在給定DRAM中可用的銀行將直接影響銀行沖突發生的頻率。

大多數存儲器技術有四個或八個存儲體,并且在幾十個周期內具有tRC值。在隨機工作負載下,具有八個存儲區核心的存儲庫沖突將比具有四個存儲區核心的存儲體沖突更少。雖然tRC和銀行計數之間的相互作用很復雜,但它們的累積影響可以通過多種方式量化。

內存讀取事務

考慮三種簡單的內存讀取事務。在第一種情況下,內存控制器發出每個事務,以便它與先前事務產生存儲沖突。控制器必須在打開頁面和打開后續頁面之間等待一段時間tRC,從而增加與循環頁面相關的最大延遲時間。在這種情況下,有效數據速率很大程度上與I/O無關,主要受DRAM核心電路的限制。在當今最高端的內存技術中,最大銀行沖突率將有效帶寬降低到峰值的20%到30%之間。

在第二種情況下,每個事務都以一個隨機生成的地址為目標。在這里,遇到銀行沖突的可能性取決于許多因素,包括tRC與存儲器核心中存儲體數量的相互作用。 tRC值越小,開放頁面越早循環,導致銀行沖突處罰越低。此外,存儲器技術具有的存儲體越多,存儲體隨機地址訪問沖突的可能性就越低。

在第三種情況下,每個事務都是頁面命中,在打開的頁面中尋址各種列地址。控制器不需要訪問封閉頁面,允許100%的總線利用率,從而實現有效數據速率等于峰值數據速率的理想情況。

雖然第一和第三種情況涉及相當簡單的計算,但隨機情況受到DRAM或存儲器接口中未特別包含的其他功能的影響。內存控制器仲裁和排隊可以大大提高銀行沖突率,因為可以發出更多可能的非沖突事務而不是那些導致銀行沖突的事務。

但是,添加內存隊列深度并不一定會增加兩種不同內存技術之間的相對有效數據速率。例如,即使增加了內存控制器隊列深度,XDR的有效數據速率也比GDDR3高20%。這種差異的存在主要是由于XDR的銀行數量較多且tRC值較低。通常,較短的tRC間隔,較高的存儲體計數和較大的控制器隊列會導致較高的有效帶寬。

許多限制效率的現象實際上是與行訪問粒度相關的問題。 tRC約束基本上要求內存控制器從新打開的行訪問一定數量的數據,以確保數據管道保持滿員。實質上,為了保持數據總線不間斷運行,打開一行后必須讀取最少量的數據,即使不需要額外的數據。

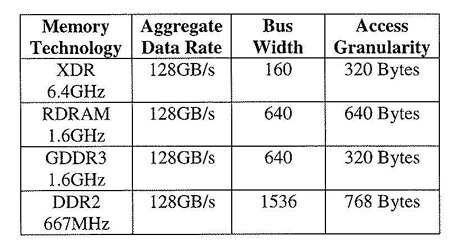

降低內存系統有效帶寬的另一類主要特性屬于列訪問粒度類別,它決定了每個單獨的讀寫操作必須傳輸多少數據。相反,行訪問粒度決定了每行激活需要多少單獨的讀寫操作(通常稱為每個RAS的CAS操作)。

列訪問粒度也可能對有效數據速率產生很大的影響,但影響較小。由于它規定了單次讀取或寫入中傳輸的最小數據量,因此列訪問粒度對通常一次只需要少量數據的系統造成問題。例如,一個16字節訪問粒度的系統,每兩行需要8個字節,必須讀取總共32個字節才能訪問這兩個位置。

由于只需要32個字節中的16個,系統經歷了有效數據速率降低,相當于其峰值數據速率的50%。兩個體系結構參數決定了內存系統的訪問粒度:總線寬度和突發長度。

總線寬度是指連接在內存控制器和內存設備之間的數據跟蹤總數。它設置了最小訪問粒度,因為每個數據跟蹤必須為給定的內存事務攜帶至少一位數據。反過來,突發長度指定每個通道必須為給定事務攜帶的位數。每個事務每個數據跟蹤發送一位數據的存儲器技術據說具有一個突發長度。總列訪問粒度很簡單:

列訪問粒度=總線寬度x突發長度

許多系統架構師僅通過添加來增加內存系統的可用帶寬更多的DRAM設備和增加內存總線的寬度。畢竟,如果400MHz數據速率的四個鏈路為您提供1.6GHz的總峰值帶寬,則八個鏈路將為您提供3.2GHz。添加DRAM設備,電路板上的更多跡線以及ASIC上的相應引腳使總聚合峰值帶寬加倍。

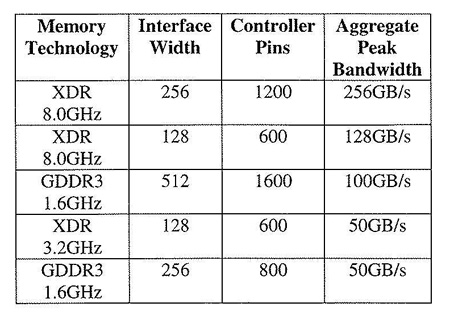

表2顯示了使用不同內存技術和總線寬度可實現的總聚合峰值帶寬以及每種配置所需的總控制器引腳數。

表2 各種存儲器技術和總線寬度的總峰值帶寬以及所需的控制器引腳數

然而,此增益是有代價的。首先,主要關注擠出每一盎司峰值帶寬的架構師已經達到了他們在物理上設計其內存總線的寬度的可行最大值。找到具有256或甚至512位寬存儲器總線的圖形控制器并不罕見,這些存儲器總線需要1,000個或更多控制器引腳。

封裝設計人員,ASIC布局規劃人員和電路板設計人員無法找到要布線的區域這些信號使用廉價的,商業上可行的手段。僅增加總線寬度以獲得更高的峰值數據速率的另一個問題導致從列訪問粒度限制減少的有效帶寬。

假設特定存儲器技術的突發長度等于1,則對于單個存儲器事務,512位寬系統的訪問粒度為512位(或64字節)。如果控制器只需要較小塊的數據,則會浪費剩余數據,從而降低系統的有效數據速率。

例如,一個控制器只需要來自前面提到的內存系統的32字節數據將浪費剩余的32個字節,導致有效數據速率等于峰值數據速率的50%。請記住,這些計算都假定突發長度為1。隨著存儲器接口數據速率的增加趨勢,大多數新技術的最小突發長度大于1。

核心預取

稱為核心預取的功能主要負責最小突發長度的增加。 DRAM核心電路無法跟上I/O電路速度的急劇增加。由于無法再從內核串行獲取數據以滿足控制器請求,因此內核通常會為I/O提供遠大于DRAM總線寬度的數據集。

本質上,核心向接口電路傳輸足夠的數據以使其保持足夠長的時間以使核心為下一個操作做好準備。例如,假設DRAM核心只能每納秒響應一次操作。但是,該接口可以維持每納秒兩位的數據速率。

DRAM內核不是浪費接口的一半功能,而是每次操作取兩個位而不是一個。在接口傳輸數據之后,核心已準備好響應下一個請求而沒有任何延遲。添加的核心預取導致最小突發長度增加2,并將直接影響列訪問粒度。

對于添加到總線寬度的每個附加信號,存儲器接口將傳輸另外兩位數據。因此,最小突發長度為2的512位寬存儲器系統的訪問粒度等于1,024位(128字節)。許多系統對最小訪問粒度問題不敏感,因為它們以非常大的塊訪問數據。但是,有些系統依靠內存系統來提供小型數據單元,并從使用更窄,更高效的內存技術中受益。

表3 當今主流內存技術的單個內存通道的訪問粒度和總線寬度值

結論

有效數據速率變得越來越重要存儲器技術提高其峰值數據速率。在做出內存決策時,設計人員必須深入研究已發布的內存規范,并了解特定技術的功能如何與手頭的應用程序進行交互。

內存系統設計人員必須超越峰值數據速率規范,就像CPU設計人員逐漸停止使用千兆赫作為唯一的性能指標一樣。雖然峰值數據速率在內存接口方面仍然是最重要規范的標題,但有效數據速率開始為系統設計人員和架構師提供空間。明天產品的性能將在很大程度上取決于其內存系統的有效利用。

Victor Echevarria是Rambus公司內存接口部的RDRAM產品經理。他于2002年加入Rambus擔任系統工程師。在加入Rambus之前,Victor與安捷倫科技公司合作,后者開發了用于高速數字采樣示波器的軟件。

-

存儲器

+關注

關注

38文章

7484瀏覽量

163768 -

內存

+關注

關注

8文章

3020瀏覽量

74008

發布評論請先 登錄

相關推薦

具有不同的存儲器單元和存儲器架構的微控制器介紹

KeyStone存儲器架構

相變存儲器(PCM) :新的存儲器技術創建 新的存儲器使用模式

存儲器和總線架構

STM32F7系統架構和存儲器映射

KeyStone存儲器架構詳解

內存架構怎么影響存儲器系統的性能

內存架構怎么影響存儲器系統的性能

評論