1定義

DDR:Double Date Rate 雙倍速率同步動態隨機存儲器。

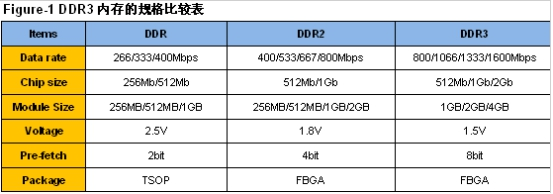

DDR、DDR2、DDR3常用規格:

02阻抗控制要求

單端走線控制 50歐姆,差分走線控制 100歐姆

03DDR布局要求

通常,根據器件的擺放方式不同而選擇相應的拓撲結構。

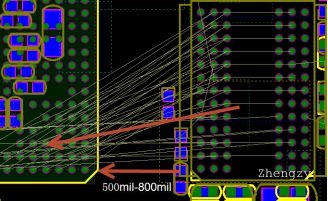

A、DDR*1片,一般采用點對點的布局方式,靠近主控,相對飛線 Bank 對稱。間距可以按照是實際要求進行調整,推薦間距為 500-800mil。

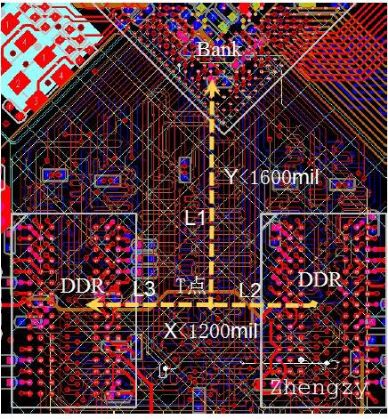

B、DDR*2片,布局相對主控飛線 Bank對稱,常采用 T型拓撲結構, 推薦間距如下:

等長要求 L1+L2=L1+L3

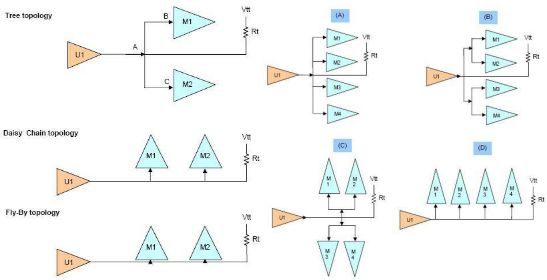

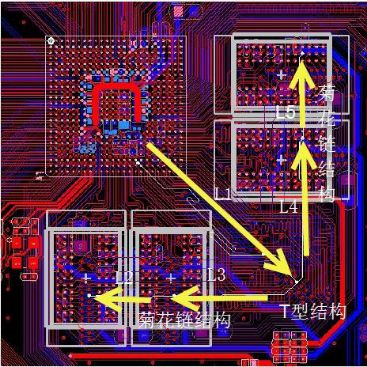

C、DDR*4 片,以下列出了常用的 4 片 DDR 布局拓撲結構。

針對于 DDR2,這些拓撲結構都是能適用的,只是有少許的差別。

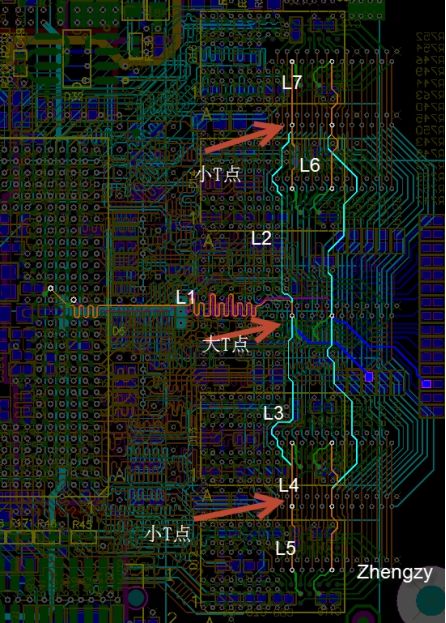

若PCB布線空間允許,Address/Command、Control、CLK,應優先采用單純的“T”型拓撲結構,并盡可能縮短分支線長度,如上面拓撲結構的B圖所示。

等長要求 L1+L2+L6=L1+L2+L7=L1+L3+L4=L1+L3+L5

然而,菊花鏈式拓撲結構被證明在 SI 方面是具有優勢的。對于 DDR3的設計, 特別是在 1600 Mbps時,則一般采用D所示菊花鏈拓撲結構進行設計。

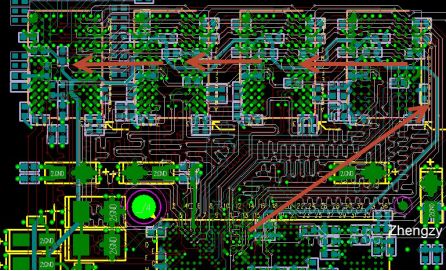

PCB 布線空間有限的,可以采用“T”型拓撲和菊蓮拓撲混合的結構,如下圖所示:

混合拓撲結構中“T”型拓撲的要求與兩片DDR2/3 相同。

等長要求 L1+L3+L2=L1+L4+L5

04信號分組以及走線要求

(以下以4片DDR3設計進行說明)

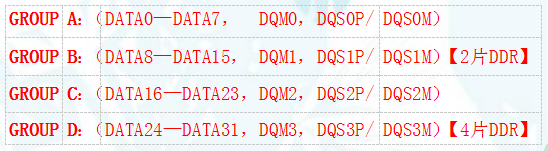

A、32條數據線(DATA0-DATA31)、4條DATA MASKS(DQM0-DQM3),4對DATA STROBES差分線(DQS0P/ DQS0M—DQS3P/DQS3M)

這36條線和4對差分線分為四組:

再將剩下的信號線分為三類:

Address/Command、Control與CLK歸為一組,因為它們都是以CLK的下降沿由DDR控制器輸出,DDR顆粒由CLK 的上升沿鎖存Address/Command、Control 總線上的狀態,所以需要嚴格控制CLK 與Address/Command、Control 之間的時序關系,確保DDR顆粒能夠獲得足夠的、最佳的建立/保持時間。

B、誤差控制,差分對對內誤差盡量控制在5mil以內;數據線組內誤差盡量控制在+-25mil以內,組間誤差盡量控制在+-50mil以內。

Address/Command 、Control全部參照時鐘進行等長,誤差盡量控制在+-100mil 以內。

C、數據線之間間距要滿足3W原則,控制線、地址線必要時可稍微放寬到2W~3W, 其他走線離時鐘線20mil或至少3W以上的間距,以減小信號傳輸的串擾問題。

D、VERF電容需靠近管腳放置,VREF走線盡量短,且與任何數據線分開,保證其不受干擾(特別注意相鄰上下層的串擾),推薦走線寬度>=15mil。

E、DDR設計區域,這個區域請保障完整的參考平面,如下方圖片所示:

-

pcb

+關注

關注

4319文章

23080瀏覽量

397518 -

DDR

+關注

關注

11文章

712瀏覽量

65318

原文標題:看過來,DDR 模塊的 PCB 設計要點都在這里!

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

分享一些常見的電路

PCB郵票孔設計及工藝要點總結

使用單片機的串口發送相應的指令給ESP-WROM-02模組,ESP-WROM-02沒有返回OK或者ERROR的信息的原因?

關于常見PCB材料的一些細節

使用STM來測量出來的ADC0的轉換時間抖動很大是為什么?

PCB板設計時,鋪銅有什么技巧和要點?

DDR終端匹配電阻的長度多少合適?

DDR 模塊的 PCB 設計要點有哪一些

DDR 模塊的 PCB 設計要點有哪一些

評論