在本文中,我們將討論定制設計的任意波形發生器(AWG)板的PCB布局。

這是我寫的關于設計的第四篇文章我的AWG PCB。這就是電路板的樣子:

其他三篇文章涵蓋了微控制器, DAC和DAC的輸出電路。現在是討論布局的時候了;在本文之后,我們將考慮技術介紹完成,我們將繼續進行實際項目。

基礎知識

此PCB,像幾乎所有的PCB一樣,是一個四層板。在我看來,將你自己限制在兩個層次是不明智的,除非你正在處理一個非常簡單的電路,否則你真的需要削減成本。

四層布局在路由方面是有益的。性能:布線,因為通過內部平面的連接幾乎完全消除了電源和接地走線;和性能,因為內部平面允許低電阻,低電感電源和接地連接。當您需要提供寬大的銅區域以改善熱性能時,所有內部平面連接打開的額外頂層和底層空間非常方便(例如,確保您的LDO或電機驅動器不會過熱并進入熱關斷狀態。

電源

我們不妨討論電源電路熱設計主題。

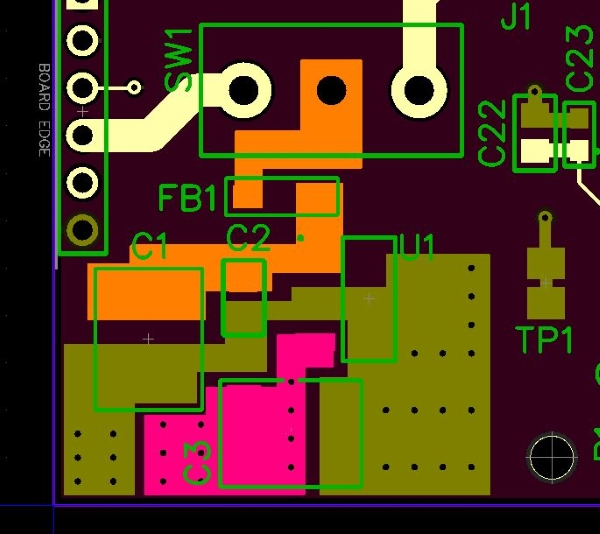

您可以看到所有電源連接如何使用大痕跡或銅傾瀉。 AWG沒有很高的電流要求,但是如果你有房間,那么你可以選擇大的(=低電阻,低電感)跡線。

您還可以看到,我已經很容易將熱量從調節器(U1)移到周圍環境或PCB的其他部分。 U1的散熱片連接到一個大的銅澆口,這個銅澆注通過過孔,將熱量傳導到內部接地層。如果我真的擔心散熱問題,我也可以將這些過孔連接到電路板底部的銅澆注,但在這種情況下,它會完全過度殺傷。

微控制器

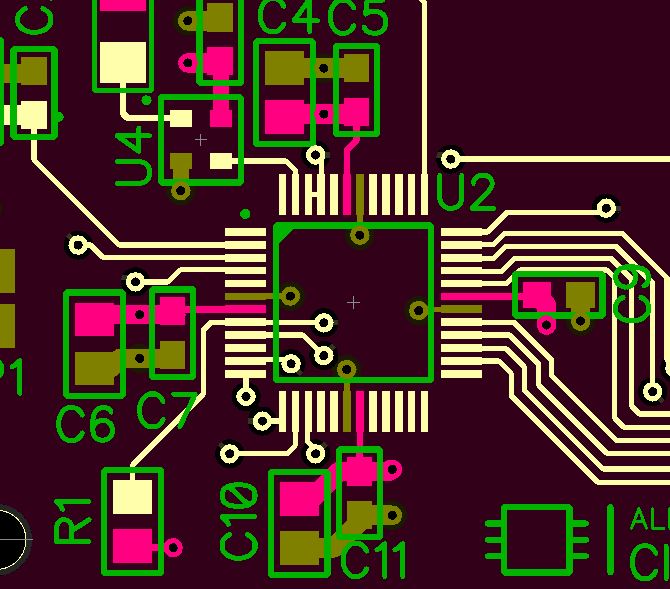

這是電路板微控制器部分的布局:

去耦電容(C4,C5,C6,C7,C9,C10,C11)圍繞芯片周邊排列,非常靠近各自的電源引腳和連接電容的通孔內部飛機。注意較小的帽子是如何始終靠近電源引腳的;這是因為我們更多地依靠低值電容進行高頻旁路,因此首要任務是盡量減小較小電容和引腳之間的電感和電阻。

請注意,U4是一個10 MHz的MEMS振蕩器,也非常靠近微控制器的時鐘輸入引腳。最小化攜帶高頻數字信號的跡線的長度總是一個好主意。首先,存在噪聲優勢:更短,更直接的跡線減少了否則將耦合到相鄰跡線的噪聲量,并且更短的跡線還減少了電磁干擾(EMI),因為它作為天線的效率較低。第二個問題與傳輸線效應有關。最小化跡線長度是避免與信號反射相關的問題的簡單方法。但是,除非您處理長互連或非常大的PCB,否則反射不是10 MHz范圍內頻率的重要問題。

并行總線

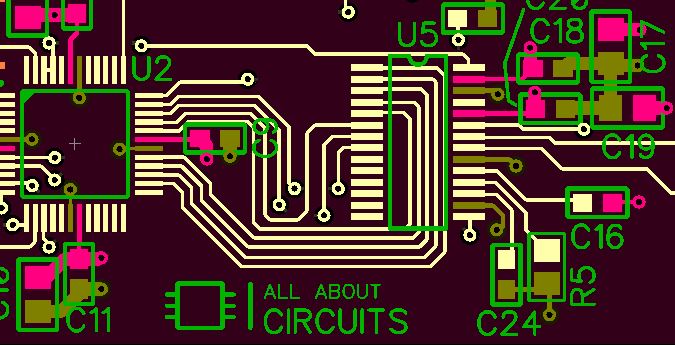

下一張圖顯示了DAC的布局;微控制器和DAC的布置使得8位并行數據總線從微控制器的右側傳輸到DAC的左側。

您可能已經注意到,這是令人煩惱的情況之一,其中引腳配置與您想要的相反:DAC的輸入引腳從第7位移到位0向下,而MCU的輸出引腳從位7移動到位0向上。我無法通過重新分配微控制器引腳來解決這個問題,因為我希望數據位對應于端口2寄存器的實際位(這樣我就可以在不移動位的情況下向DAC寫入一個完整的字節)。所以我最終得到了一些笨拙的路由,但沒有什么可怕的。

當你布置一個并行總線時,總是很好地認識到跟蹤長度,盡管在中等頻率下沒有什么可以強調的。通過跡線的信號的傳播時間可能是150皮秒/英寸。因此,如果您有兩條長度不匹配為1英寸的跡線,則一條信號將在另一條信號之后達到150 ps。如果您的信號以相應周期遠大于150 ps的頻率轉換,則這一英寸不匹配不會導致問題。即使在100 MHz(對于并行總線來說相當快),周期為10 ns,即比一英寸不匹配的到達時間差異大約67倍。

大圖

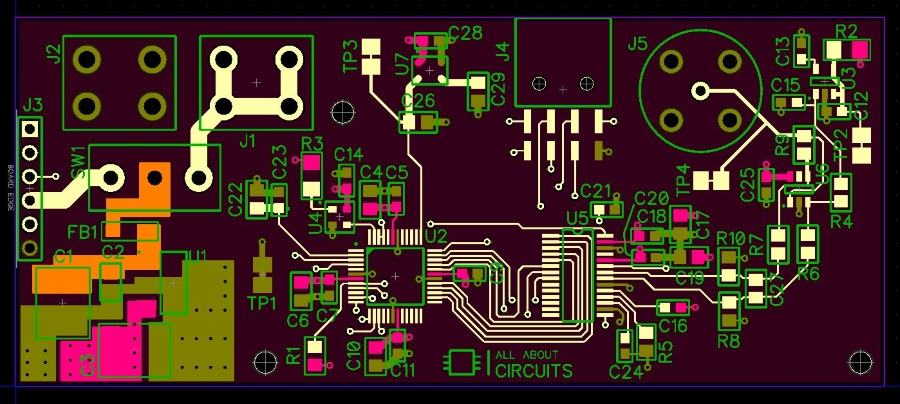

以下是整個布局:

我總是喜歡在PCB布局中保持信號和功能的邏輯流程。我認為這種方法可以使設計過程更加簡單,并且可以提供更好的電路板。 AWG布局從左到右進行:從電源輸入和通信輸入/輸出,到電源電路,到處理器,再到DAC(由處理器控制,構成電路板從數字到模擬的轉換)到模擬信號調理電路,最后到輸出連接器。在功能流程中沒有特定位置的部件 - 例如振蕩器(U4),DAC的無源元件(C16,R5等)和電壓參考(U3) - 布置在它們支持的組件附近。

結論

我們現在已經詳細了解了這個定制設計的任意波形發生器的原理圖和布局。在下一篇文章中,我們將通過簡單的數模轉換任務啟動并運行電路板,我們將繼續閱讀涉及更高級功能和應用的其他文章。

-

微控制器

+關注

關注

48文章

7627瀏覽量

151781 -

pcb

+關注

關注

4324文章

23143瀏覽量

398981 -

波形發生器

+關注

關注

3文章

293瀏覽量

31407

發布評論請先 登錄

相關推薦

任意波形發生器_DDS任意波形發生器的設計

任意波形發生器如何輸出電壓

任意波形發生器的定義、特點及應用

任意波形發生器的使用方法

任意波形發生器中波形生成方法

什么是任意波形發生器

是德任意波形發生器應用領域

任意波形發生器pcb是怎樣布局的

任意波形發生器pcb是怎樣布局的

評論