從PCB布局到編程的設計決策,了解地面反彈是什么以及如何避免它。

大多數本科工程師都沒有教過PCB設計。從某個角度來看,前幾代電子設備相當寬容,設計錯誤仍然可以讓您創建一個功能板。我們知道這一點是因為,如果您在這個業務上花費大量時間查看其他人制作的原理圖和PCB設計,您將很快發現生產PCB上的疏漏,錯誤和明顯的錯誤。你甚至可能會在自己過去的設計中發現錯誤。

這些錯誤已經滑落,部分原因是董事會無論如何都會工作 - 即使只是勉強。

但是,隨著我們向更小的方向發展更快,更低功耗的電路,我們如何創建電路板非常重要。 AsDr。 Eric Bogatin-Teledyne LeCroy物理學家和自稱為“信號完整性傳播者”的人說:

“除非你有令人信服的理由不使用,否則請使用最佳設計實踐。”

本文提供了有關地面反彈原因的信息以及如何在您的設計中緩解它的一些最佳實踐。

什么是地面反彈?

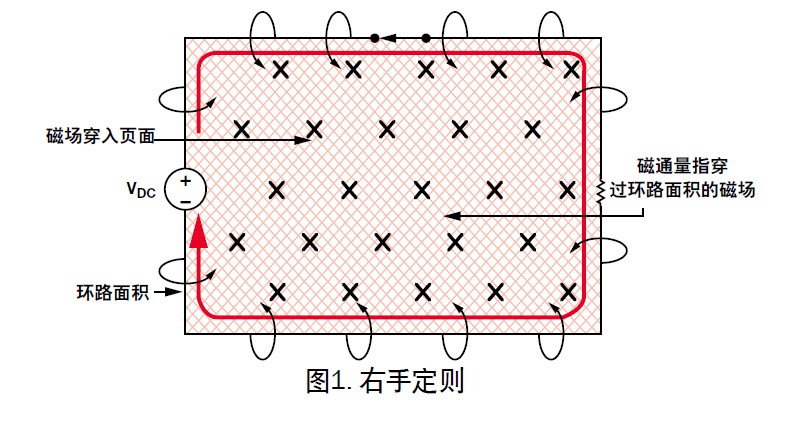

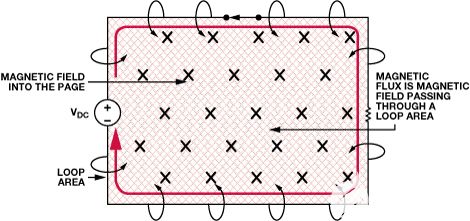

接地反彈是晶體管開關過程中發生的一種噪聲,當PCB接地和芯片封裝接地電壓不同時。

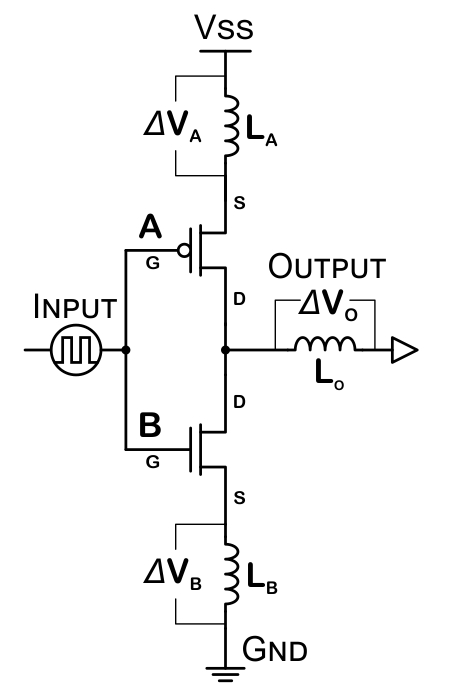

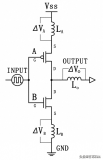

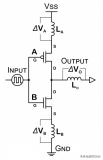

為了幫助解釋接地反彈的想法,請舉例說明。下面的推挽電路可以提供邏輯低電平或邏輯高電平輸出。

圖1。 推挽電路

電路由兩個MOSFET組成:上部p溝道MOSFET的源極連接到Vss,漏極連接到輸出引腳。下部n溝道MOSFET有其漏極連接到輸出引腳,其源極接地。

這兩種MOSFET類型對MOSFET柵極電壓的響應相反。 MOSFET柵極上的輸入邏輯低信號將使p溝道MOSFET將Vss連接到輸出,而n溝道MOSFET將輸出與Gnd斷開。 MOSFET柵極上的輸入邏輯高信號將導致p溝道MOSFET將其Vss與輸出斷開,并使n溝道MOSFET將輸出與Gnd連接。

將IC芯片上的焊盤連接到IC封裝的引腳是微小的鍵合線。這些機械必需品具有少量電感,由上面的簡化電路建模。電路中肯定存在一定數量的電阻和電容,這些電阻和電容沒有建模,也不一定需要理解以下概述。

全橋開關的等效電路中顯示了三個電感器。電感符號表示封裝電感(IC封裝設計中固有的電感),電路輸出連接到某些元件(不允許浮動)。

想象一下在輸入被保持后遇到這個電路在很長一段時間后處于邏輯低電平。這種狀態會導致上部晶體管通過上部MOSFET將電路輸出連接到Vss。經過適當長時間后,L O 和L A 中存在穩定的磁場,ΔV O 的電位差ΔV A ,ΔV B 為0伏。少量電荷將存儲在跡線中。

輸入邏輯切換到低電平,上部MOSFET將Vss與輸出斷開,下部柵極將觸發下部MOSFET將電路輸出連接到GND。

這是有趣的事情發生的地方 - 目前輸入邏輯發生變化,后果在整個系統中移動。

接地反彈的原因

輸出和地之間的電位差導致電流從通過下部MOSFET輸出到地。電感器使用存儲在其磁場中的能量來建立電位差,并且跨越ΔV O 和ΔV B ,試圖抵抗磁場的變化。

即使它們是電連接的,輸出和地之間的電位差也不會立即為0 V.請記住,輸出先前為Vss,MOSFET B的電源先前為0 V電位。先前的電位差將導致電流在輸出線放電時流動。

在電流開始從輸出下降到地的同時,封裝的電感特性會產生電位差。 ΔV B 和ΔV O 試圖保持先前建立的磁場。

電感L B 和L O 改變MOSFET的源極和漏極電位。這是一個問題,因為MOSFET柵極電壓以芯片封裝的地為參考。當電路在柵極觸發閾值附近振蕩時,輸入電壓可能不再足以保持柵極開路或導致其打開多次。

當電路再次切換時,類似情況會導致在ΔVA之間建立的電位可以將MOSFET A的源極電壓降低到觸發閾值以下。

為什么IsGround反彈不好?

目前輸入改變狀態,輸出和MOSFET不再處于定義狀態 - 它們介于兩者之間。結果可能是錯誤切換或雙切換。此外,IC芯片上任何其他共享相同的Gnd和Vss連接的部件都會受到開關事件的影響。

但接地反彈的影響不僅限于IC芯片。正如ΔVB強制MOSFET源極電位高于0V一樣,它會強制電路電位低于0V。您看到的大部分圖像都顯示出反彈效果。

如果您同時切換多個門,效果復雜,可以完全破壞你的電路。

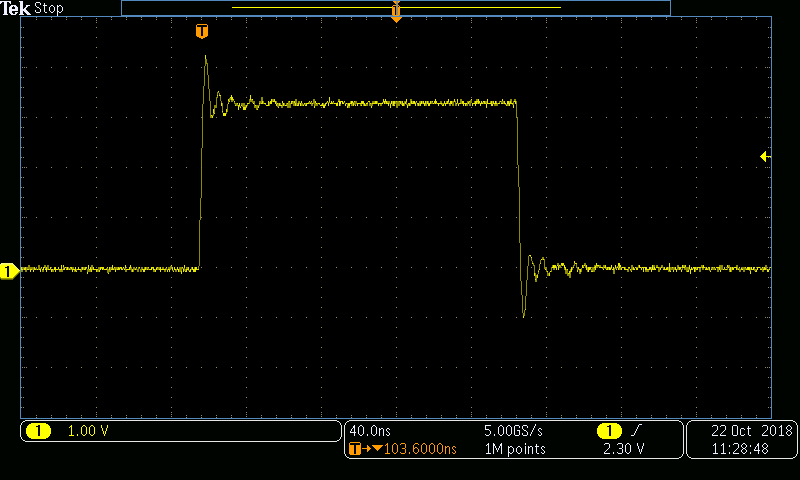

你可以在下面的例子中看到反彈。

圖2中的信號線顯示了重要的Gnd和Vss反彈。 BeagleBone Black計算機連接并激活了LightCrafter斗篷。

這里,在切換期間3.3V線路上產生大約~1V的噪聲,在最終落入背景線之前在信號線中繼續明顯共振噪音。

圖2. 來自BeagleBone Black的信號線,連接并激活LightCrafter蓋。

噪聲不僅限于切換的門。開關門連接到IC電源引腳,PCB通常共用公共電源和接地軌。這意味著噪聲很容易通過Vss上的直接電氣連接和芯片上的接地或PCB上走線的耦合傳遞到電路中的其他位置。

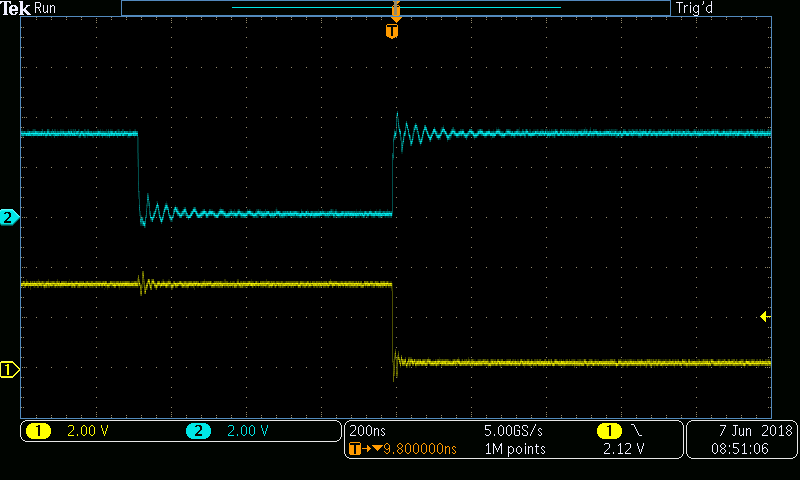

圖3. 此圖片是從附有LightCrafter斗篷的BeagleBone Black拍攝的。

在圖3中,通道2(上面的青色顯示)顯示了無阻尼信號線中的地和Vss反彈。問題非常嚴重,它通過電報傳輸到通道1上的信號線不同(以黃色顯示)。

降低接地反彈的方法:PCB設計技巧

方法#1:使用去耦電容器來定位接地反彈

降低接地反彈的首選解決方案是在每個電源軌和地之間安裝SMD去耦電容,盡可能靠近IC。遠距離去耦電容具有較長的走線,可以增加電感,因此遠離IC安裝它們對您沒有任何好處。當IC芯片上的晶體管開關狀態時,它們將改變芯片上的晶體管和本地電源軌的電位。

去耦電容為IC和IC提供暫時的低阻抗,穩定電位。定位反彈效果,防止其擴散到電路的其余部分。通過使電容器靠近IC,可以最大限度地減少PCB走線中的電感環路面積并減少干擾。

新設計人員的注意事項:去耦電容并不總是顯示在原理圖上有時在數據表中沒有提到。這并不意味著設計不需要它們。去耦電容被認為是成功設計的基礎,作者會假設您知道您需要它們,有時會從原理圖中移除它們以減少混亂。選擇100nf(0.1 uF)X7R或NP0陶瓷,除非數據表另有指示。

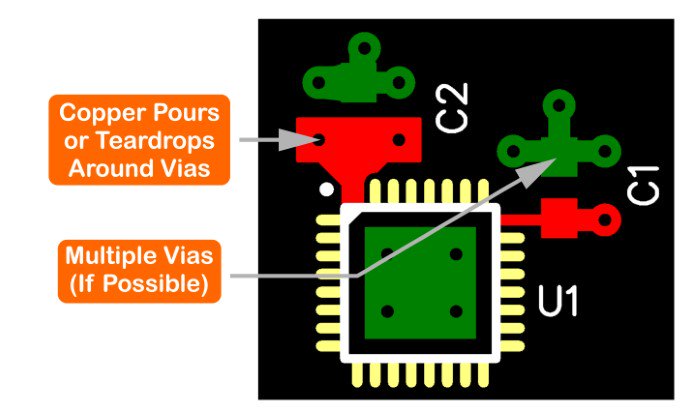

混合信號IC通常具有獨立的模擬和數字電源引腳。 您應在每個電源輸入引腳上安裝去耦電容。電容應位于IC和連接到PCB上相關電源層的多個過孔之間。

去耦電容應連接到帶過孔的電源層。

多個過孔是首選,但由于電路板尺寸要求,通常不可能。如果可以,使用銅澆注或淚珠連接過孔;如果鉆頭稍微偏離中心,額外的銅有助于將通孔連接到跡線。

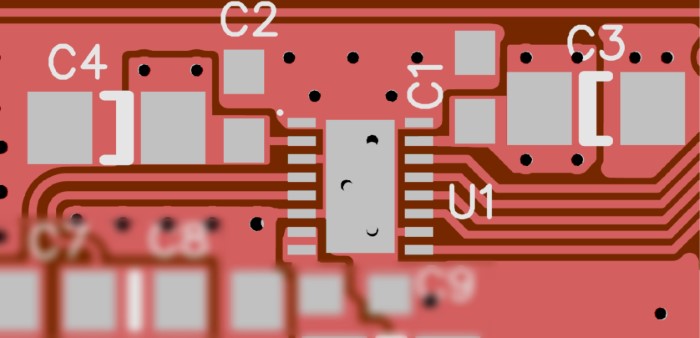

上面顯示的是IC(U1)和四個電容(C1,C2,C3,C4)的銅焊盤。 C1和C2是用于高頻干擾的去耦電容。根據 數據表 建議將C3和C4添加到電路中。由于對其他平面的限制,通過放置并不理想。

有時在物理上不可能將去耦電容放在IC附近。但是,如果你將它放置在遠離IC的地方,你就會產生一個感應回路,使你的接地反彈問題變得更糟。幸運的是,這個問題有解決辦法。

去耦電容可以放在相反的位置在IC下面的電路板的一側。

并且,在絕望的情況下,您可以使用相鄰層上的銅在電路板內部制造自己的電容器。這些被稱為嵌入式平面電容器,由并行的銅澆注組成,由PCB中非常小的介電層隔開。這類電容器的另一個好處是唯一的成本是設計人員的時間。

方法#2:使用電阻器來限制電流

使用串聯的限流電阻,以防止過多的電流流入和流出IC。

這不僅有助于降低功耗,還可以防止設備過熱,但會限制電流從輸出線通過MOSFET流向Vss和Gnd軌道,減少接地反彈。

方法#3:使用布線來降低電感

如果可能,保留相鄰跡線或相鄰層的返回路徑。由于存在厚芯材料,電路板上第1層和第3層之間的距離通常是第1層和第2層之間距離的幾倍。信號和返回路徑之間的任何不必要的分離都會增加該信號線的電感以及隨后的反彈效應。

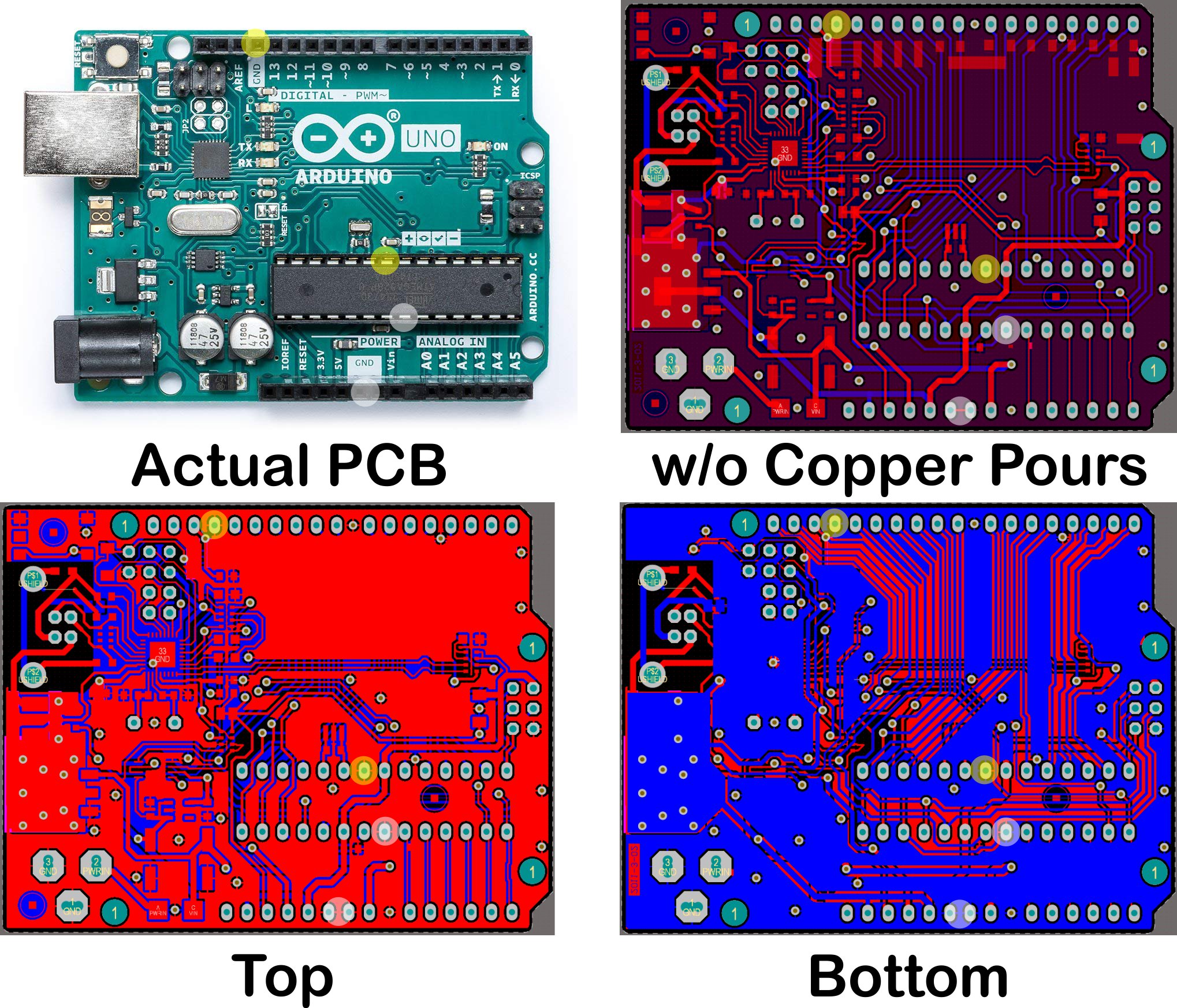

讓我們評估一個真實的電路板示例。在下圖中,您可以看到Arduino Uno的PCB布局。

模擬和數字 Gnds 在分別為白色和黃色。

正如您所看到的,電路板具有用于模擬和數字的獨立接地返回引腳,這很好。然而,董事會的布局否定了分離它們的任何積極影響。 IC的數字接地引腳和插頭行上的接地引腳之間沒有明確而直接的路徑。

信號將從IC中取出迂回路徑到達引腳引腳和通過回路的復雜路徑接地引腳。因為Arduino Uno是這個星球上最受歡迎的電路板之一,所以這是一個很好的例子,“你布局電路板的方式并不重要。”

如果這個例子激起了你的好奇心,查看我們關于Arduino Uno硬件設計的文章。

通過編程和設計考慮減少接地反彈

接地反彈中斷隨著開關門數量的增加而增加。如果可能,在你的設計中,用一個很短的延遲來偏移開關門。

例如,你可能有一個設計以不同的間隔(1秒,2秒,3秒等)閃爍各種LED 。。。)表示您的設計狀態。當所有三個LED同時切換時,接地反彈效應將最大程度地影響電路。

在此示例中,您可以通過略微偏移LED來減輕接地反彈的影響,因此它們不會完全同步。在LED之間引入1ms的偏移對于您的用戶來說是難以察覺的,但會將地面反彈效應降低~3倍。

最佳實踐摘要

接地和Vss彈跳是由對快速上升/下降時間的感應響應引起的。您可以通過適當的布局和電路板設計實踐來最小化接地反彈對電路的影響。

一些減少接地的方法反彈包括:

保持去耦電容盡可能靠近IC。

選擇上升/下降時間較慢的IC。

同時防止盡可能切換。

-

pcb

+關注

關注

4319文章

23111瀏覽量

398228 -

噪聲

+關注

關注

13文章

1122瀏覽量

47429 -

晶體管

+關注

關注

77文章

9698瀏覽量

138321

發布評論請先 登錄

相關推薦

pcb設計如何減少接地反彈問題?

PCB設計如何減少接地反彈?

減少地環路影響的方法

減少DC-DC變換器中接地反彈的方法

接地的系統方法接地的系統方法

減小DC/DC變換器中的接地反彈-一些接地要點

如何地面反彈降低技術設計電路?

DC/DC開關電源的接地反彈

DC/DC開關電源中接地反彈的詳解

減少DC-DC轉換器中的接地反彈—一些接地要點

減少接地反彈的方法概述

減少接地反彈的方法概述

評論