標準時鐘信號波形是梯形的周期數字脈沖,如圖1所示,脈沖周期為T;信號上升時間為tr;信號下降時間為tf。假設tr=tf,高電平維持時間為to,定義數字脈沖寬度為τ=to+tr。

圖1 數字時鐘信號

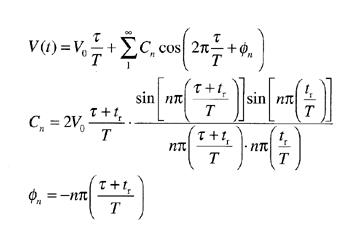

將此時鐘信號作傅里葉展開如下:

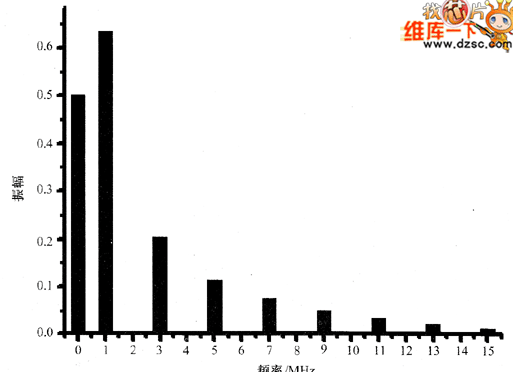

通過上式的傅里葉展開可以得到此時大致的時鐘信號離散頻譜,如圖2所示。可見數字信號的頻譜并不局限于其時鐘頻率,而是覆蓋很寬的頻率范圍。例如,一個時鐘頻率為33 MHz的數字系統,它的三次諧波分量接近100 MHz。電路板上的元件、走線、封裝、連接器等互連結構在33 MHz時可能不會帶來問題,但是對于100 MHz的諧波,趨膚效應、傳輸線效應開始出現,并影響信號的完整性。隨著頻率的升高,一段不起眼的導線、一個封裝引腳都可能像天線一樣輻射電磁波,帶來電磁兼容性問題。此外,系統互連對不同頻率的衰減不同,頻率越高,衰減越大,這就可能帶來信號波形退化等一系列問題。

圖2 時鐘信號的頻譜

來源:維庫電子市場網

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

pcb

+關注

關注

4319文章

23083瀏覽量

397561 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43036

發布評論請先 登錄

相關推薦

高速pcb與普通pcb的區別是什么

的區別,包括設計原則、材料選擇、制造工藝和性能特點等方面。 一、設計原則 1. 信號完整性(Signal Integrity,SI):高速PCB設計需要關注信號完整性,以確保

頻譜儀怎么測信號功率多少

頻譜儀是一種用于測量信號頻率和幅度的儀器,廣泛應用于通信、電子、射頻等領域。本文將詳細介紹如何使用頻譜儀測量信號功率。 1. 頻譜儀的基本原

高速PCB設計,信號完整性問題你一定要清楚!

隨著集成電路輸出開關速度提高以及PCB板密度增加,信號完整性(英語:Signalintegrity,Sl)已經成為高速數字 PCB設計 必須關心的問題之一。元器件和

高速PCB信號走線的九大規則

由于 PCB 板的密度越來越高,許多 PCB LAYOUT 工程師在走線的過程中,較容易出現一種失誤,即時鐘信號等高速信號網絡,在多層的

發表于 01-08 15:33

?1478次閱讀

PCB高速信號的頻譜是怎樣的

PCB高速信號的頻譜是怎樣的

評論