當(dāng)發(fā)現(xiàn)數(shù)字電路出現(xiàn)電磁干擾現(xiàn)象后,主要的原因是在電源線和地線上,用示波器可以觀察到明顯的噪聲電壓。雖然許多人可以斷定這些噪聲是造成電路電磁干擾問題的原因,但卻不知道采取何種手段來解決。為了達(dá)到消除噪聲的目的,有必要首先明白這些噪聲是如何產(chǎn)生的。

1,電源線上的噪聲

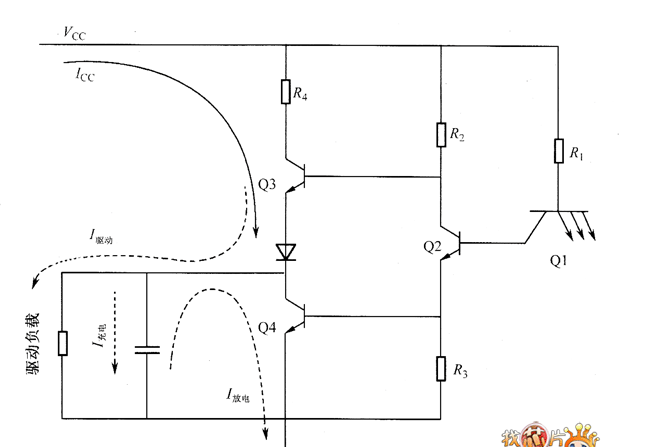

如圖1所示是比較典型的門電路輸出級(jí),當(dāng)輸出為高電平時(shí),Q3導(dǎo)通,Q4截止;當(dāng)輸出為低電平時(shí),Q3截止,Q4導(dǎo)通。這兩種狀態(tài)都會(huì)在電源與地之間形成高阻抗,這樣就限制了電源的電流。

圖1 典型的門電路輸出級(jí)

而當(dāng)狀態(tài)發(fā)生變化時(shí),暫時(shí)會(huì)有Q3和Q4管同時(shí)導(dǎo)通,這時(shí)在電源和地之間形成了短暫的低阻抗,產(chǎn)生了30~100 mA的尖峰電流。當(dāng)門輸出電平從低變?yōu)楦邥r(shí),電源不僅要保持輸出電流,還要給寄生電容充電,使這個(gè)電流峰值達(dá)到飽和。由于電源線有不同程度的電感,因此當(dāng)電流發(fā)生突變時(shí),則產(chǎn)生感應(yīng)電壓。這就觀察到在電源線上的噪聲。由于存在電源線阻抗,所以會(huì)造成電壓的短暫跌落。

2.地線上的噪聲

當(dāng)產(chǎn)生上述尖峰電流的同時(shí),地線上也會(huì)流過電流,特別是當(dāng)輸出電平從高變?yōu)榈蜁r(shí),寄生電容放電,地線上的峰值電流更大。由于地線總有不同程度的電感,也會(huì)感應(yīng)出電壓,這就形成了地線噪聲。地線和電源線上的噪聲不僅會(huì)使電路運(yùn)行不好,還會(huì)產(chǎn)生較強(qiáng)的電磁輻射。

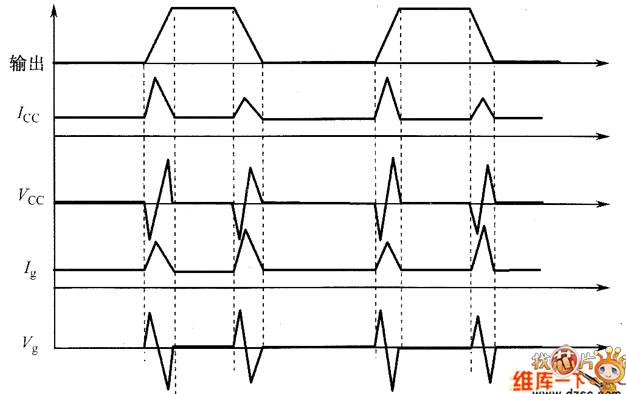

如圖2所示就是形成的電源線、地線噪聲電壓波形。

·“Icc”(電源上電流):在不同的輸出狀態(tài)時(shí),幅值是不同的。穩(wěn)定時(shí),電流也穩(wěn)定。

當(dāng)輸出從低變?yōu)楦邥r(shí),瞬間短路,電流增加,同時(shí)給寄生電容充電,電流更大;當(dāng)輸出電平從高變?yōu)榈蜁r(shí),瞬間短路,電流增加,但不給寄生電容充電,因此電流較輸出電平從低變高時(shí)要小。

· 電壓“Vcc”(電源上電壓):當(dāng)Icc發(fā)生突變時(shí),電源線的電感L會(huì)產(chǎn)生感應(yīng)電壓“Ldi/dt”。

“Ig”(地線電流):電源線上的電流與電路中寄生電容放電而形成的電流。輸出穩(wěn)定,電流穩(wěn)定。當(dāng)輸出電平從低變高時(shí),瞬間短路,電流增加。當(dāng)輸出電平從高變低時(shí),瞬間短路,電流增加,同時(shí)寄生電容放電,電流峰值較輸出電平從低變高時(shí)更大。

“Vg”(地線電壓):當(dāng)“Ig”發(fā)生突變時(shí),地線的電感L會(huì)有感應(yīng)電壓“Ldi/dt”產(chǎn)生。

圖2 電源線、地線噪聲電壓波形

雖然解決地線噪聲電壓的方法可以在線路板上設(shè)置電源線網(wǎng)格來減小電感量,但要占有大量的布線空間。為了減小電源線電感量,可采取下面的方法:

采用儲(chǔ)能電容,其作用是為芯片供給電路輸出狀態(tài)發(fā)生變化時(shí)所需的大電流,這樣就減小了感應(yīng)出的噪聲電壓,避免了電流突變。儲(chǔ)能電容將電流變化限制在較小的范圍內(nèi),減小了輻射,所以在線路板上使用電源線網(wǎng)格或電源線面(電源系統(tǒng)具有很小的電感)時(shí)增加一些儲(chǔ)能電容。

因?yàn)閮?chǔ)能電容是為芯片提供瞬態(tài)高能量,所以在布線階段要盡量靠近芯片,也就是使儲(chǔ)能電容的供電回路面積盡量小,或使儲(chǔ)能電容與芯片電源端和地線端之間的走線盡量短。

芯片與儲(chǔ)能電容之間的走線長(zhǎng)度是芯片自身引腳的長(zhǎng)度加上線路板走線的長(zhǎng)度。因此,要減小這兩部分的總長(zhǎng)度,就得選用電源引腳與地引腳靠得很近的芯片,避免使用芯片安裝座、表面安裝形式的芯片等。

另外,每個(gè)芯片的儲(chǔ)能電容在放電結(jié)束后,都要及時(shí)補(bǔ)充電荷,為下次放電做好準(zhǔn)備。為了減小對(duì)電源系統(tǒng)的騷擾,可通過稱為二級(jí)儲(chǔ)能的電容來提供電荷。當(dāng)線路板上的芯片較少時(shí),一只二級(jí)儲(chǔ)能電容安裝在電源線的入口處就可以了,該二級(jí)儲(chǔ)能電容的容量應(yīng)為芯片儲(chǔ)能電容總?cè)萘康?倍以上。如果線路板上芯片較多,每5~10片設(shè)置一個(gè)二級(jí)儲(chǔ)能電容。這個(gè)電容應(yīng)該使用鉭電容,并且要求串聯(lián)電感盡量小,不要使用鋁電解電容而導(dǎo)致內(nèi)部電感的產(chǎn)生。

-

pcb

+關(guān)注

關(guān)注

4370文章

23511瀏覽量

410209 -

電路板

+關(guān)注

關(guān)注

140文章

5138瀏覽量

102825 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

43948

發(fā)布評(píng)論請(qǐng)先 登錄

用了 10 年網(wǎng)才明白!"帶寬”“寬帶”原來不是一回事!#帶寬 #寬帶 #數(shù)據(jù)采集卡 #模擬信號(hào) #電路知識(shí)

電路板上助焊劑殘留的處理方法

今天帶你來看看防逆流是什么?光伏防逆流又是怎么一回事?

讓人欲罷不能樹莓派貪吃蛇掌機(jī)!

深度解析:雙面PCB板與單面PCB板的制造差異

用兩臺(tái)Fluke 5720提供了一對(duì)差分信號(hào),實(shí)測(cè)出來的非線性卻有100ppm左右,為什么?

為什么TLC7135C初始加電后D1~D5數(shù)字輸出時(shí)0,直到對(duì)引腳3(ANLG COMMON)觸碰一下,才開始正常數(shù)值輸出?

PCB線路板阻抗是怎么回事?帶你了解多層阻抗線路板的作用!

Laird Eccosorb吸波材料的應(yīng)用案例

評(píng)論