步驟1:啟動Quartus

1如果尚未安裝Quartus,請在您的計算機上安裝。

注意:由于我使用的是校園計算機,因此不必安裝Quartus。遵循安裝向導,一切正常。

2)從主窗口中打開Quartus。

3)應出現項目向導。單擊創建一個新項目。

參見圖片

4)第一頁告訴您有關項目向導的信息。單擊下一步轉到下一頁。

5)選擇要工作的目錄。

注意:任何目錄都可以。只是在這里保存文件。最好為您執行的任何項目創建一個文件夾。

6)將項目命名為4BitAdder。這還將顯示為頂層設計實體。

7)單擊到下一頁。

8)我們將從頭開始,除了程序中包含的基礎知識之外,因此請再次單擊“下一步”。

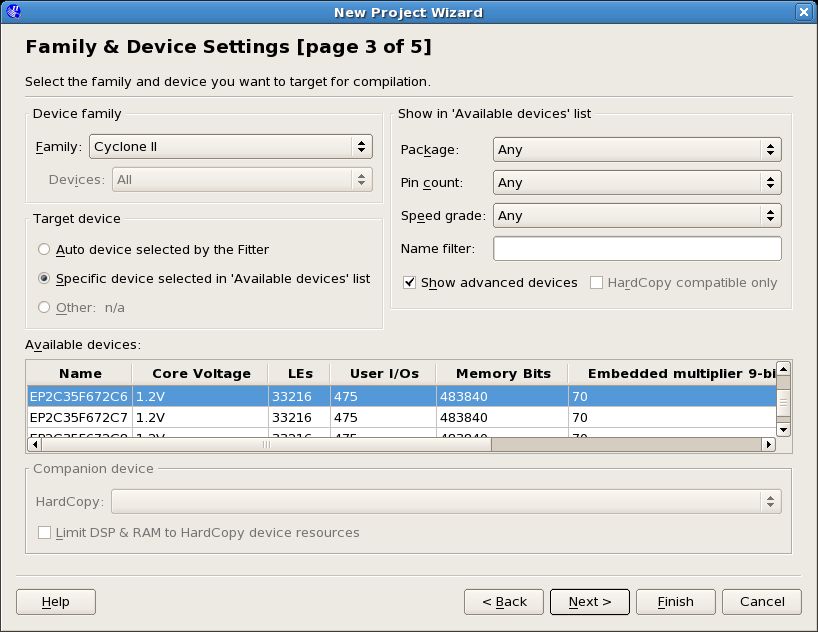

9)選擇您擁有的FPGA的家族名稱。 (旋風,地層等)。

10)您的設備在滾動欄中將具有特定名稱。選擇它并點擊完成。最后兩頁將保持不變。

a)要弄清楚設備的系列名稱和特定名稱,請在FPGA上找到處理器。它是上面寫有ALTERA的更大芯片。

b)姓氏將在第二行顯示,且打印尺寸比ALTERA稍小。 c)姓氏下方是設備的特定名稱,其中包含字母和

請參見圖片

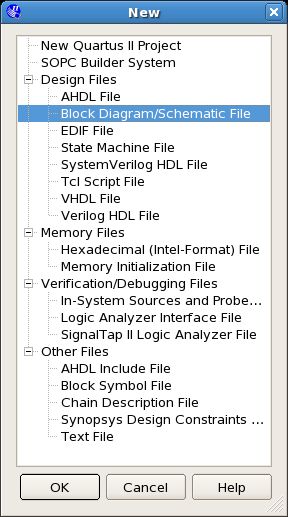

11)該項目將加載空白屏幕,顯示Altera Quartus II。在左上角,單擊“文件”,然后從出現的下拉菜單中單擊“新建”。

12)從出現的窗口中選擇“框圖/原理圖文件(BDF)”。屏幕將變為白色,并帶有小點。

請參見圖片

13)立即將文件保存為名稱4BitAdder。出現保存屏幕時,該文件應默認為該名稱。

注意:要保存,請單擊文件,然后另存為。添加零件后,也可以單擊工具欄中的軟盤進行保存。

警告:請經常保存。已知計算機和軟件會崩潰。為了避免丟失信息和重做步驟,請隨時考慮保存文件。

此文件將是主項目所在的位置。較小的組件將在其他文件中創建并制成一個塊,其中僅看到輸入和輸出,而沒有所有的門和混亂。這些塊較小,為項目創建的混亂程度較小。

步驟2:時鐘發生器

時鐘驅動整個電路。最初,時鐘產生于10MHz,對于我們的使用而言太快了。時鐘將使用T觸發器按比例縮小。您的時鐘頻率可能不同。檢查一下它的頻率,并調整T觸發器的數量。我們的電路=(10 ^ 7)/(2 ^ 28)。將時鐘設置為正確的頻率可確保添加過程不會太快且不會超出您的控制范圍。

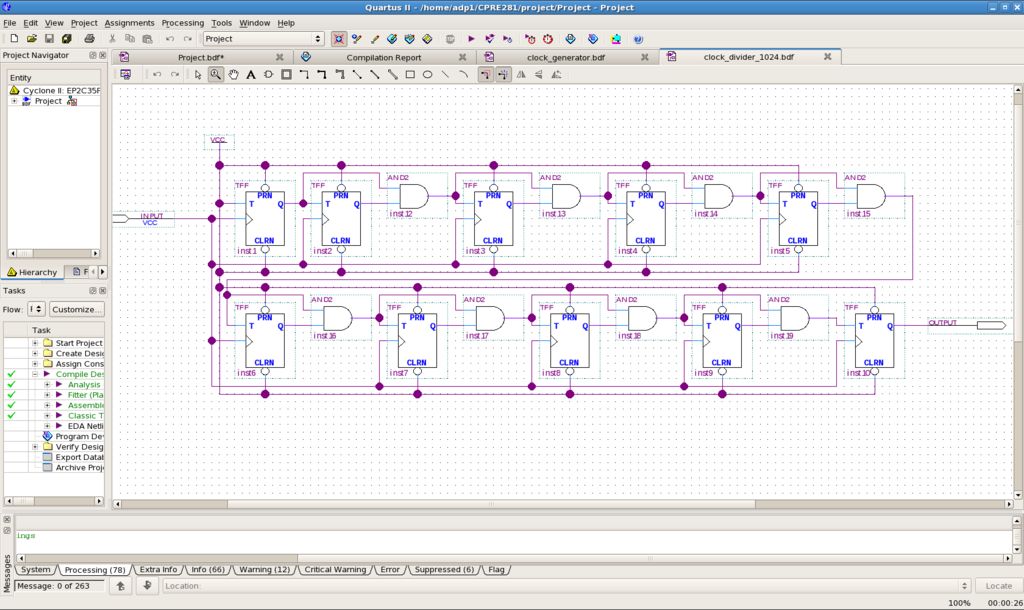

1)開始一個名為clock_divider_1024的文件。文件-》新建

b)選擇BDF

c)以給定名稱保存

2)在該空間中放置10個T型觸發器。

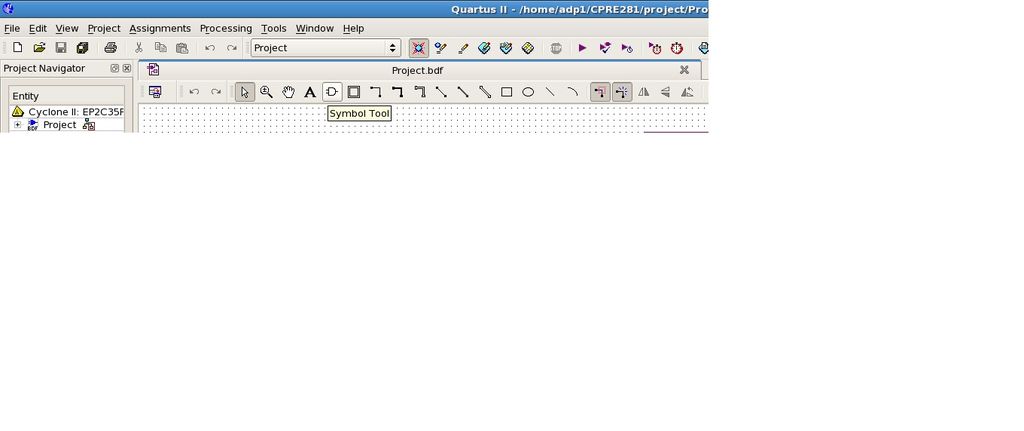

a)1)要添加組件,請單擊工具欄中的符號工具。 (它看起來像是D,左側有兩根電線,右側有一根。)

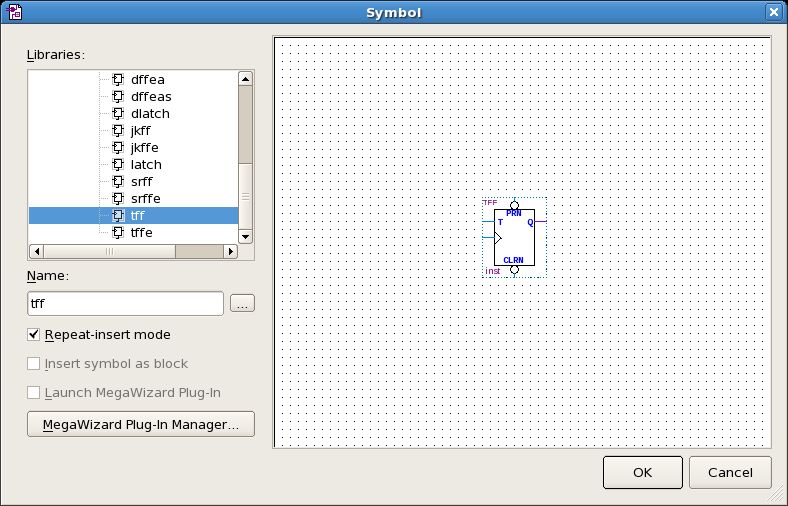

參見圖片 a)2)您也可以雙擊空白區域以打開符號窗口。

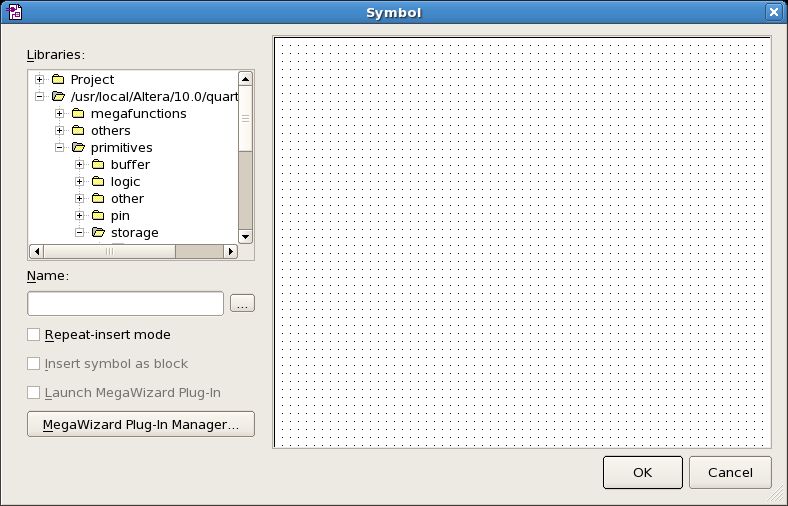

b)符號窗口加載了兩個庫。一個將項目中所有的文件都制作成更簡單的塊。另一個是Quartus隨附的默認庫。單擊默認庫旁邊的+展開。

請參見圖片。c)我們的組件位于基本文件夾下。單擊+將其展開。

d)觸發器在存儲文件下。單擊+將其展開。

e)選擇tff。 f)由于需要倍數,因此單擊選項“重復插入模式”。

g)按OK,然后在空白處單擊以添加T型觸發器。 (單擊一次)

注意:要停止任何命令或離開新窗口,請按退出鍵。

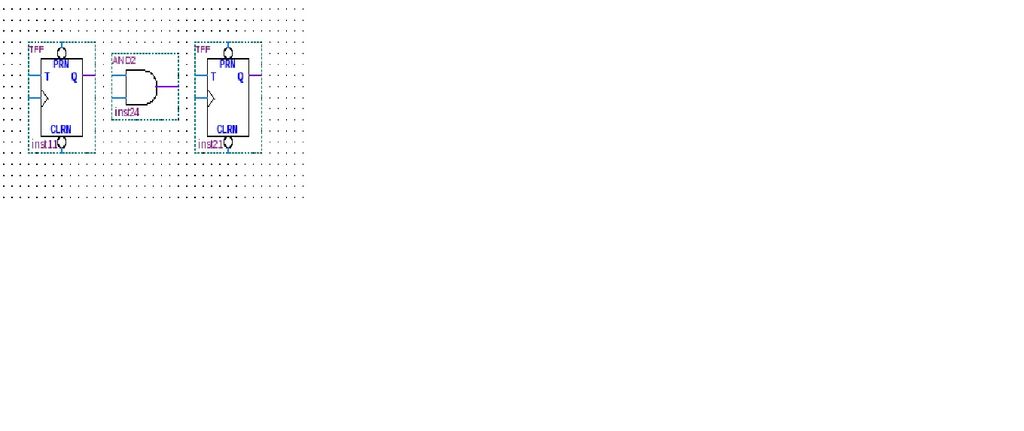

請參見圖片

3)將觸發器分成兩個水平行,每行5個。在觸發器之間留出大約2塊空間。

注意:對于這些指令,1塊區域將與觸發器相同。

請參見圖片

4)添加8個2輸入與門。 》 a)像打開T觸發器一樣打開符號窗口。 b)文件夾仍應展開。通過單擊+展開邏輯文件夾。c)選擇AND2。我們想要倍數,因此請確保單擊選項“重復插入模式”。

d)單擊以添加AND門。

5)將AND門置于每個觸發器之間,從第二個觸發器之后開始。

注意:最好從左到右進行電路流動。

a)如果您已經添加了AND門并且需要排列它們,只需單擊并拖動即可。將鼠標左鍵放到要打開門的位置。

6)在第一個觸發器之前添加一個輸入引腳。

a)引腳位于PIN文件夾下。展開它以選擇輸入選項卡。

7)通過雙擊pin_name并更改它來標記輸入引腳CLK_IN。

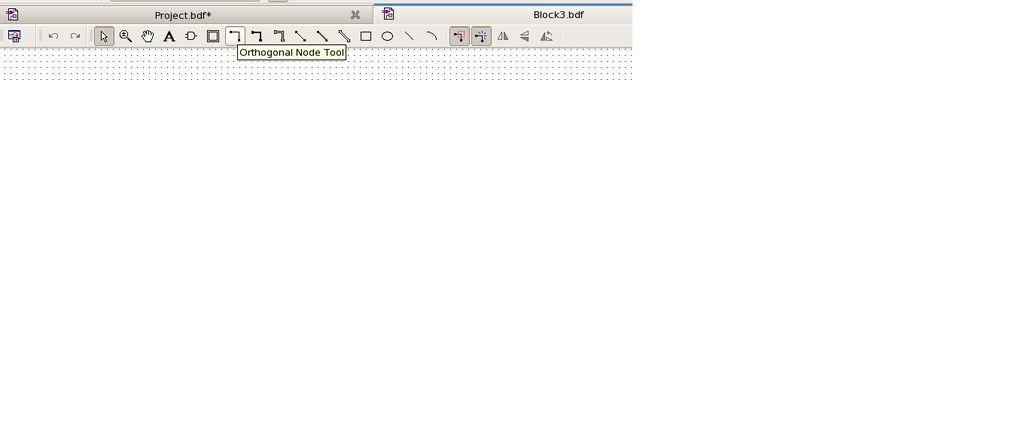

8)單擊正交節點工具。

請參見圖片

9)連接T觸發器上每個三角形的輸入引腳,也稱為時鐘輸入。 a)單擊并拖動以創建導線。確保電線連接到每個組件上的電線。

警告:當三根或更多根電線以直角相交時,會形成一個“節點”。該節點看起來像一個點。請注意哪些電線正在相互連接。

10)從零件清單中添加VCC。

a)VCC位于“ other”文件夾下。

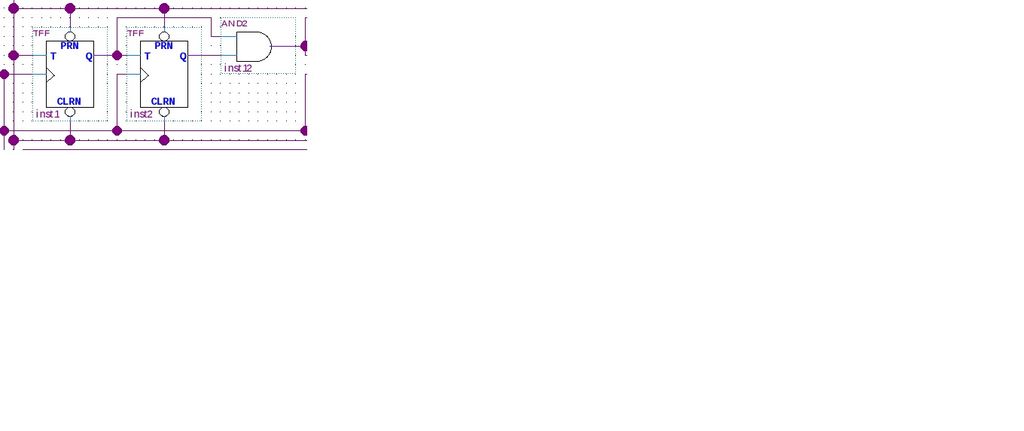

11)使用正交節點工具,將VCC連接至T的T。第一個觸發器以及每個觸發器的PRN和CLRN。

12)將第一個觸發器的Q連接到第二個觸發器的T。

參見圖片

13)連接每個AND門的一個輸入。

14)將“與”門的另一個輸入連接到它前面的觸發器的T。

15)將“與”門的另一個輸入連接到它前面的觸發器的T。《15》

16)添加一個輸出引腳。

參見圖片

17)標記輸出引腳CLK_OUT。

18)將最后一個觸發器的Q連接到輸出引腳。

T觸發器用作時鐘分頻器。通過將第一觸發器的T連接到VCC(高電壓),第一觸發器在每個時鐘周期將其輸出Q(從1切換為0或反之亦然)。 Q連接到第二個觸發器的T,因此第二個觸發器的Q僅在其T為1且時鐘從0變為1時才切換其值。從那里開始,每個其他觸發器都需要在每個觸發器之前在將其從0更改為1之前,它的值為1。每個時鐘周期的周期變得更長,從而降低了時鐘的速度。

19)保存文件。

20)使文件可用作塊,單擊“處理”,然后分析當前文件。

21)分析完文件后,單擊文件,向下進行創建/更新,然后從旁邊顯示的菜單中單擊“為當前文件創建符號文件”。 。

我們的電路現在已被制成一個隱藏了內部零件的塊,并且僅顯示輸入和輸出。僅當在其他文件中使用原始電路時,才會更改原始電路。要在另一個項目中使用,必須將每個電路文件的.bdf和.bsf文件復制到該項目的文件夾中。

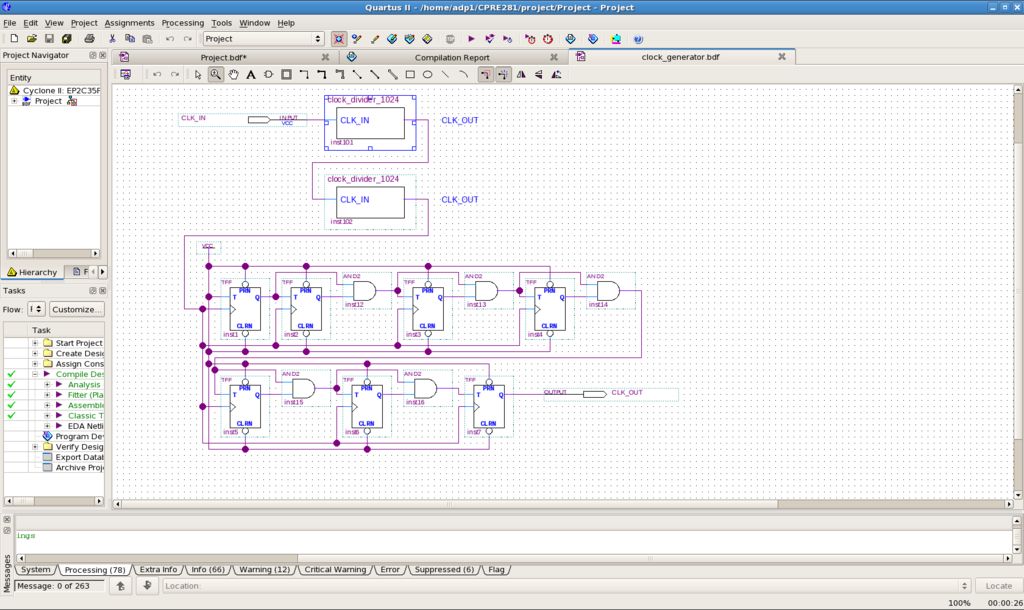

22)打開一個新文件(bdf),并將其命名為clock_generator。

23)在其中添加2個

a)在組件窗口中,展開4BitAdder文件夾。 b)選擇clock_divider_1024并將其添加到文件中。

24)從clock_divider_1024文件中,復制整個電路并粘貼到新文件中。

25)將觸發器的數量減少到8個,與門的數量減少到6個。

這可以通過以下方法完成:a)刪除第8個觸發器之后的所有內容, 將第8個觸發器的Q連接到輸出引腳。 c)刪除將第8個觸發器的T連接到其后的AND門的導線。 br》 26)刪除將CLK_IN連接到第一個觸發器的導線。

27)將CLK_IN連接到一個Clock_divider_1024的輸入(左側)。

28)將同一clock_divider_1024的輸出(右側)連接到輸入29)將第二個clock_divider_1024的輸出連接到第一個觸發器的時鐘輸入(三角形)。

30)確保將VCC連接到每個觸發器的PRN和CLRN,如下所示:以及電路的第一個觸發器的T輸入。

參見圖片

31)保存文件。

32)分析文件。 (處理-》分析文件)

33)為文件創建符號。 (文件-》創建/更新-》創建符號)

34)在文件4BitAdder中,添加clock_generator。

步驟3:狀態機

狀態機跟蹤我們正在處理的位置,以便可以輕松地進行下一步。我們的狀態機將跟蹤裝載數量,發送每個位以進行加法并顯示最終結果。

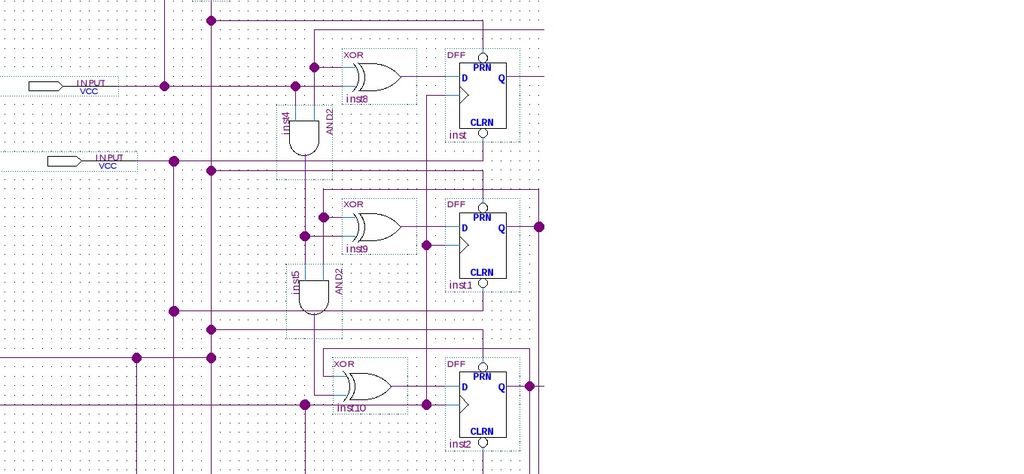

1)打開一個名為State_machine的新BDF。

2)在垂直列中使用3D觸發器添加符號工具。在它們之間保留1塊空間。3)在每個D觸發器的左側添加3個2輸入XOR門。少于一個空間是必要的,但要留出一些空間。

4)使用正交節點工具,將每個XOR門的輸出(右側)直接連接到D觸發器D的右側。

5)在頂部和底部兩個XOR門的下方和下方添加2個2輸入與門。

6)旋轉每個AND門,使2個引腳朝上。要旋轉,請單擊在組件上

b)右鍵單擊組件以顯示菜單。 c)選擇一個選項以翻轉或旋轉組件。

7)將每個“與”門的一個輸入連接到一個輸入。

8)將每個“與”門的另一個輸入連接到其上方的“異或”門的另一個輸入。

9)將每個D觸發器的Q輸出連接到以下一個: XOR門的輸入直接在其左側。

請參見圖片

10)AND門的輸出應連接至AND和XOR門的輸入,該輸入不與D的Q連接。觸發器。

注意:一個XOR輸入從D fli連接到Q。 p觸發器和與門的輸入。另一個XOR輸入連接到AND門的另一個輸入,以及如果它上面有一個AND門,則其上面的AND門的輸出。

11)對于第三個XOR門,一個輸入將連接到

12)另一個輸入連接到右側D觸發器的Q。

參見圖片《13》 13)添加VCC引腳。

推薦的位置是到當前組件的左上角

14)將VCC連接到每個D觸發器的PRN。

15)在到目前為止的左邊添加3個輸入引腳3個塊。

16)第一個輸入引腳控件。

17)將第一個輸入引腳連接到連接第一個XOR門和第一個AND門的導線。不要將它連接到連接到D觸發器Q的導線。

18)將第二個輸入引腳標記為“清除”。

19)將第二個輸入引腳連接到每個D觸發器的CLRN。

20)標記第三個輸入引腳“時鐘”。

21)連接第三個輸入引腳。每個D觸發器的時鐘輸入(三角形)的輸入引腳。

22)加3

23)標記第一個輸出引腳Select1。

24)將select1連接到第一個D觸發器的Q。

25)標記第二個輸出Select2。

26)將select2連接到第二個D觸發器的Q。

27)標記第三個輸出引腳select3。

28)將select3連接到第三個D觸發器的Q。

參見圖片

29)保存文件。

30)分析文件。

31)為文件創建符號。

32)在4BitAdder的clock_generator右側添加state_machine。

步驟4: 7段顯示器

我們也希望加法器也看起來像計算器。計算器顯示要添加的數字及其總和。為了在板上顯示我們的數字,我們的7段顯示器將采用我們數字的二進制表示形式,并將其顯示在典型的數字顯示器上。

1)用二進制寫出數字0-9,以及每個數字如何影響

注意:這些條在順時針方向上標記為AG。每個輸出A-G都會受到輸入0000-1001的影響。 (完整的7段顯示器使用十六進制,0-9和AF執行0-F,但我們將不需要它。如果以后要重用它,對AF進行編程將非常有用。我將介紹7的完整實現-段顯示。)在對7段顯示進行編程時,輸出0對應點亮的條,而1則表示不點亮。

請參見圖片

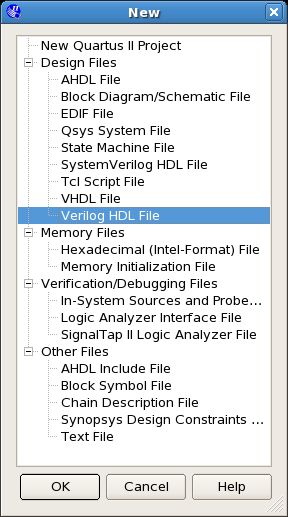

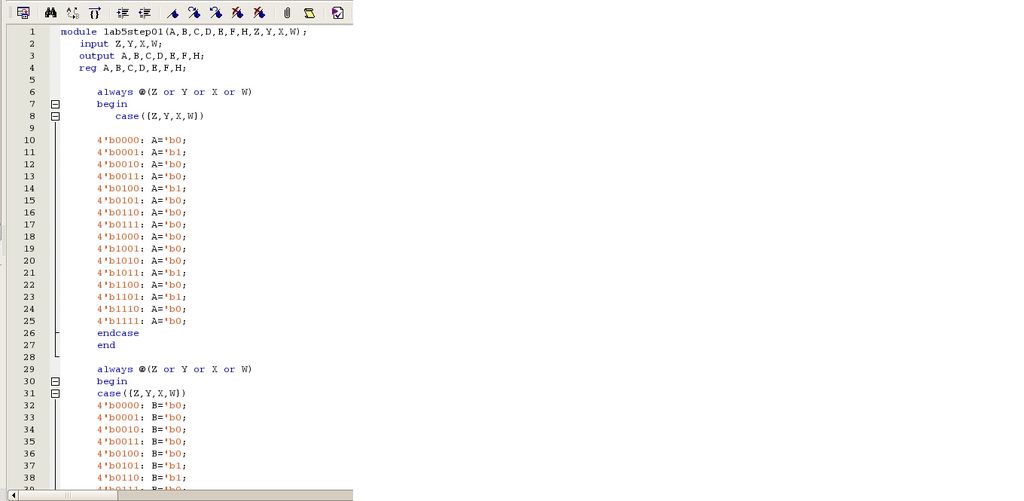

2)創建Verilog HDL文件。

請參見圖片

此文件將與其他文件不同。每個段的輸出將以二進制形式特別說明。該文件將被編碼。

3)另存為7_segment_display。

4)在第一行中,輸入“ module 7_segment_display(A,B,C,D,E,F,G,W,X,Y ,Z);”。

注意:AG是我們的輸出,與數字時鐘中的7段相對應。 W-Z是我們的輸入,對應于我們二進制數的每個數字。這些區分大小寫。保持相同。

5)在第二行中,輸入“輸入W,X,Y,Z;”。

6)在第三行中,輸入“輸出A,B,C,D,E

7)在第四行上,輸入“ reg A,B,C,D,E,F,G;”。

8)跳到第六行。

9)輸入“總是@(W或X或Y或Z)”。

10)在第7行,輸入“開始”。

11)第8行將說“ case({W,X,Y, Z})”。

第6-8行將在每種情況下開始。每種情況都包含不同的輸入可能性以及每個輸入的輸出結果。

12)跳到第10行,輸入“ 4‘b0000:A =’b0;”。

13)在線在11中,輸入“ 4‘b0001:A =’b1;”。

“ 4‘b”告訴計算機我們的輸入將是4位二進制數字,而不是十進制,十六進制或八進制。對于每個給定輸入,都給出A的輸出,該輸出只能有1個小數,對應于2個可能的輸出。

14)使用上面顯示的輸入/輸出表,并完成輸入的情況A.

15)輸入完所有大小寫后,就可以在第26行輸入了。

16)在第26行輸入了“ endcase”。

17)在第27行輸入了“

請參見圖片

18)跳到第29行,對輸出B開始相同的過程。

19)為了使代碼易于閱讀,請在每個輸出的外殼之間保留空格。 》 20)如果按照建議保留空格,則在完成輸出G的格時,下一個空行將是第161行。

21)在該空行上,輸入“ endmodule”。

22)保存文件。

23)分析文件。

24)創建7_segment_display的符號。

步驟5:Full_adder

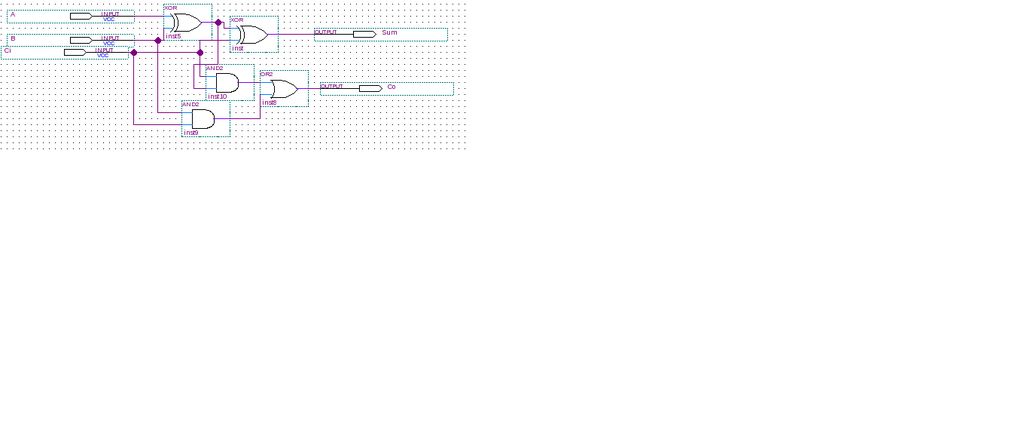

完整加法器是在整個程序中進行實際加法的設備。該組件接收兩位并執行按位加法。加法運算首先經過0的位置,然后經過1的位置,依此類推。如果前一個進位有進位,則也必須添加進位。半加法器不考慮先前數學運算中的進位。

1)創建一個新的BDF。

2)將其另存為Full_adder。

3)將2個XOR門并排添加到文件中。

4)在右XOR門下方添加2個2輸入與門。 “與”門應垂直排列。

5)在2個“與”門的右邊添加一個2輸入“或”門,大約在兩個垂直門之間。

6)將一個“或”門的輸出連接到另一個XOR門的一個輸入。

7)將同一根導線連接到頂部AND門的一個輸入。

8)將那個AND門的另一個輸入連接到右XOR門的另一個輸入。 br》 9)將“與”門的輸出連接到“或”門的輸入。

請參見圖片

10)在垂直線的左邊添加3個輸入引腳。

11 )標記頂部引腳A。

12)將A連接到左側XOR門的一個輸入和底部AND門的一個輸入。

13)標記第二個引腳B。

14)連接B

15)標記第三個引腳Ci(進位)。

16)將Ci連接到連接到XOR門的另一個輸入的導線(進位)。右XOR門與頂部AND門的輸入。

17)添加2個輸出引腳。

18)標簽一個總和。

19)連接總和到右XOR門的輸出。

20)標記第二個Co(執行)。

21)將Co連接到OR門的輸出。

參見圖片

22)保存該文件。

23)分析該文件。

24)為full_adder創建一個符號。

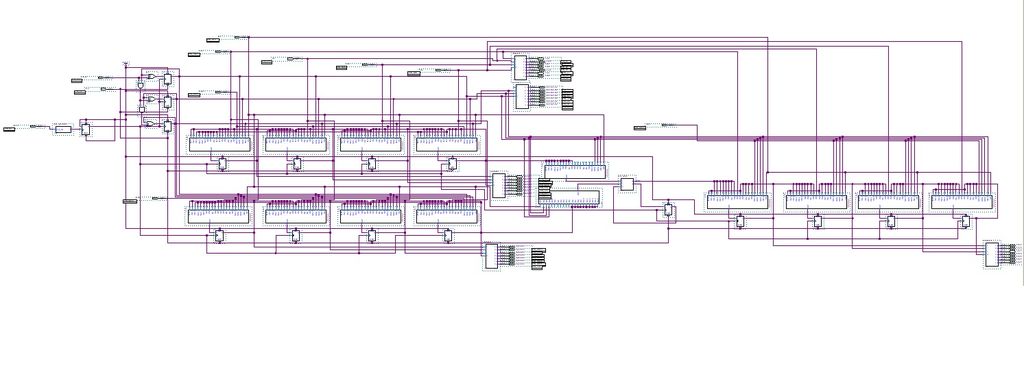

步驟6:將其放在一起

4位加法器的所有較小部分均已創建。我們剩下的部分是將組件添加到必要的位置,然后將它們連接在一起(令人困惑的部分)。

到目前為止,我們的4BitAdder中具有clock_generator和state_machine。 (clock_generator應該在狀態機的左側。)

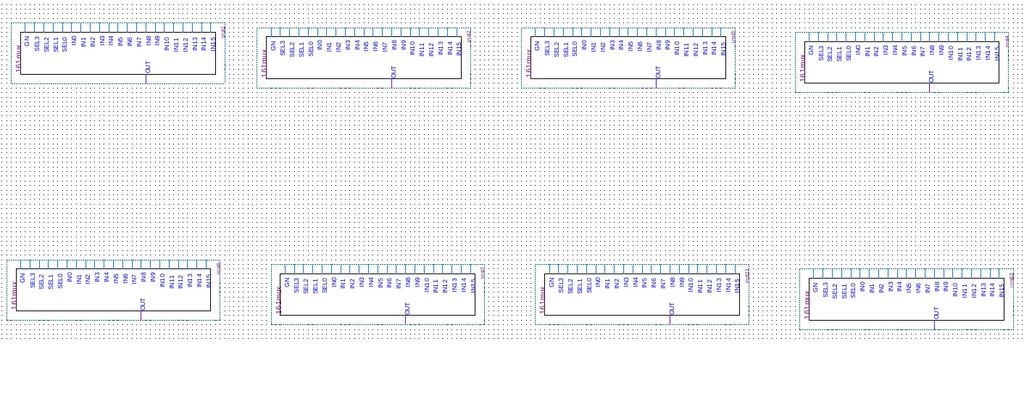

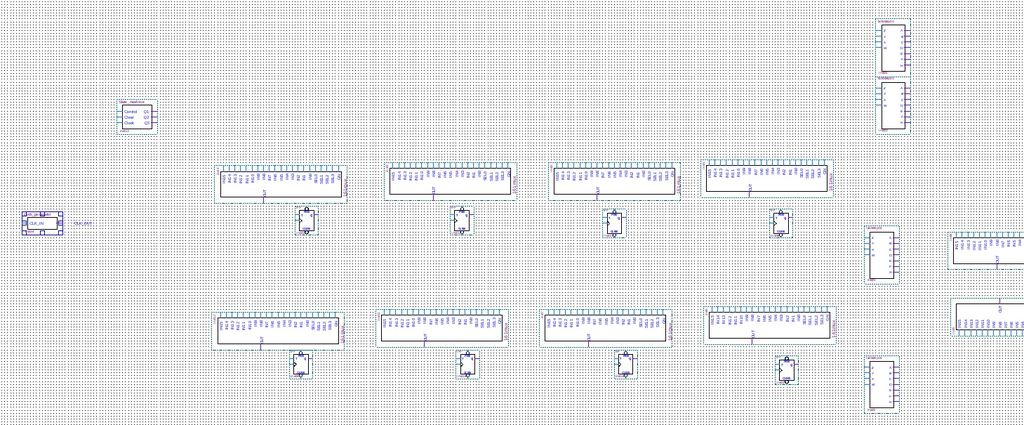

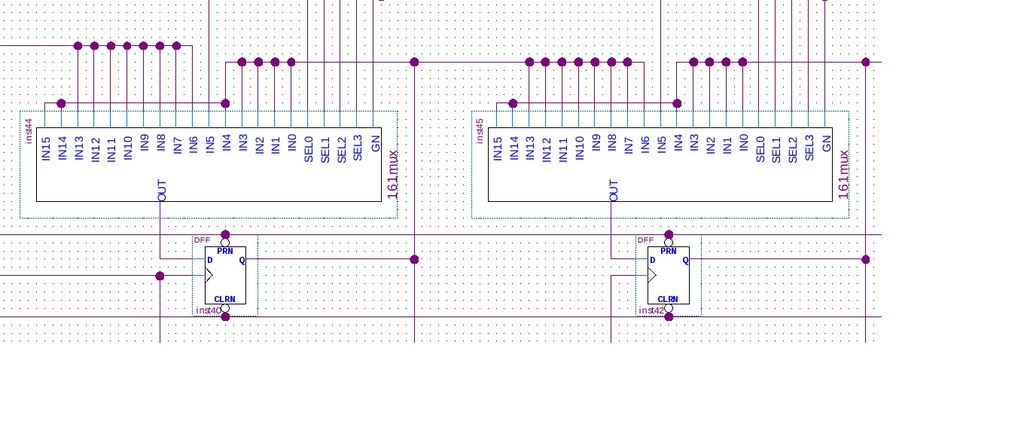

1)添加8個16輸入MUX(161MUX)。

a)展開默認庫下的other文件夾。 b)展開maxplus2 .c)添加16輸入多路復用器。2)將8個MUX排列成兩行,每行四長。它們應該在state_machine的右側(因此也應該在clock_generator的右側)。如果它們稍微低于state_machine,則更容易。

a)MUX需要旋轉,以使一個輸出朝下。 b)每個MUX水平之間留出1塊空間,并且3-4兩行之間垂直分隔。

每組4個MUX接受輸入。我們發送到選擇輸入的信號決定哪個信號將出現在輸出上。

3)從左到右標記頂部的MUX RegA3-RegA0,指示數字A的位3位0。

4 )標記底部的MUX RegB3-RegB0。

參見圖片

5)添加8個D型觸發器。

a)每個MUX下方應放置一個觸發器。

D型觸發器有助于將MUX放在時鐘上。 MUX選擇的任何信號都將按其方式發送,但是通過添加觸發器,它只會在時鐘信號到來時發送。

6)加4 7_segment_display。

a)所有四個將被發送。在MUX的右側,它們與MUX之間大約有3個空間。

b)四個中的兩個將位于MUX的上方,但仍保留在MUX的右側。c)其中一個7_segment_displays將位于兩組MUX之間。

d)最后一個將位于底部的MUX組之下。

7_segment_displays將幫助我們了解電路中正在發生的事情。一個讓我們看看將要輸入的數字。另一個告訴我們狀態機在哪里,只有3個D觸發器,選擇范圍是0到7。該組的最后兩個顯示只是為了確保電路正常工作。 MUX和D觸發器用作移位器。如果信號正確,則來自一個MUX的信號將被發送到右側的MUX。稍后,這還將最右邊的位移入加法器。 7_segment_displays會告訴我們每組MUX發出了什么信號。這可以用來解決任何問題。

e)將頂部7_segment_display標記為Number。將第二個顯示器標記為StateMachine。

g)將第三個顯示器標記為RegA。

h)將第四個顯示器標記為RegB。

參見圖片

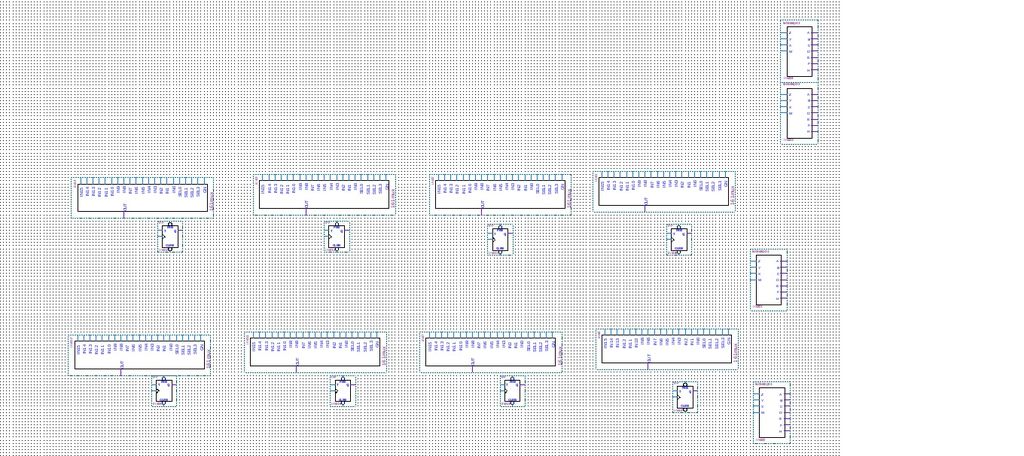

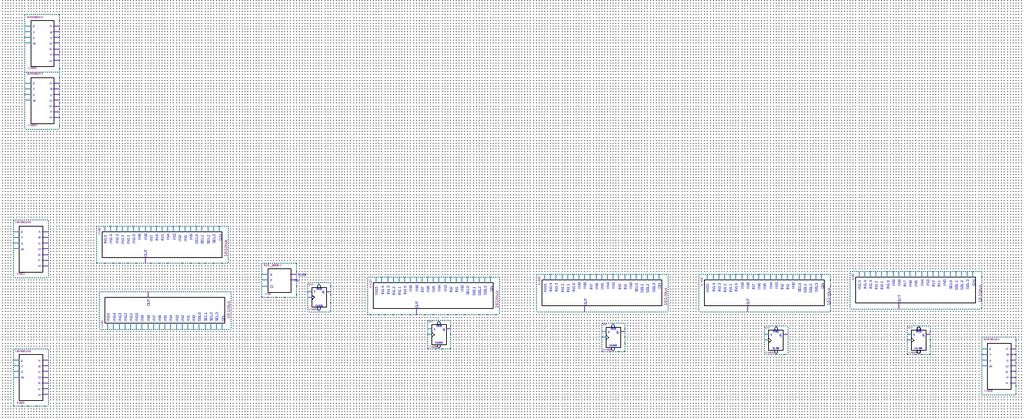

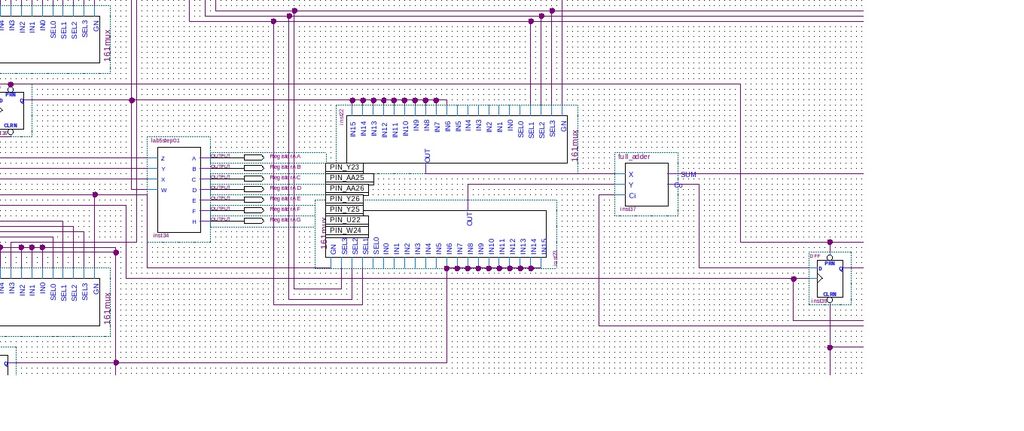

7)再添加兩個兩個16輸入MUX,一個在另一個之上,頂部的輸出朝下,底部的輸出朝上。 )這些MUX應該在右側,并且大約在其他MUX組之間。 (對于頂部MUX組,這些MUX也在7_segment屏幕的右側。標記頂部MUX AddBitA。標記底部MUX AddBitB。

8)將full_adder添加到

9)在full_adder的右邊添加一個D觸發器,將其放低大約一半。

10)將4個16輸入MUX添加到T觸發器的右側。在每個組件之間保留1塊空間。

a)從左到右標記MUX RegC3-RegC0。

11)在每個MUX下方添加4個D觸發器。

12)在右側添加7_segment_display

請參見2圖片

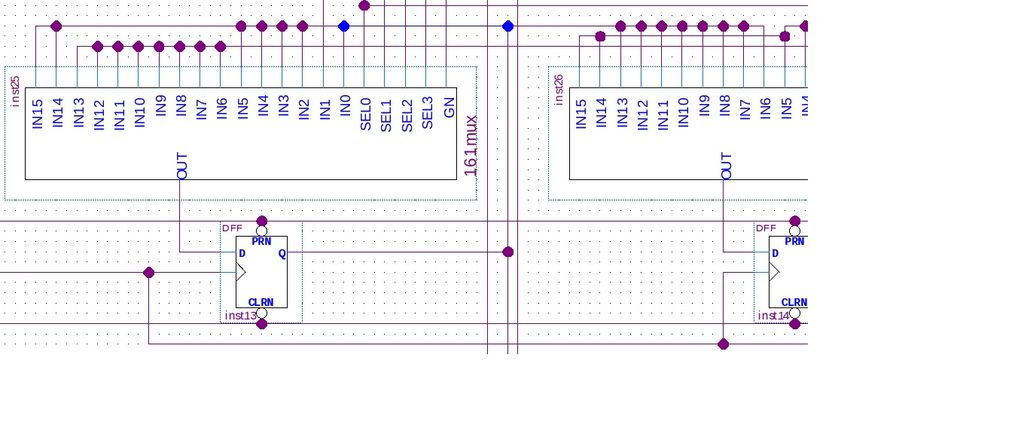

13)將state_machine的輸出Q1連接到每個MUX的SEL1。

14)將state_machine的輸出Q1連接到7_segment_display標記為StateMachine的輸入Z

15)將狀態機的輸出Q2連接到每個MUX的SEL2。

16)將狀態機的輸出Q2連接到標記為StateMachine的7_segment_display的輸入Y。

17)將狀態機的輸出Q3連接到每個MUX的SEL3。

18)將state_machine的輸出Q3連接到標有StateMachine的7_segment_display的輸入X。

19)將每個MUX的輸出連接至其下面的D觸發器的D輸入。 》 20)標有AddBitA和AddBitB的MUX的輸出應連接到full_adder的X和Y(一個輸出到一個輸入)。

21)連接D的Q輸出RegA3 MUX下方的觸發器連接到RegA3 MUX的輸入IN0,IN2-IN5,IN14和IN15。

22)還將相同的Q輸出連接到RegA2 MUX的輸入IN6-IN13。

23)重復步驟每個RegA2-RegA0下方的D觸發器的16和17。

a)RegA2-RegA0的D觸發器的Q輸出始終連接到其上方和右側的寄存器的相同輸入。類似于RegA3。b)對于RegA0下面的D觸發器的第17步,Q連接到RegA3的輸入IN6-IN13。

參見圖片

24)在RegA3下面的D觸發器的Q輸出連接。到RegA 7_segment_decoder的輸入W。

25)將RegA2下方的D觸發器的Q輸出連接到RegA的輸入X。

26)將RegA1下方的D觸發器的Q輸出連接到RegA1的輸入Y。 。

27)將RegA0下方的D觸發器的Q輸出連接到RegA的輸入Z。

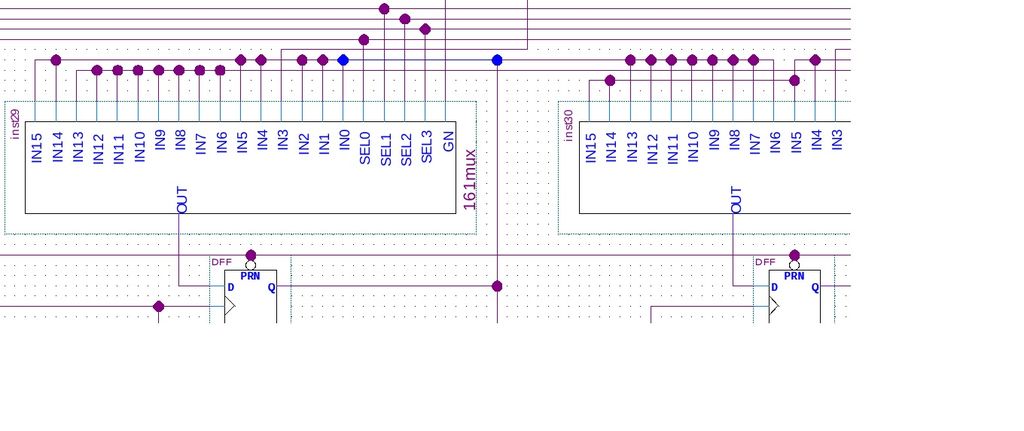

28)將RegB3 MUX下方的D觸發器的Q輸出連接到輸入IN0-IN2,IN4,IN5, RegB3 MUX的IN14和IN15。

29)將相同的輸出Q連接到輸入IN6- RegB2 MUX的IN13。

30)對RegB2-RegB0以下的D觸發器重復步驟23和24。a)RegB2-RegB0的D觸發器的Q輸出始終連接到寄存器的相同輸入b)對于RegB0下面的D觸發器的第24步,Q連接到RegB3的輸入IN6-IN13。

參見圖片

31)連接在RegB3之下的D觸發器的輸出Q到RegB 7_segment_decoder的輸入W。

32)在RegB2之下的D觸發器的輸出Q連接到RegB2的輸入X。

33)將D觸發器的輸出Q連接到

34)將RegB0下方的D觸發器的輸出Q連接到RegB0的輸入Z。

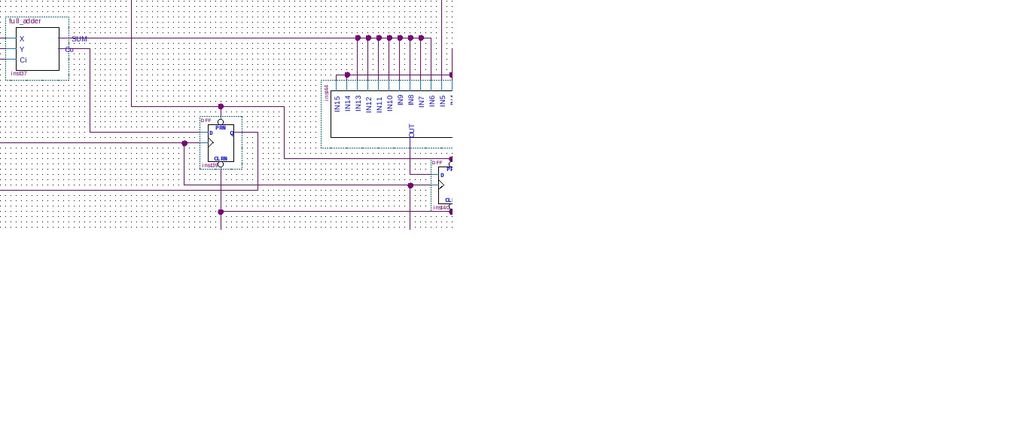

35)將RegC3 MUX下方的D觸發器的Q輸出連接到Reg0的輸入Z。 RegC3 MUX的IN4,IN14和IN15。

36)將D觸發器的相同Q輸出連接到RegC2的輸入IN6-IN13。

37)對RegC2下面的每個D觸發器重復步驟30和31。 -RegC0。

a)RegC2-RegC0的D觸發器的Q輸出始終連接到就像RegC3一樣,位于寄存器上方和右側的寄存器的輸入相同。

b)RegC0的D觸發器的Q輸出未連接到RegC3的任何輸入。

請參見圖片

38)將RegC3下方的D觸發器的輸出Q連接到RegC 7_segment_Decoder的輸入W。

39)將RegC2下方的D觸發器的輸出Q連接到RegC2的輸入X。

40)將RegC2下方的D觸發器的輸出Q連接到RegC。 RegC1之下的D觸發器到RegC的輸入Y。

41)RegC0之下的D觸發器的輸出Q連接到RegC0的輸入Z。

42)RegA0之下的D觸發器的輸出Q連接到RegC0的輸入到IN6。 AddBitA MUX的-IN15。

43)將RegB0下面的D觸發器的輸出Q連接到AddBitB MUX的輸入IN6-IN15。

注意:這兩個MUX的其余輸入和SEL0將保留。懸空。這可能會在某些電路中引起問題,但不適用于此電路。請注意,如果確實引起問題,則將輸入連接到VCC或GND通常可以解決問題。 VCC類似于1,GND類似于0。

請參見圖片《44》將full_adder的輸出Sum連接到RegC3 MUX的輸入IN6-IN13。

45)將full_adder的輸出Co連接到RegC3 MUX的D輸入。 D觸發器在其右側。

46)將D觸發器的Q輸出連接至full_adder的輸入Ci。

請參見圖片

47)在您所有的左側添加3個輸入引腳

48)將輸入標記在clock_generator時鐘的左側。

49)將其連接到clock_generator的輸入。

br》 50)將clock_generator的輸出連接到每個D觸發器的時鐘輸入。

51)將相同的輸出連接到state_machine的時鐘輸入。

52)在其左側標記一個輸入引腳state_machine Control。

53)將Control連接到state_machine的輸入標簽控件。

54)將第三個輸入引腳標記為Clear。

55)將Clear連接到state_machine的clear輸入。

56 )連接相同的清除每個D觸發器的CLRN的輸入引腳。

57)在RegA3 MUX上方添加6個輸入引腳。

58)標記第一個輸入引腳LoadA。

59)將LoadA連接到RegA3-RegA0的SEL0。

60)將第二個輸入引腳標記為Bit3。

61)將Bit3連接到RegA3的IN1,RegB3的IN3,RegC3的IN5,以及標記為Number的7_segment_display的輸入W。

62)標記第三個輸入引腳Bit2。

63)將Bit2連接到RegA2的IN1,RegB2的IN3,RegC2的IN5,以及標記為Number的7_segment_display的輸入X。

64)標記第四個輸入引腳Bit1。

65)連接RegA1的位1到IN1,RegB1的IN3,RegC1的IN5和標有編號的7_segment_display的輸入Y。

66)標記第五個輸入引腳Bit0。

67)將Bit0連接到RegA0的IN1,IN3 RegB0,RegC0的IN5和標記為Number的7_segment_display的輸入Z。

68)標記第六個輸入引腳Gn。

69)將Gn連接到每個MUX的輸入GN。

70)添加輸入銷到RegB3 MUX的左側。

71)將其標記為LoadB。

72)將LoadB連接到RegB3-R的SEL0 egB0。

73)在RegC3 MUX的左側添加一個輸入引腳。

74)在引腳C上標記負載C.

75)將LoadC連接到RegC3-RegC0的SEL0。

76)添加7個輸出標記為Number的7_segment_display右側的引腳。

77)標記輸出InputA-InputG。

78)將Number的輸出AG連接到其相應的輸出引腳。

79)在右側添加7個輸出引腳of 7_segment_display StateMachine。

80)在輸出上標記StateMachineA-StateMachineG。

81)將StateMachine的輸出AG連接到其相應的輸出引腳。

參見圖片

82)在7的右側添加7個輸出引腳。 7_segment_display RegA。

83)標記輸出RegAA-RegAG。

84)將RegA的輸出AG連接到其相應的輸出引腳。

85)在7_segment_display RegB的右側添加7個輸出引腳。 》 86)將輸出RegBA-RegBG標記。

87)將RegB的輸出AG連接到其相應的輸出引腳。

88)在7_segment_display RegC的右側添加7個輸出引腳。

89)標記輸出SumA-SumG。

90)將RegC的輸出AG連接到其相應的輸出引腳。

請參見圖片

91)保存文件。

92)單擊“處理”。

93)轉到“開始編譯”(此處將花費幾分鐘。)

程序可能會出現一些警告,但我們的電路仍應正確加載到FPGA。

參見圖片

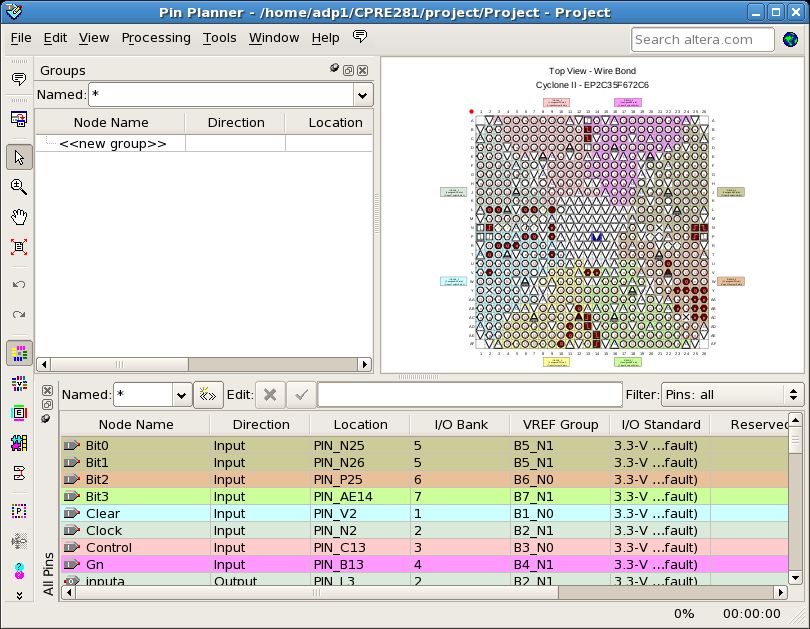

步驟7:引腳分配

由于完成了項目電路,因此需要將輸入和輸出引腳分配給FPGA板上的開關和LED。這將是測試電路是否正常的測試。

1)單擊“ Assignments”。

2)進入“ Pin Planner”。

將出現一個新窗口,其中包含您輸入的所有輸入和輸出引腳。

請參見圖片

3)拿起FPGA手冊或在Google上查找設備的引腳分配。

引腳分配應通過所有開關,LED,按鈕和7段顯示器。每個位置將在同一行中給出。 (例如:PIN_N25)

4)在引腳規劃器上找到Bit0-Bit3(應按字母順序)。

5)選擇要為每個引腳使用的開關(我對bit0-使用了switch0-switch3分別為Bit3)

6)在您的手冊中找到要使用的開關并找到其位置ID。

7)在引腳規劃器中,單擊位置框,然后使用下拉菜單選擇

8)對于您的輸出,請確保該引腳對應于7段顯示器的正確段。

9)輸入Clock應該連接到內部時鐘源。請確保使用可與clock_generator正確縮放的適配器。

注意:確保輸入引腳僅是開關和按鈕。我們所有的輸出應該是7段顯示器。

這里是您可以做的一個例子。

?Bit0-Bit3的Switch0-3。

?LoadA

的開關4? LoadB

?LoadC

的開關6?Control

的開關7?Gn

的開關8?Clear的開關17(由于它會復位整個電路,因此我們嘗試使其遠離開關我們會更定期地移動)

?輸入A-InputG的HEX7

?StateMachineA-StateMachineG 的HEX5?RegAA-RegAG

HEX3?RegBA-RegBG

HEX2?SumA的HEX0

責任編輯:wv

-

加法器

+關注

關注

6文章

183瀏覽量

30425 -

quartus

+關注

關注

17文章

171瀏覽量

74945

發布評論請先 登錄

相關推薦

評論