第1步:材料

完成此項(xiàng)目您將需要:

硬件

-任何具有HDMI和以太網(wǎng)的ZYNQ板都可以正常工作/我正在使用Digilent Zybo

-USB A到micro B USB電纜

-HDMI電纜

-以太網(wǎng)電纜

-帶有HDMI輸入的顯示器

軟件

-Xilinx Vivado

-Xilinx SDK

步驟2:輸出-VGA控制器第1部分

我們將使用開發(fā)板上的HDMI端口輸出視覺數(shù)據(jù)。 HDMI端口連接到ZYNQ的PL(可編程邏輯= FPGA)端,我們將需要為其設(shè)計(jì)VHDL控制器。如果您曾經(jīng)設(shè)計(jì)過VGA控制器,您會(huì)發(fā)現(xiàn)它非常相似。 HDMI和VGA的時(shí)序?qū)嶋H上是相同的,實(shí)際上您可以在現(xiàn)有的VGA控制器上構(gòu)建以獲得HDMI控制器。

為更好地了解實(shí)際情況,我們將首先設(shè)計(jì)一個(gè)VGA控制器

我們要以1920x1080的分辨率顯示。

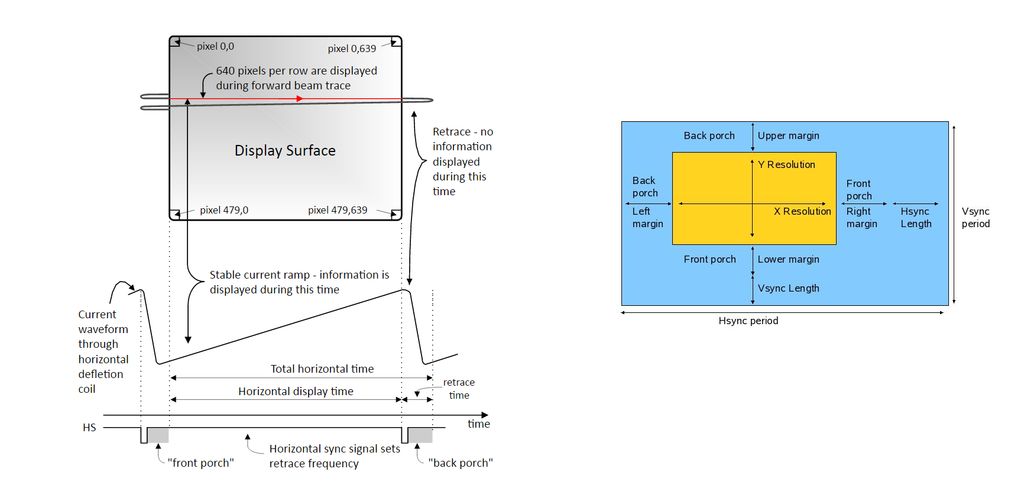

VGA控制器負(fù)責(zé)將像素?cái)?shù)據(jù)(RGB格式)依次逐像素傳輸?shù)斤@示器。在1920x1080的實(shí)際顯示區(qū)域之外,還有一些“邊界”區(qū)域,即:前沿,后沿和回掃。這些區(qū)域的像素大小是標(biāo)準(zhǔn)的,并針對(duì)每種分辨率。這些區(qū)域?qū)嶋H上并沒有出現(xiàn)在屏幕上,但是它們是必需的,并且該區(qū)域中像素的顏色必須為黑色。一個(gè)有效的問題是,為什么需要這些額外的區(qū)域。這個(gè)問題違背了這個(gè)可指導(dǎo)性的目的,但是如果您好奇的話,我鼓勵(lì)您在線進(jìn)行進(jìn)一步研究。

這是一個(gè)很好的視頻,解釋了VGA接口https://goo.gl/vfSw6o

在我們的情況下,我們希望以1920 * 1080的分辨率進(jìn)行顯示,這些時(shí)間是:

水平顯示區(qū)域= 1920像素

水平Fron門廊= 88像素

水平后沿= 148像素

水平回掃= 44像素

垂直顯示區(qū)域= 1080像素

垂直前沿= 4像素

垂直后沿= 36像素

垂直回掃= 5像素

(您可以在此處找到其他分辨率的時(shí)間http://goo。 gl/hFNRVb)

因此,我們的實(shí)際分辨率為2200 x1125。我們希望60 fps(每秒幀數(shù)),因此我們的像素時(shí)鐘將為60 * 2200 * 1125 = 148.5 MHz。在Zybo板上,提供了125 Mhz的時(shí)鐘。我們將使用MMCM IP生成所需的148.5 MHz像素時(shí)鐘。

步驟3:輸出-VGA控制器第2部分

《在上一步的理論背景下,您應(yīng)該可以設(shè)計(jì)自己的VGA控制器。我將為您提供一個(gè)Vivado項(xiàng)目,但我建議您至少嘗試自己嘗試一下。

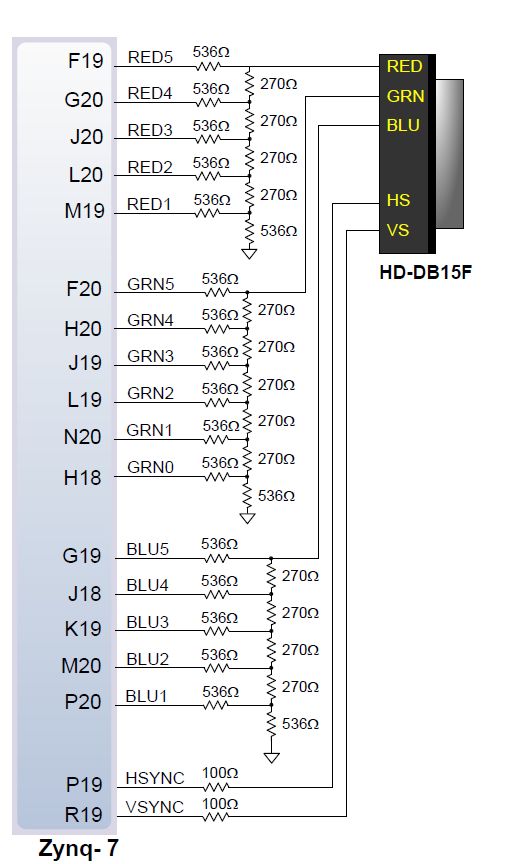

大多數(shù)VGA端口不會(huì)為每個(gè)像素的每個(gè)顏色通道提供8位(參見上圖),因此您需要使設(shè)計(jì)適應(yīng)開發(fā)板提供的每種顏色的引腳數(shù)(盡管這對(duì)于HDMI來說不是問題)。

設(shè)計(jì)會(huì)將整個(gè)屏幕涂成藍(lán)色,除了左上方的像素將變?yōu)榧t色。應(yīng)當(dāng)指出,該項(xiàng)目使用了ZYBO董事會(huì)的約束條件。因此,如果要在另一個(gè)開發(fā)板上運(yùn)行該項(xiàng)目,則應(yīng)更新約束文件并調(diào)整每種顏色的引腳數(shù)。

請(qǐng)看圖nr。 2.請(qǐng)記住,盡管我們的VGA控制器在每種顏色下輸出5/6位,但是在通過電纜之前,這些位會(huì)針對(duì)每種顏色通道(紅色,綠色和藍(lán)色)轉(zhuǎn)換為一個(gè)模擬信號(hào)。

第4步:輸出-HDMI控制器第1部分

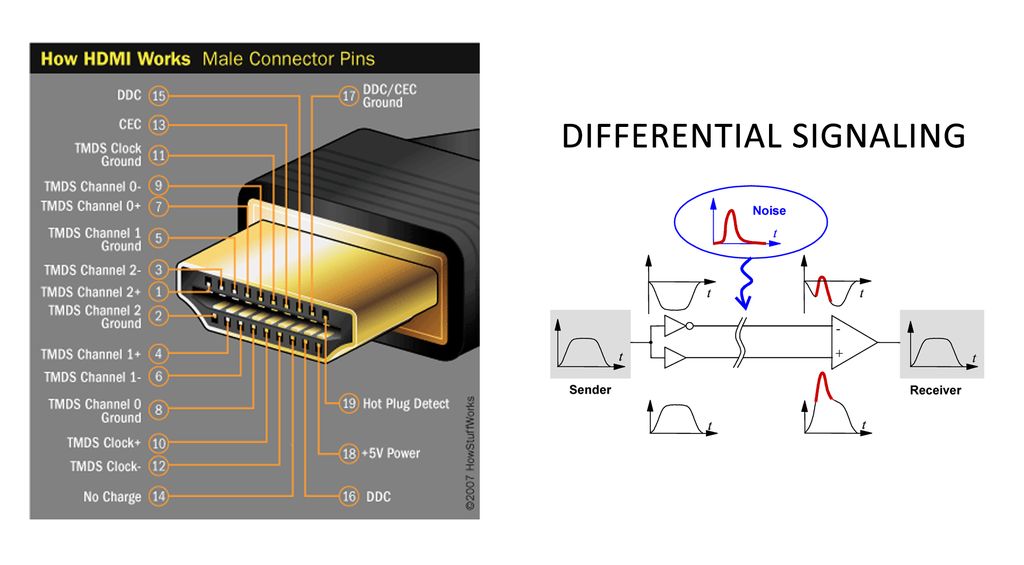

現(xiàn)在,我們知道了VGA控制器的工作原理,并且我們有一個(gè)可行的設(shè)計(jì),我們可以繼續(xù)使用HDMI控制器。 HDMI控制器實(shí)際上將使用我們?cè)赩GA控制器中開發(fā)的所有代碼。 HDMI和VGA使用相同的時(shí)序和相同的信號(hào)。差異出現(xiàn)在輸出引腳上。

雖然VGA每種顏色使用一根線并傳輸一條模擬信號(hào),但HDMI每次每種顏色以1位數(shù)字方式傳輸數(shù)據(jù)并使用差分信號(hào)。差分信號(hào)意味著HDMI的每一位都有2個(gè)引腳,而另一個(gè)則相反。因此,如果我們要傳輸信號(hào)“ 1”,我們將在一根線上傳輸“ 1”,而在另一根線上傳輸“ 1”。這樣可以確保信號(hào)的完整性,您可以在https://goo.gl/6CPCzB上了解更多信息。對(duì)于每種顏色(紅色,綠色和藍(lán)色),我們都有一個(gè)通道,對(duì)于時(shí)鐘,我們有一個(gè)通道。由于差分信號(hào)的特殊性,我們通過HDMI發(fā)送的信號(hào)必須經(jīng)過DC平衡處理,這意味著1和0的數(shù)量必須在特定的時(shí)間范圍內(nèi)大致相等。為了實(shí)現(xiàn)這一點(diǎn),我們將使用8b/10b編碼。您可以從DVI規(guī)范(http://goo.gl/hhh8Ge,DVI和HDMI使用相同的視頻信號(hào))上了解很多有關(guān)差分信號(hào)和8b/10b編碼的工作原理。

第5步:輸出-HDMI控制器第2部分

足夠的理論,讓我們進(jìn)入我們的項(xiàng)目。在VGA控制器中,我們獲得了148.5 MHz的時(shí)鐘,但是在這里,我們將不得不提供10倍的頻率,因?yàn)槲覀円獮槊糠N顏色傳輸8位,并使用8b/10b編碼轉(zhuǎn)換為每個(gè)像素10位和10 * 148.5MHz = 1485MHz。這是Zybo板上無法獲得的巨大頻率。幸運(yùn)的是,我們掌握了一些技巧。我們可以管理5 * 148.5MHz = 742.5MHz,我們將使用OSERDES(串行器)IP在742.5Mhz時(shí)鐘的上升沿和下降沿都傳輸數(shù)據(jù),因此實(shí)際上我們將以1485MHz傳輸數(shù)據(jù)。 Vivado會(huì)給我們一些時(shí)間警告,您可以始終使用較小的時(shí)鐘來獲得較低的分辨率,但是由于它可以正常工作,因此我們暫時(shí)不介意(警告與時(shí)鐘緩沖區(qū)未正式存在有關(guān)

因此,我們需要做的是將來自VGA控制器輸出的數(shù)據(jù)編碼為8b/10b格式,然后如上所述進(jìn)行序列化。我們還需要在項(xiàng)目中添加另一個(gè)MMCM,以生成用于序列化的742.5MHz時(shí)鐘。

我在編碼器和序列化器的vhdl文件下面附加了該文件。您必須首先對(duì)RGB通道進(jìn)行編碼,然后對(duì)其進(jìn)行序列化。

紅色通道示例:

TMDS_encoder_RED:TMDS_encoder

端口圖(clk148,red_channel_8bits,c_red,video_on ,encode_red_10bits);

Serialiser_RED:Serialiser10_1

端口映射(clk148,clk742,encoded_red_10bits,重置,red_serial_1bit);

TMDS_encoder的“ c”輸入是紅色和綠色的“ 00”,藍(lán)色是“ vsync&hsync”(這是DVI規(guī)范http://goo.gl/hhh8Ge)。

步驟6:從RAM顯示圖像

HDMI控制器的目的是顯示處理后的圖像。現(xiàn)在,在實(shí)現(xiàn)控制器并準(zhǔn)備就緒后,我們應(yīng)該考慮為該控制器提供數(shù)據(jù)。鑒于很多圖像增強(qiáng)過程將在PS中進(jìn)行(處理系統(tǒng)= ARM處理器),并且生成的圖像將駐留在DDR RAM中。因此,我們需要一種從RAM到HDMI控制器獲取數(shù)據(jù)的方法。

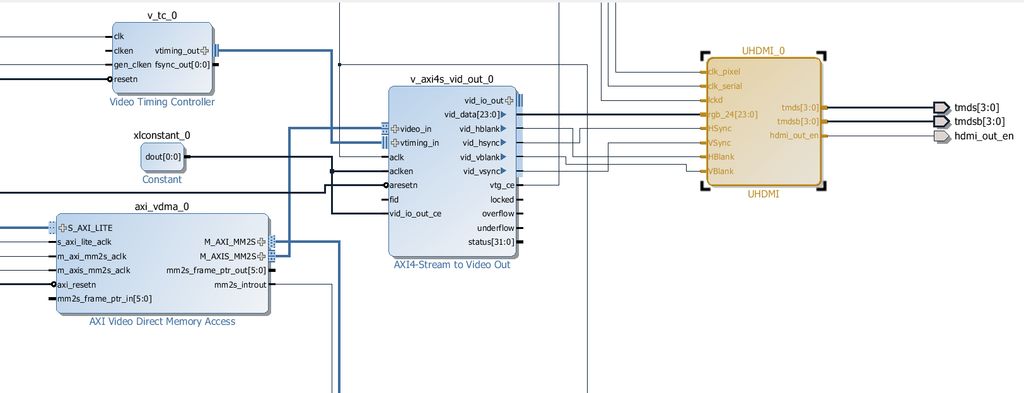

要實(shí)現(xiàn)此目的,您需要3個(gè)IP:

1)VDMA(視頻直接內(nèi)存訪問) )

2)VTC(視頻定時(shí)控制器)

3)流到視頻輸出(從現(xiàn)在開始我們將其稱為S2VO)

S2VO實(shí)際上將提供輸出的RGB 24BIT信號(hào)以及所需的HSYNC和VSYNC信號(hào)。因此,我們可以省去HDMI控制器的那一部分。

您應(yīng)該將這些IP添加到設(shè)計(jì)中,進(jìn)行配置并進(jìn)行正確的連接。

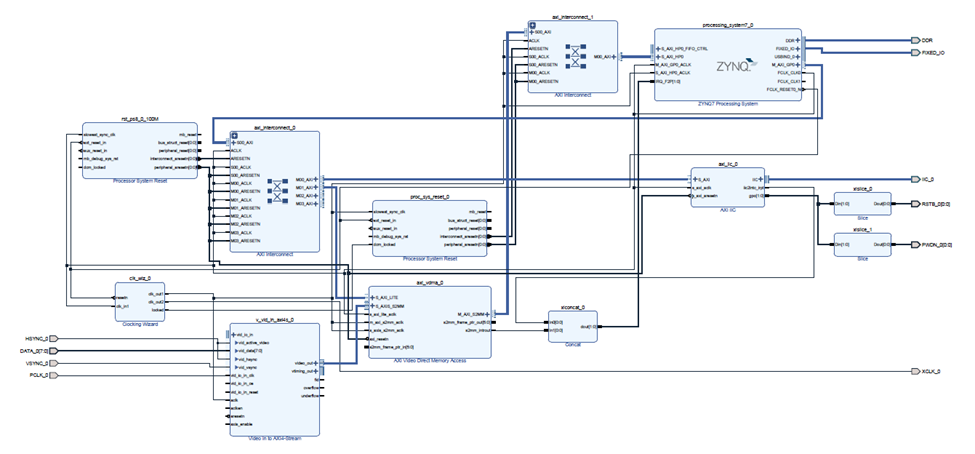

最后,您應(yīng)該得到類似于

步驟7:輸出-SDK END

所有硬件均已設(shè)置好并準(zhǔn)備就緒,我們現(xiàn)在必須在PS中構(gòu)建軟件。我們將導(dǎo)出硬件和比特流并啟動(dòng)SDK。

1)文件-》導(dǎo)出-》導(dǎo)出硬件-》選中包括比特流,然后按確定

2)文件-》啟動(dòng)SDK

在SDK中創(chuàng)建一個(gè)新的應(yīng)用程序項(xiàng)目。

3)文件-》新建-》應(yīng)用程序項(xiàng)目

4)為您的項(xiàng)目選擇一個(gè)名稱,然后按下一步

5)選擇“ Hello World”模板然后按Finish

SDK中的應(yīng)用程序?qū)⑿枰獙?duì)VDMA進(jìn)行編程。為了完成此操作,使用了一些標(biāo)準(zhǔn)功能(我會(huì)在有空的時(shí)候進(jìn)行詳細(xì)介紹)。

為了測(cè)試我們的設(shè)計(jì),我們將使用SDK Restore(Xilinx工具-》轉(zhuǎn)儲(chǔ)/還原) )功能可將圖像放入DDR RAM內(nèi)存并使用我們的HDMI控制器顯示。您可以將圖像加載到所需的任何位置(內(nèi)存開頭的一些較小的受限區(qū)域除外)。在我們的示例中,我們選擇了地址16777216,文件大小為8294400 = 1920 * 1080 * 4(4個(gè)通道= RGB + alpha)。

責(zé)任編輯:wv

-

HDMI

+關(guān)注

關(guān)注

32文章

1734瀏覽量

152212 -

usb

+關(guān)注

關(guān)注

60文章

7978瀏覽量

265548

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

傅立葉變換在圖像處理中的作用

【每天學(xué)點(diǎn)AI】實(shí)戰(zhàn)圖像增強(qiáng)技術(shù)在人工智能圖像處理中的應(yīng)用

基于差分卷積神經(jīng)網(wǎng)絡(luò)的低照度車牌圖像增強(qiáng)網(wǎng)絡(luò)

如何構(gòu)建物聯(lián)網(wǎng)系統(tǒng)

圖像采集卡:增強(qiáng)視覺數(shù)據(jù)采集

基于VDMA的遠(yuǎn)程圖像采集系統(tǒng)參考設(shè)計(jì)

正點(diǎn)原子ZYNQ7015開發(fā)板!ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2,性能強(qiáng)悍,資料豐富!

[XILINX] 正點(diǎn)原子ZYNQ7035/7045/7100開發(fā)板發(fā)布、ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

Cricket XL全新亮相:革新圖像增強(qiáng)技術(shù)的解決方案

基于 ZYNQ AlphaGo 的棋類人機(jī)博弈 AR 系統(tǒng)

圖像邊緣檢測(cè)系統(tǒng)的設(shè)計(jì)流程

鴻蒙OpenHarmony開發(fā):【編譯構(gòu)建指導(dǎo)】

如何構(gòu)建Zynq圖像增強(qiáng)系統(tǒng)

如何構(gòu)建Zynq圖像增強(qiáng)系統(tǒng)

評(píng)論