在當(dāng)前雖然在嵌入式系統(tǒng)中有許多連接元件的方法,但最主要的還是以太網(wǎng)、PCI Express和RapidIO這三種高速串行標(biāo)準(zhǔn)。所有這三種標(biāo)準(zhǔn)都使用相似的串行解串器(SerDes)技術(shù),它們提供的吞吐量和時延性能都要超過寬的并行總線技術(shù)。隨著這些標(biāo)準(zhǔn)的不斷發(fā)展,今后的趨勢將是采用通用SerDes技術(shù)。這意味著這些協(xié)議提供的原始帶寬不會有明顯的差異。相反,每種協(xié)議的用途將取決于如何使用帶寬。LinkedIn串行總線的發(fā)展一共目前可以總結(jié)分為 3 個環(huán)節(jié)時期:

時鐘并行總線:小于 200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC

源同步時鐘并行總線:小于 3200Mbps,比如 DDRr1234 系列,MII,EMMC

高速串行總線:最高有 56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4

那么對于這些信號的重要線信號的處理我們在設(shè)計過程中注意以下幾點:

差分走線,信號換層過孔數(shù)量,等長長度把控,阻抗控制要求,跨分割的損耗,走線拐角的位置形狀,繞線方式對應(yīng)的插損和回?fù)p,布局不妥當(dāng)造成的一系列串?dāng)_和疊層串?dāng)_,布局不恰當(dāng)操作焊盤存在的stub。

1. 差分走線,差分走線嚴(yán)格按照差分仿真所得出的結(jié)論,2S,和 3W 的要求進(jìn)行把控走線,其目的在于增強信號質(zhì)量的耦合性能,減少信號的回?fù)p

2. 信號層走線過孔數(shù)量,對于重要的信號線而言這里簡直就是致命的傷害,特別是高速信號頻率很高的信號線,過孔數(shù)量一旦過多,就會造成回?fù)p的加劇,所以打孔不是遇到線就打孔,尤其是我們的時鐘線。

3. 等長長度把控

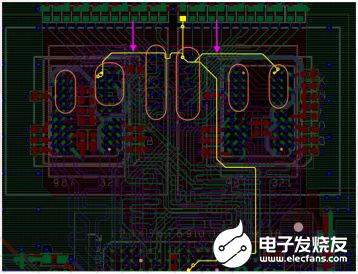

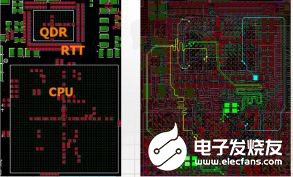

按照對應(yīng)的器件的等長要求,進(jìn)行數(shù)據(jù)的線段匹配長度一致,從而保證數(shù)據(jù)傳輸?shù)姆€(wěn)定和數(shù)據(jù)文件傳輸時序上的同步。

4. 跨分割的損耗。重要線段不能跨分割走線,以免我們的信號會出現(xiàn)回?fù)p和插損的產(chǎn)生

5. 信號線的布局盡量不要出現(xiàn) stub 布局出現(xiàn),如圖所示

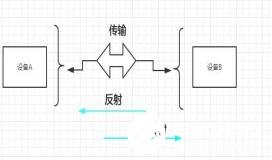

6. 走線直角和倒角和圓弧到底哪個好

通過仿真,其實圓弧走線是最好的,信號沒有 reflect 反射,倒角多多少少會有,但是反射沒有直角來的明顯,當(dāng)我們設(shè)備 A 傳輸?shù)皆O(shè)備 B 其自然而然的就會有信號在傳輸過程中存在反射回來我們的設(shè)備A,當(dāng)我們的設(shè)備 B 傳輸?shù)皆O(shè)備 A,同樣因為直角的反射,會有信號回到我們的設(shè)備 B 中。

責(zé)任編輯:gt

-

嵌入式

+關(guān)注

關(guān)注

5089文章

19170瀏覽量

306812 -

帶寬

+關(guān)注

關(guān)注

3文章

952瀏覽量

41016 -

總線

+關(guān)注

關(guān)注

10文章

2899瀏覽量

88277

發(fā)布評論請先 登錄

相關(guān)推薦

在設(shè)計過程中對于高速串行總線的注意事項有哪幾點

在設(shè)計過程中對于高速串行總線的注意事項有哪幾點

評論